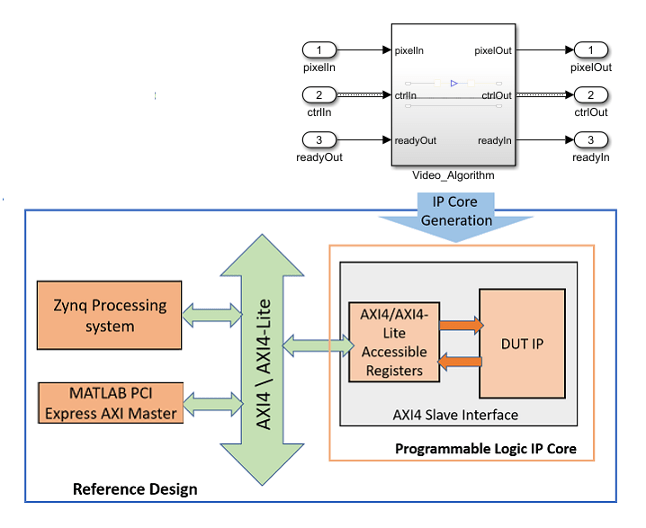

Можно задать несколько Основных интерфейсов AXI в пользовательском исходном проекте и получить доступ к ведомым интерфейсам AXI4 в сгенерированном HDL ядро IP DUT для DUT. Эта возможность позволяет вам одновременно соединить HDL ядро IP DUT с двумя или больше Основными IP AXI в исходном проекте, таком как Ведущий IP HDL Verifier™ JTAG AXI и ARM® процессор в Zynq® система обработки.

Чтобы задать несколько Основных интерфейсов AXI, вы задаете BaseAddressSpace и MasterAddressSpace для каждого Основного экземпляра AXI, и также IDWidth свойство.

IDWidth ширина всех сигналов ID, таких как AWID, WID, ARID, и RIDВ виде положительного целого числа. По умолчанию, IDWidth 12, который позволяет вам задать одну связь интерфейса AXI Master с ядром IP DUT. Чтобы соединить ядро IP DUT с несколькими Основными интерфейсами AXI, вам, вероятно, придется увеличить IDWidth. IDWidth значение специфично для инструмента. Чтобы видеть значение, которое необходимо использовать при определении больше чем одного интерфейса AXI Master, обратитесь к документации для того инструмента. Если вы используете неправильную ширину ID, инструмент синтеза генерирует ошибку и сообщает о правильном IDWidth то, что необходимо использовать.

Этот код является синтаксисом для MasterAddressSpace поле при определении нескольких Ведущего устройства AXI взаимодействует через интерфейс в Vivado®- основанные исходные проекты:

'MasterAddressSpace', ...

{'AXI Master Instance Name1/Address Space of Instance Name1', ...

'AXI Master Instance Name2/Address_Space of Instance Name2',...};Например, этот код иллюстрирует, как можно изменить plugin_rd файл, чтобы задать два Основных интерфейса AXI.

% ... %% Add custom design files % add custom Vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); % ... % ... % The DUT IP core in this reference design is connected % to both Zynq Processing System and the MATLAB as AXI % Master IP. Because of 2 AXI Master, ID width % has to be increased from 12 to 13. hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', 'axi_interconnect_0/M00_AXI', ... 'BaseAddress', {'0x40010000', '0x40010000'}, ... 'MasterAddressSpace', {'processing_system7_0/Data', 'hdlverifier_axi_master_0/axi4m'}, ... 'IDWidth', 13); % ...

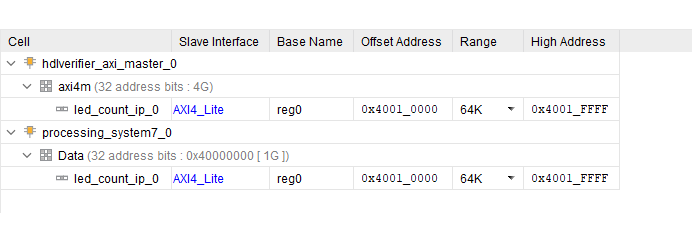

В этом примере два Основных IP AXI являются HDL Verifier MATLAB как Ведущий IP AXI и процессор ARM. На основе синтаксиса MasterAddressSpace, для HDL Verifier MATLAB как ведущий IP AXI, AXI Master Instance Name hdlverifier_axi_master_0 и Address_Space of Instance Name axi4m.

Ведомые интерфейсы AXI4 в HDL ядро IP DUT соединяются с Xilinx® Соединительный IP AXI, который задан InterfaceConnection свойство addAXI4SlaveInterface метод. Ведомые интерфейсы AXI4 имеют BaseAddress. Этот BaseAddress должен сопоставить с MasterAddressSpace для двух Основных IP AXI, которые заданы как массив ячеек из символьных векторов.

Необходимо убедиться, что Основной дюйм/с AXI был уже включен в проект исходного проекта Vivado. system_top.tcl файл TCL, который задан CustomBlockDesignTcl свойство addCustomVivadoDesign метод. В этом файле TCL необходимо убедиться, что два Основных IP AXI соединяются с тем же Соединительным IP AXI Xilinx. Межсоединения затем соединяют Основного дюйм/с AXI с ведомыми интерфейсами AXI4 в ядре IP HDL.

После того, как вы запускаете IP Core Generation рабочий процесс и создает проект Vivado, открывает проект. В проекте Vivado, если вы открываете блочную конструкцию, вы видите два Основных IP AXI, соединенные с HDL ядро IP DUT. Если вы выбираете вкладку Address Editor, вы видите Основные имена экземпляра AXI и соответствующие адресные пространства.

Чтобы задать несколько Основных интерфейсов AXI, вы задаете InterfaceConnection и BaseAddressSpace для каждого Основного экземпляра AXI, и также IDWidth свойство. Этот код является синтаксисом для InterfaceConnection поле при определении нескольких Ведущего устройства AXI взаимодействует через интерфейс в исходных проектах Qsys™-based:

'InterfaceConnection', ...

{'AXI Master Instance Name1/Port name of Instance Name1', ...

'AXI Master Instance Name2/Port name of Instance Name1', ...};Например, этот код иллюстрирует, как можно изменить plugin_rd файл, чтобы задать три Основных интерфейса AXI.

% ... %% Add custom design files % add custom Qsys design hRD.addCustomQsysDesign('CustomQsysPrjFile', 'system_soc.qsys'); hRD.CustomConstraints = {'system_soc.sdc','system_setup.tcl'}; % ... % add AXI4 slave interfaces hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', {'hps_0.h2f_axi_master','master_0.master','MATLAB_as_AXI_Master_0.axm_m0'}, ... 'BaseAddress', {'0x0000_0000','0x0000_0000','0x0000_0000'},... 'InterfaceType', 'AXI4'... 'IDWidth', 14); % ...

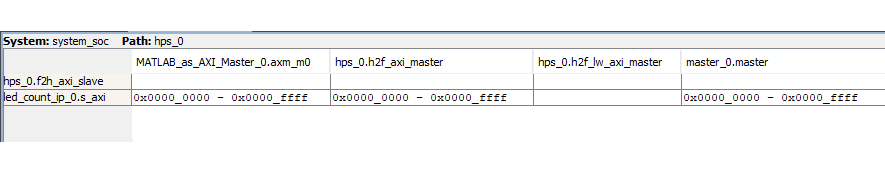

На основе синтаксиса InterfaceConnection опция, для HDL Verifier MATLAB как Ведущий IP AXI, AXI Master Instance Name MATLAB_as_AXI_Master_0 и Port name axm_m0. Для каждого Основного IP AXI, BaseAddress из ядра IP HDL и InterfaceConnection должен быть задан как массив ячеек из символьных векторов.

Необходимо убедиться, что Основной дюйм/с AXI был уже включен в проект исходного проекта Qsys. system_soc.qsys файл, который задан CustomQsysPrjFile свойство addCustomQsysDesign метод. В этом файле необходимо убедиться, что два Основных IP AXI соединяются с тем же Соединительным IP Qsys AXI.

Межсоединения затем соединяют Основного дюйм/с AXI с ведомыми интерфейсами AXI4 в ядре IP HDL.

После того, как вы запускаете IP Core Generation рабочий процесс и создает Куарта® проект, откройте проект. В проекте Куарта вы видите три Основных IP AXI и Основные интерфейсы AXI, соединенные с ядром IP HDL для DUT. Если вы выбираете вкладку Address Map, вы видите Основные имена экземпляра AXI, имена порта и соответствующие адресные пространства.

hdlcoder.Board | hdlcoder.ReferenceDesign