Во многих проектах DUT не является автономным. Например, рассмотрите DUT, который является частью большей системы, которая предоставляет сигналы синхронизации к ее компонентам под управлением глобальных часов. Глобальные часы обычно запускаются на более высоком уровне, чем некоторые компоненты под его управлением. Путем определения такого global oversampling clock можно объединяться DUT в большую систему без использования Сверхдискретизировали или блоки Downsample.

Чтобы сгенерировать глобальную переменную синхронизируют логику, вы задаете oversampling factor. Фактор сверхдискретизации описывает желаемый уровень глобальных часов сверхдискретизации как кратное базовой ставке вашей модели.

Когда вы задаете фактор сверхдискретизации, HDL Coder™ генерирует глобальные часы сверхдискретизации и выводит необходимые сигналы синхронизации из сигнала часов. Генерация глобальных часов сверхдискретизации влияет только на сгенерированный HDL-код. Часы не влияют на поведение симуляции вашей модели.

Когда вы зададите фактор сверхдискретизации для глобальных часов сверхдискретизации, отметьте эти требования:

Фактором сверхдискретизации должно быть целое число, больше, чем или равный 1.

Значение по умолчанию равняется 1. В случае по умолчанию HDL Coder не генерирует глобальные часы сверхдискретизации.

Некоторые DUTs требуют нескольких частот дискретизации для своих внутренних операций. В таких случаях другие уровни в DUT должны разделиться равномерно на глобальный уровень сверхдискретизации. Для получения дополнительной информации смотрите, что Решение Сверхдискретизировало Конфликты Уровня.

Можно задать фактор сверхдискретизации для глобальных часов от графический интерфейса пользователя можно следующим образом:

Выберите HDL Code Generation> панель Global Settings в диалоговом окне Configuration Parameters.

Для Oversampling factor в разделе Clock settings введите желаемый фактор сверхдискретизации. В следующем рисунке Oversampling factor задает глобальные часы сверхдискретизации, которые достигают десять раз базовой ставки модели.

Нажмите Generate на панели HDL Code Generation, чтобы инициировать генерацию кода.

HDL Coder сообщает о тактовой частоте сверхдискретизации:

### Begin VHDL Code Generation ### MESSAGE: The design requires 10 times faster clock with respect to the base rate = 1. ### Working on symmetric_fir_tc as hdlsrc\symmetric_fir_tc.vhd ### Working on sfir_fixed/symmetric_fir as hdlsrc\symmetric_fir.vhd ### HDL Code Generation Complete.

Можно задать фактор сверхдискретизации для глобальных часов из командной строки путем установки Oversampling свойство с hdlset_param или makehdl. Следующий пример задает фактор сверхдискретизации 7:

makehdl(gcb,'Oversampling', 7)### Generating HDL for 'sfir_fixed/symmetric_fir' ### Starting HDL Check. ### HDL Check Complete with 0 errors, 0 warnings and 0 messages. ### Begin VHDL Code Generation ### MESSAGE: The design requires 7 times faster clock with respect to the base rate = 1. ### Working on symmetric_fir_tc as hdlsrc\symmetric_fir_tc.vhd ### Working on sfir_fixed/symmetric_fir as hdlsrc\symmetric_fir.vhd ### HDL Code Generation Complete.

Реализация HDL некоторых проектов является по сути многоскоростной, даже при том, что исходный Simulink® модель является односкоростной. Как пример, рассмотрите simplevectorsum_cascade модель.

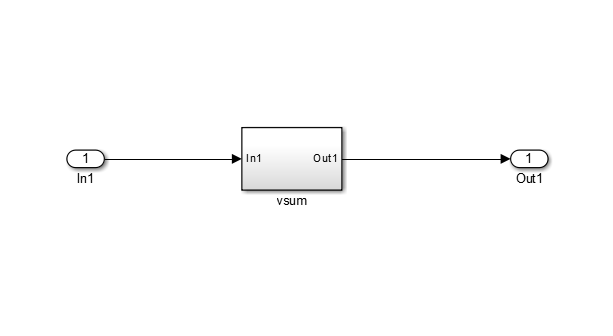

Эта модель состоит из подсистемы, vsum, управляемый векторным входом ширины 10, со скалярным выходом. Следующий рисунок показывает корневой уровень модели.

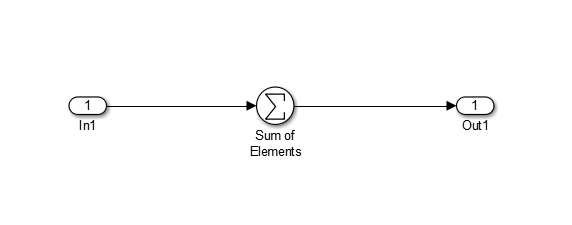

Устройством под тестом является vsum подсистема, показанная в следующем рисунке. Подсистема содержит блок Sum, сконфигурированный для векторного суммирования.

simplevectorsum_cascade модель задает каскадную реализацию (SumCascadeHDLEmission) для блока Sum. Сгенерированный HDL-код для каскадной векторной реализации блока Sum достигает двух эффективных уровней: более быстрое (сверхдискретизация) уровень для внутренних расчетов и более медленный уровень для ввода/вывода. HDL Coder сообщает, что свойственный уровень сверхдискретизации для DUT является пять раз базовой ставкой:

dut = 'simplevectorsum_cascade/vsum';

makehdl(dut);

### Generating HDL for 'simplevectorsum_cascade/vsum'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### The code generation and optimization options you have chosen have introduced

additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for

compensation.

### The DUT requires an initial pipeline setup latency. Each output port

experiences these additional delays

### Output port 0: 1 cycles

### Begin VHDL Code Generation

### MESSAGE: The design requires 5 times faster clock with respect to the

base rate = 1.

...

В некоторых случаях требования часов для такого DUT конфликтуют с глобальным уровнем сверхдискретизации. Чтобы постараться не сверхдискретизировать конфликты уровня, проверьте что подуровни в делении модели равномерно в глобальный уровень сверхдискретизации.

Например, если вы запрашиваете глобальный уровень сверхдискретизации 8 для simplevectorsum_cascade модель, кодер выводит предупреждение и игнорирует требуемый фактор сверхдискретизации. Кодер вместо этого уважает фактор сверхдискретизации, который запрашивает DUT:

dut = 'simplevectorsum_cascade/vsum'; makehdl(dut,'Oversampling',8);

### Generating HDL for 'simplevectorsum/vsum'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### The code generation and optimization options you have chosen have introduced

additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for

compensation.

### The DUT requires an initial pipeline setup latency. Each output port

experiences these additional delays

### Output port 0: 1 cycles

### Begin VHDL Code Generation

### WARNING: The design requires 5 times faster clock with respect to

the base rate = 1, which is incompatible with the oversampling

value (8). Oversampling value is ignored.

...Фактор сверхдискретизации 10 работает в этом случае:

dut = 'simplevectorsum_cascade/vsum'; makehdl(dut,'Oversampling',10);

### Generating HDL for 'simplevectorsum_cascade/vsum'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### The code generation and optimization options you have chosen have introduced

additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for

compensation.

### The DUT requires an initial pipeline setup latency. Each output port

experiences these additional delays

### Output port 0: 1 cycles

### Begin VHDL Code Generation

### MESSAGE: The design requires 10 times faster clock with respect to

the base rate = 1.

...