Распределенная арифметика (DA) является широко используемым методом для реализации расчетов суммы продуктов без использования множителей. Разработчики часто используют DA, чтобы создать эффективный, Умножаются - Накапливают Схему (MAC) для фильтров и других приложений DSP.

Основным преимуществом DA является свой высокий вычислительный КПД. DA распределяет, умножают и накапливают операции через переключатели, интерполяционные таблицы (LUTs) и сумматоры таким способом, которым не требуются обычные множители.

Кодер поддерживает DA в HDL-коде, сгенерированном для нескольких односкоростных и многоскоростных КИХ-структур фильтра для проектов фильтра фиксированной точки. (См. Требования и Факторы для Генерации Распределенного Арифметического Кода.)

Этот раздел кратко подводит итог операции DA. Детальные обсуждения теоретических основ DA появляются в следующих публикациях:

Мейер-Бэезе, U., Цифровая обработка сигналов с Программируемыми пользователем вентильными матрицами, Вторым Выпуском, Спрингером, стр 88–94, 128–143.

White, S.A., приложения распределенной арифметики к цифровой обработке сигналов: учебный анализ. IEEE журнал ASSP, издание 6, № 3.

В реализации DA КИХ фильтруют структуру, последовательность слов входных данных ширины W питается через параллельно-последовательный сдвиговый регистр. Это сквозное соединение производит сериализованный поток битов. Сериализированные данные затем питаются сдвиговый регистр шириной в бит. Этот сдвиговый регистр служит линией задержки, храня битные выборки последовательных данных.

Линия задержки касается (на основе входного размера слова W), чтобы сформировать W- битный адрес, который индексирует в интерполяционную таблицу (LUT). LUT хранит возможные суммы частичных продуктов по содействующему пробелу фильтра. Сдвиг и сумматор (масштабирующий аккумулятор) следуют за LUT. Эта логика последовательно добавляет значения, полученные из LUT.

Поиск по таблице выполняется последовательно для каждого бита (в порядке значения, начинающего с LSB). На каждом такте результат LUT добавляется к накопленному и переключенному результату предыдущего цикла. Для последнего бита (MSB) результат поиска по таблице вычтен, составляя знак операнда.

Эта каноническая форма DA полностью последовательна, работающий с одним битом за один раз. Если последовательностью входных данных является W широкие биты, затем КИХ-структура берет W такты, чтобы вычислить выход. Симметричные и асимметричные КИХ-структуры являются исключением, требуя W+1 циклы, потому что один дополнительный такт требуется, чтобы обрабатывать бит переноса предварительных сумматоров.

По сути битная последовательная природа DA может ограничить пропускную способность. Чтобы улучшить пропускную способность, основной алгоритм DA может быть изменен, чтобы вычислить больше чем одну битную сумму за один раз. Количество одновременно вычисленных битных сумм описывается, как степень двойки вызвала DA radix. Например, основание DA 2 (2^1) указывает, что одна битная сумма вычисляется за один раз. Основание DA 4 (2^2) указывает, что двухбитовые суммы вычисляются за один раз и так далее.

Чтобы вычислить больше чем одну битную сумму за один раз, кодер реплицирует LUT. Например, чтобы выполнить DA на двух битах за один раз (основание 4), нечетные биты питаются один LUT, и ровные биты одновременно питаются идентичный LUT. Результаты LUT, соответствующие нечетным битам, лево-переключены, прежде чем они будут добавлены к результатам LUT, соответствующим даже битам. Этот результат затем подан в масштабирующийся аккумулятор, который переключает его значение обратной связи двумя местами.

Обработка больше чем одного бита за один раз вводит степень параллелизма в операцию, которая может улучшать производительность за счет области. DARadix свойство позволяет вам задать количество битов, обработанных одновременно в.

Размер LUT растет экспоненциально с порядком фильтра. Для фильтра с N коэффициенты, LUT должен иметь 2^N значения. Для фильтров высшего порядка размер LUT должен уменьшаться до разумных уровней. Чтобы уменьшать размер, можно подразделить LUT на несколько LUTs, названные LUT partitions. Каждый раздел LUT работает с различным набором касаний. Результаты, полученные из разделов, суммированы.

Например, для 160 фильтров касания, размером LUT является (2^160)*W биты, где W размер слова данных о LUT. Можно достигнуть значительного сокращения размера LUT путем деления LUT на 16 разделов LUT, каждый берущий 10 входных параметров (касания). Это деление уменьшает общий размер LUT до 16*(2^10)*W биты.

Несмотря на то, что разделение LUT уменьшает размер LUT, архитектура использует больше сумматоров, чтобы суммировать данные о LUT.

DALUTPartition свойство позволяет вам задать, как LUT разделен в.

Кодер позволяет вам управлять, как код DA сгенерирован с помощью DALUTPartition и DARadix свойства (или эквивалентные опции диалогового окна Generate HDL). Перед использованием этих свойств рассмотрите следующие общие требования, ограничения и другие факторы для генерации кода DA.

Кодер поддерживает DA в HDL-коде, сгенерированном для следующих односкоростных и многоскоростных КИХ-структур фильтра:

прямая форма (dfilt.dffir или dsp.FIRFilter)

прямая симметричная форма (dfilt.dfsymfir или dsp.FIRFilter)

прямая асимметричная форма (dfilt.dfasymfir или dsp.FIRFilter)

dsp.FIRDecimator

dsp.FIRInterpolator

Генерация кода DA поддерживается только для проектов фильтра фиксированной точки.

Информационный канал в HDL-коде, сгенерированном для архитектуры DA, оптимизирован для расчетов полной точности. Фильтр бросает результат к размеру выходных данных в заключительном этапе. Если ваш объект фильтра собирается использовать типы данных полной точности, числовые результаты симуляции сгенерированного HDL-кода битно-верны для выхода исходного объекта фильтра.

Если ваш объект фильтра настроил слово или дробные длины, сгенерированный код DA может привести к числовым результатам, которые отличаются, чем выход исходного объекта фильтра.

DA игнорирует касания, которые имеют коэффициенты с нулевым знаком, и уменьшает размер LUT DA соответственно.

Для симметричных и асимметричных КИХ-фильтров:

Предварительный сумматор битного уровня или предварительное вычитающее устройство требуются, чтобы добавлять значения данных касания, которые имеют коэффициенты равного значения и/или противоположного знака. Один дополнительный такт требуется, чтобы вычислять результат из-за дополнительного бита переноса.

Кодер использует в своих интересах симметрию фильтра. Эта симметрия уменьшает размер LUT DA существенно, потому что эффективная длина фильтра для этих, которые вводит фильтр, разделена на два.

Разделенные распределенные арифметические архитектуры реализуют внутренние тактовые частоты выше, чем входной уровень. В таких реализациях фильтра существует N циклы (N >= 2) из основных часов для каждой входной выборки. Можно задать, сколько тактов испытательный стенд содержит значения входных данных в допустимом состоянии.

Когда вы выбираете Hold input data between samples (значение по умолчанию), испытательный стенд содержит значения входных данных в допустимом состоянии для N такты.

Когда вы очищаете Hold input data between samples, испытательный стенд содержит значения входных данных в допустимом состоянии только для одного такта. Для следующего N-1 циклы, испытательный стенд управляет данными к неизвестному состоянию (описанный как 'X') пока следующая входная выборка не начата работу. Принуждение входных данных к неизвестному состоянию проверяет что сгенерированные кодовые регистры фильтра входные данные только на первом цикле.

generatehdl СвойстваДва свойства задают распределенные арифметические опции к generatehdl функция:

DALUTPartition — Номер и размер интерполяционной таблицы (LUT) разделы.

DARadix — Количество битов обрабатывается параллельно.

Можно использовать функцию помощника hdlfilterdainfo исследовать возможные разделы и настройки основания для вашего фильтра.

Для примеров смотрите

Диалоговое окно Generate HDL предоставляет несколько возможностей, связанных с генерацией кода DA.

Всплывающее меню Architecture, которое позволяет вам включить генерацию кода DA и связанные с отображениями опции.

Выпадающее меню Specify folding, которое позволяет вам непосредственно задать складной фактор или установить значение для DARadix свойство.

Выпадающее меню Specify LUT, которое позволяет вам непосредственно установить значение для DALUTPartition свойство. Можно также выбрать ширину адреса для LUT. Если вы задаете ширину адреса, кодер использует вход LUTs как требуется.

Диалоговое окно Generate HDL первоначально отображается связанные с DA значения опции по умолчанию, которые соответствуют текущему созданию фильтра. Для требований для установки этих опций смотрите DALUTPartition и DARadix.

Чтобы задать генерацию кода DA, использующую диалоговое окно Generate HDL, выполните эти шаги:

Спроектируйте КИХ-фильтр (использующий Filter Designer, Filter Builder или MATLAB® команды), который удовлетворяет требования, описанные в Требованиях и Факторах для Генерации Распределенного Арифметического Кода.

Откройте диалоговое окно Generate HDL.

Выберите Distributed Arithmetic (DA) от всплывающего меню Architecture.

Когда вы выбираете эту опцию, связанный Specify folding и опции Specify LUT отображены ниже меню Architecture. Следующая фигура показывает варианты DA по умолчанию для прямого КИХ-фильтра формы.

Выберите одну из следующих опций от Specify folding выпадающее меню:

Folding factor (значение по умолчанию): Выберите складной фактор из выпадающего меню справа от Specify folding. Меню содержит исчерпывающий список сворачивания факторных опций для фильтра.

DA radix: Выберите количество битов, обработанных одновременно, описанных как степень 2. DA radix по умолчанию значением является 2, определение обработки одного бита за один раз или полностью последовательного DA. При желании установите DA radix поле к значению не по умолчанию.

Выберите одну из следующих опций от Specify LUT выпадающее меню:

Address width (значение по умолчанию): Выберите из выпадающего меню справа от Specify LUT. Меню содержит исчерпывающий список ширин адреса LUT для фильтра.

Partition: Выберите или войдите, вектор, задающий номер и размер разделов LUT.

Установите другие опции HDL как требуется и сгенерируйте код. О недопустимых или недопустимых значениях для LUT Partition или DA Radix сообщают во время генерации кода.

Когда вы взаимодействуете с Specify folding и опциями Specify LUT, вы видите результаты по вашему выбору в трех полях только для отображения: Folding factor, Address width, и Total LUT size (bits).

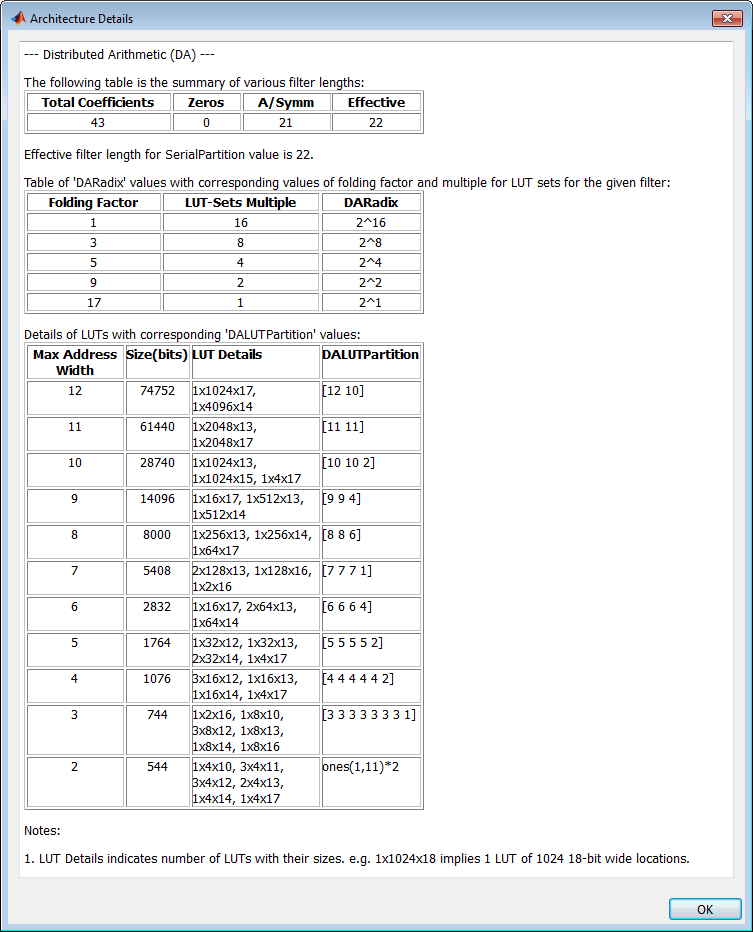

Кроме того, когда вы кликаете по гиперссылке View details, кодер отображает отчет, показывающий полный DA архитектурные детали для текущего фильтра, включая:

Отфильтруйте длины

Полный список применимых факторов сворачивания и как они применяются к наборам LUTs

Табулирование настроек LUTs с общим Размером LUT и деталями LUT

Следующий рисунок показывает типичный отчет.

Когда Distributed Arithmetic (DA) выбран в меню Architecture, некоторые другие опции HDL превращаются автоматически в настройки, которые соответствуют генерации кода DA:

Coefficient multipliers установлен в Multiplier и отключенный.

FIR adder style установлен в Tree и отключенный.

Add input register (в панели Ports) выбран и отключен. (Входной регистр, используемый в качестве части сдвигового регистра, используется в коде.)

Add output register (в панели Ports) выбран и отключен.