Следуйте инструкциям для вызова HDL Workflow Advisor. Смотрите Начало работы с HDL Workflow Advisor (HDL Coder).

Примечание

У вас должна быть лицензия HDL Coder™, чтобы сгенерировать HDL-код с помощью HDL Workflow Advisor.

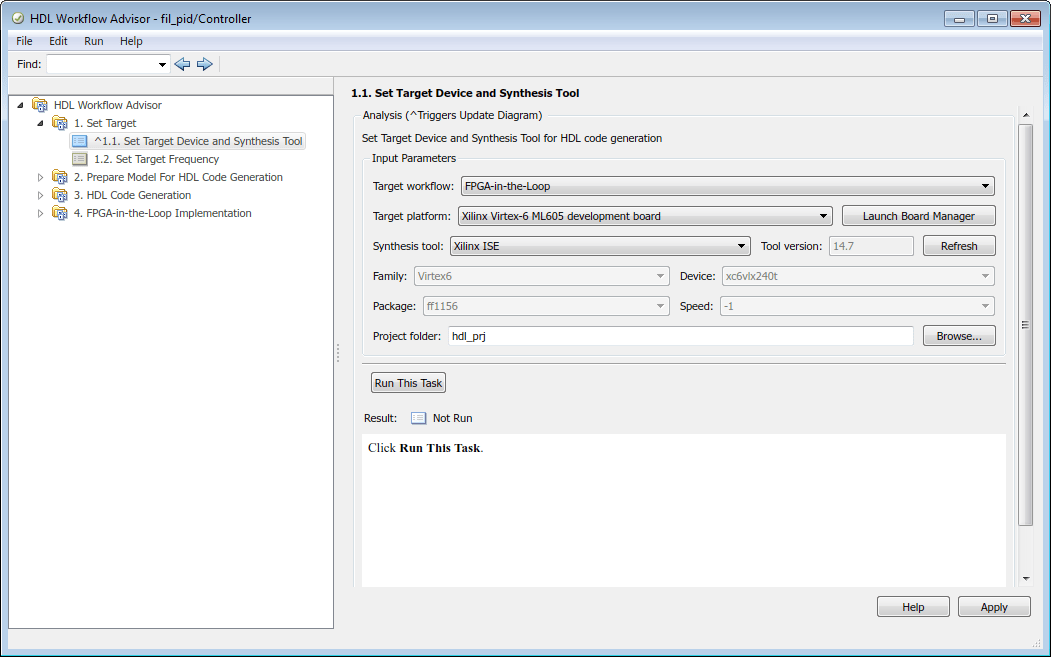

На шаге 1, Set Target, нажимают 1.1 Set Target Device and Synthesis Workflow и делают следующее:

Выберите FPGA-in-the-Loop из выпадающего списка в Target Workflow.

Под Target Platform выберите макетную плату из выпадающего списка. Family, Device, Package и Speed заполнены в HDL Workflow Advisor. Если вы еще не загрузили пакет поддержки плат FPGA HDL Verifier™, выберите Get more boards. Затем возвратитесь к этому шагу после того, как вы загрузите пакет поддержки плат FPGA.

Для Folder введите имя папки, чтобы сохранить файлы проекта в. Значением по умолчанию является hdl_prj под текущей рабочей папкой.

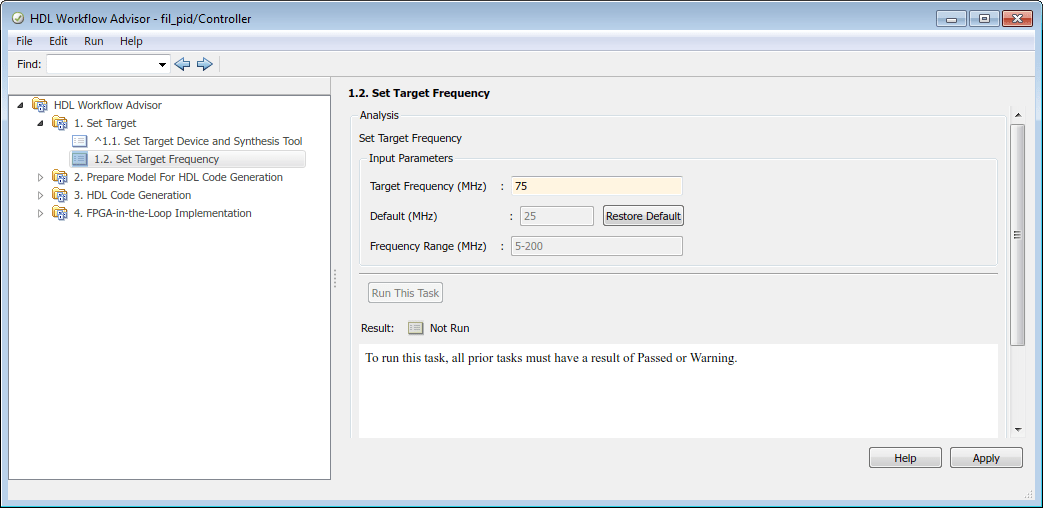

После того, как вы выберете цель FIL на Шаге 1.1, нажмите 1.2 Set Target Frequency.

Установите Target Frequency (MHz) для тактовой частоты вашего проекта, реализованного на FPGA. Доступную область значений частот показывают в параметре Frequency Range (MHz). Для Intel® платы и Xilinx® платы, Советник по вопросам Рабочего процесса проверяет требуемую частоту по возможным для требуемой платы. Если требуемая частота не возможна для этой платы, Советник по вопросам Рабочего процесса возвращает ошибку и предлагает альтернативную частоту. Для Xilinx Vivado®- поддерживаемые платы или PCI Express® платы, Советник по вопросам Рабочего процесса не может проверять частоту. Инструменты синтеза предпринимают попытку максимальных усилий требуемой частоты, но могут выбрать альтернативную частоту, если заданная частота не была достижима. Значением по умолчанию является 25 МГц.

На шаге 2, Prepare Model for HDL Code Generation, выполняют шаги 2.1-2.4 как описано в, Готовят Модель К Обзору генерации HDL-кода (HDL Coder).

Кроме того, выполните шаг 2.5 Check FPGA-in-the-Loop Compatibility, чтобы проверить, что модель совместима с FIL.

На шаге 3, HDL Code Generation, выполняют шаги 3.1 и 3.2 как описано в Обзоре генерации HDL-кода (HDL Coder).

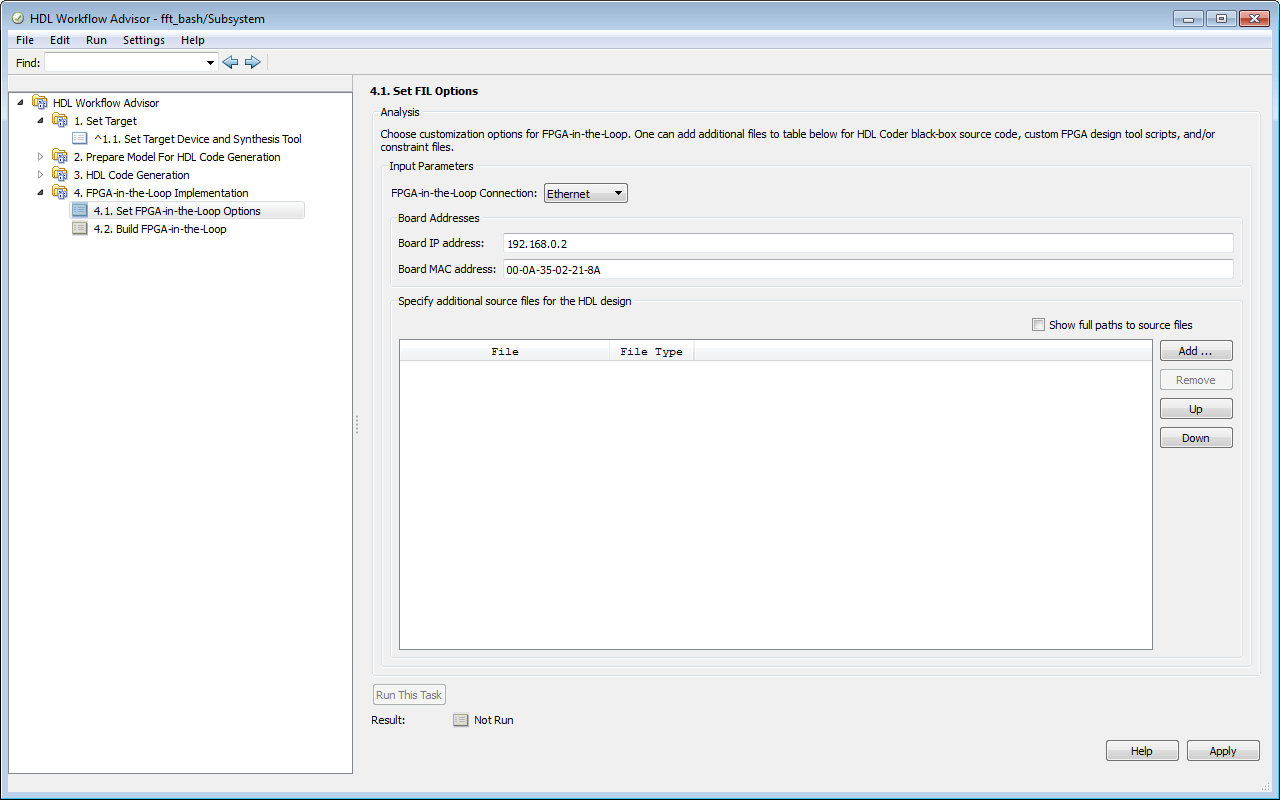

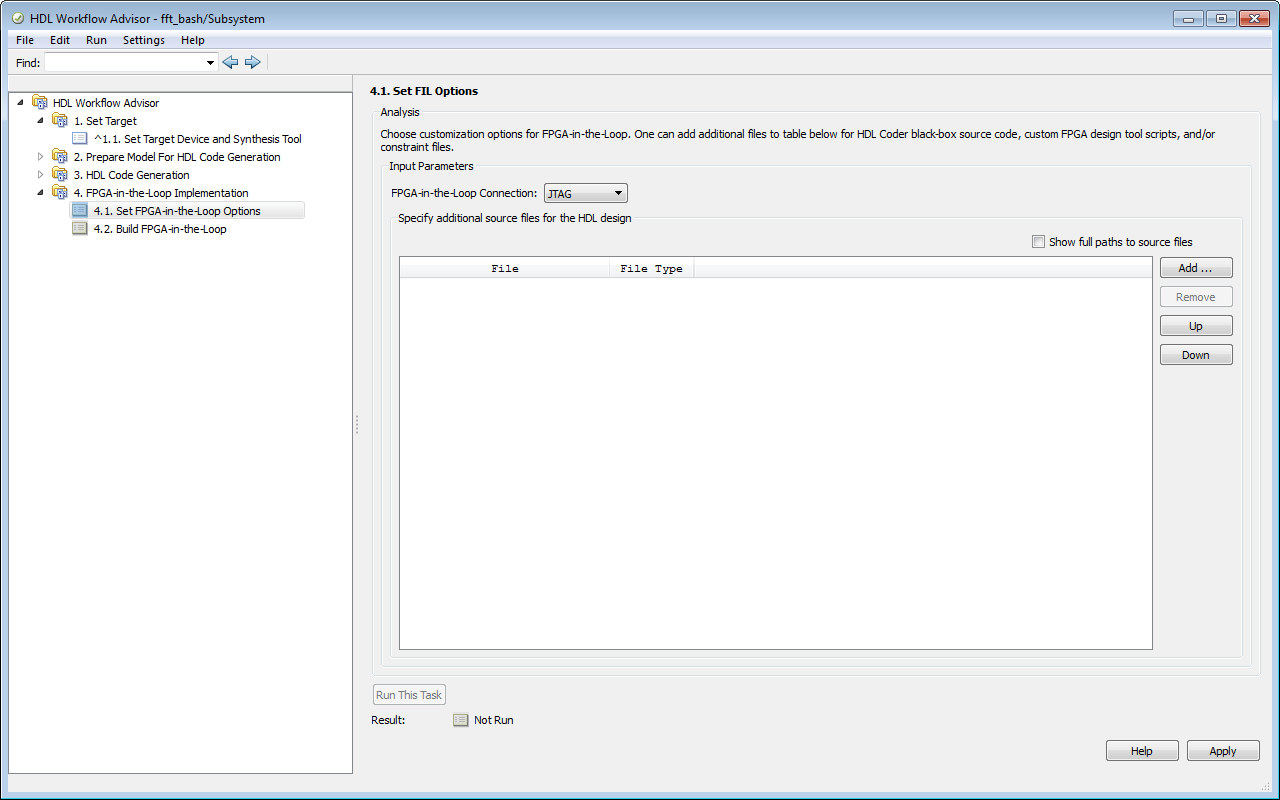

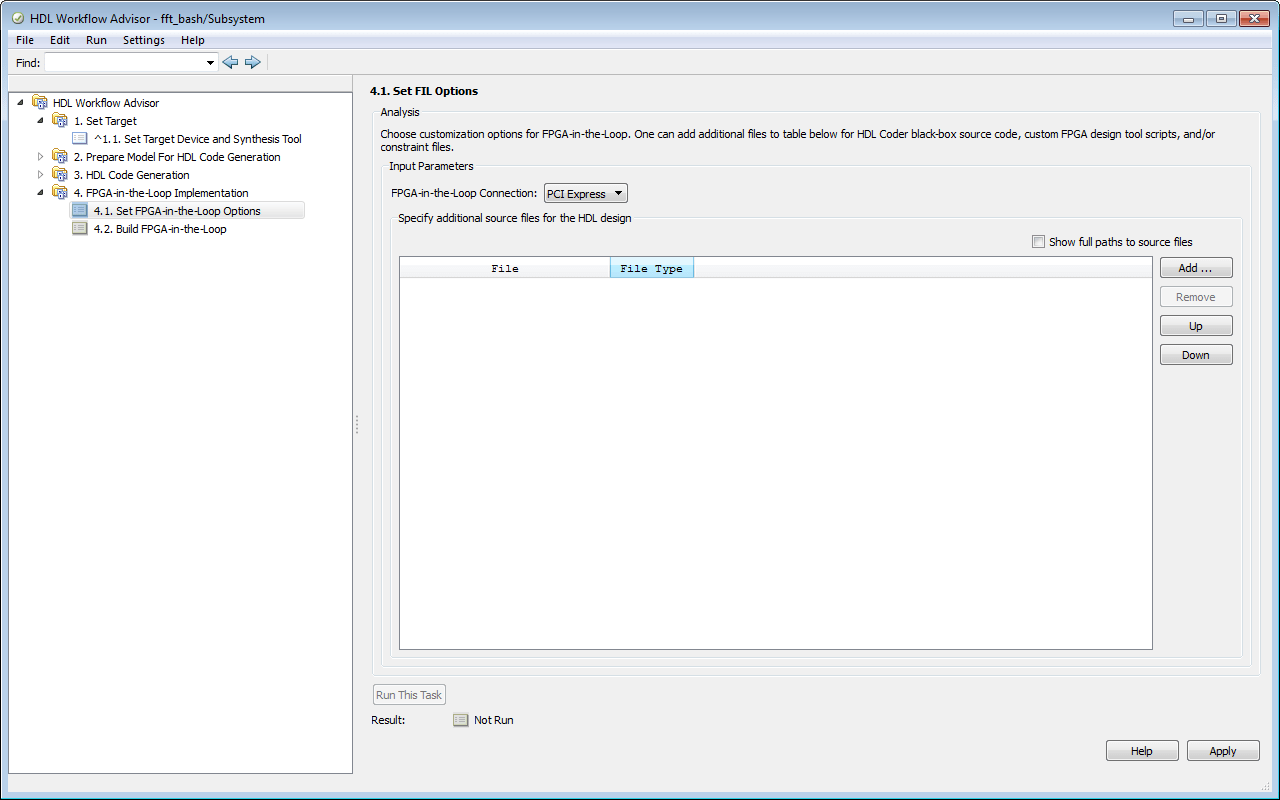

На шаге 4.1, Set FPGA-in-the-Loop Options, изменяют эти опции при необходимости:

FPGA-in-the-Loop Connection: метод связи симуляции FIL. Опции в выпадающем меню обновляются в зависимости от методов связи, поддержанных для требуемой платы, которую вы выбрали. Если требуемая плата и HDL Verifier поддерживают связь, можно выбрать Ethernet, JTAG, или PCI Express.

Board Address:

Когда вы выбираете соединение Ethernet, можно настроить IP платы и Мак адреса при необходимости.

| Опция | Инструкции |

|---|---|

| Board IP address | Используйте эту опцию для установки IP-адреса платы, если это не IP-адрес по умолчанию (192.168.0.2). Если IP-адрес платы по умолчанию (192.168.0.2) используется другим устройством, или вы нуждаетесь в различной подсети, изменяете IP-адрес Совета согласно следующим инструкциям:

|

| Board MAC address | При большинстве обстоятельств вы не должны изменять Мак адрес платы. Если вы соединяете больше чем одну макетную плату FPGA с одним хостом - компьютером, изменяете Мак адрес платы для каких-либо дополнительных плат так, чтобы каждый адрес был уникален. У вас должен быть отдельный NIC для каждой платы. Чтобы изменить Мак адрес Совета, щелкните в поле Board MAC address. Задайте адрес, который отличается с той принадлежности на любое другое устройство, присоединенное к вашему компьютеру. Чтобы получить Мак адрес Совета для определенной макетной платы FPGA, обратитесь к метке, присоединенной к плате, или консультируйтесь с документацией по продукту. |

Specify additional source files for the HDL design:

Укажите на дополнительные исходные файлы для DUT использование Add. Чтобы (опционально) отобразить полные пути к исходным файлам, установите флажок, названный Show full paths to source files. HDL Workflow Advisor пытается идентифицировать тип исходного файла. Если тип файла является неправильным, можно изменить его путем выбора из File Type выпадающего списка.

FIL по Ethernet

FIL по JTAG

FIL по PCI Express

На шаге 4.2, Build FPGA-in-the-Loop, нажимают Run this task.

Во время процесса сборки происходят следующие действия:

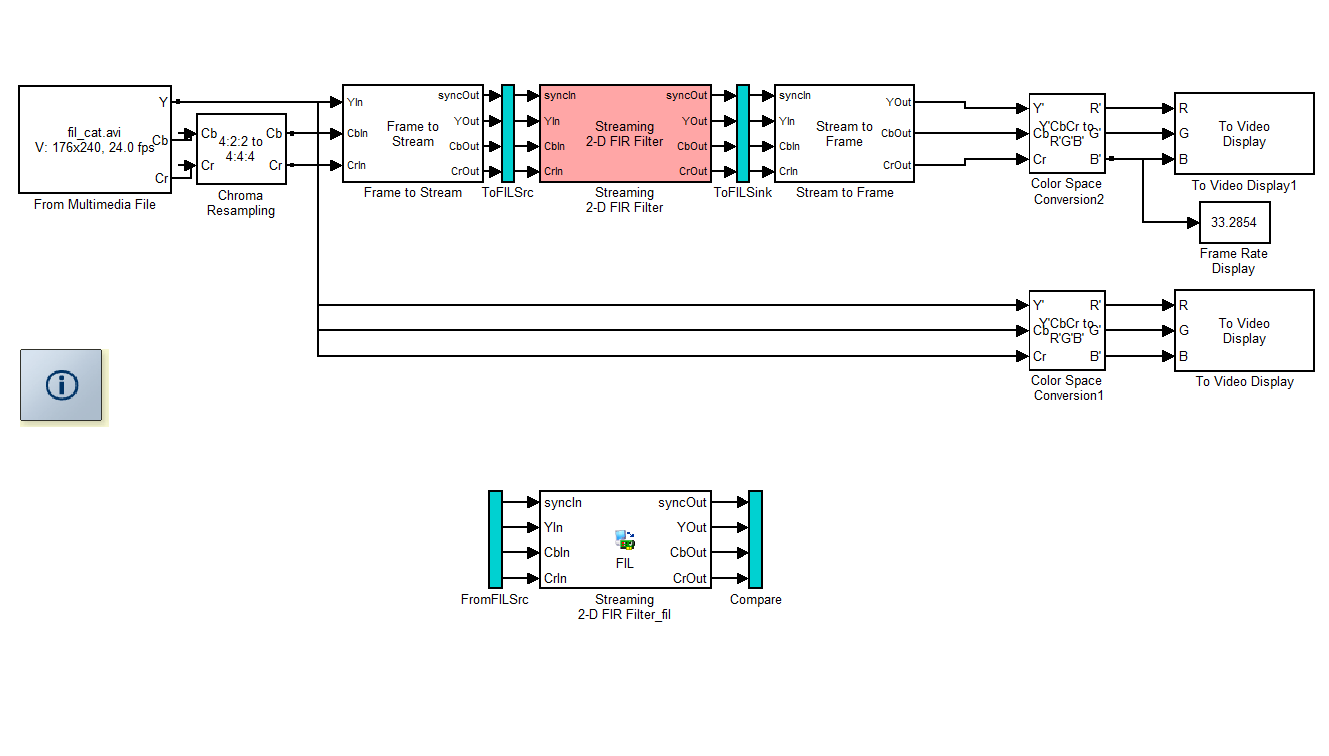

HDL Workflow Advisor генерирует блок FIL, названный в честь модуля верхнего уровня, и помещает его в новую модель. Следующий рисунок показывает пример новой модели, содержащей блок FIL.

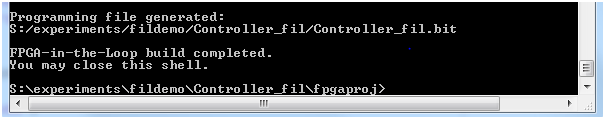

После новой генерации модели HDL Workflow Advisor открывает командное окно:

В этом окне программное обеспечение проекта FPGA выполняет синтез, подгонку, PAR и FPGA, программируя генерацию файла.

Когда процесс завершается, сообщение в командном окне предлагает вам закрывать окно.

HDL Workflow Advisor создает тестовую модель вокруг сгенерированного блока FIL.

Гарантируйте, что ваша макетная плата FPGA настраивается, включается и соединяется с вашей машиной, как направлено документацией изготовителя платы. Затем выполните следующие шаги, чтобы программировать FPGA:

Дважды кликните блок FIL в своем Simulink® модель, чтобы открыть маску блока.

На вкладке Main нажмите Load, чтобы загрузить файл программирования на FPGA.

Процесс загрузки может занять несколько минут, в зависимости от того, насколько большой подсистема. Для очень больших подсистем процесс может занять час или дольше.

Для дальнейших советов поиска и устранения неисправностей смотрите, что Загрузка Программирует Файл на FPGA.

В Simulink, на вкладке Simulation, нажимают Run. Результаты симуляции FIL должны совпадать с теми из образца модели Simulink или исходного HDL-кода.

Примечание

Относительно инициализации: Simulink запускается со времени 0 каждых раз, что означает, что RAM в Simulink инициализируется, чтобы обнулить. Однако это не верно в оборудовании. Если у вас будет RAM в вашем проекте, первая симуляция будет совпадать с Simulink, но любые последующие запуски не могут соответствовать.

Обходное решение должно перезагрузить поток битов FPGA прежде, чем повторно выполнить симуляцию. Для этого нажмите Load на маске блока FIL.