HDL Workflow Advisor является инструментом, который поддерживает набор задач, покрывающих этапы процесса проектирования FPGA. Некоторые задачи выполняют проверку допустимости модели или проверку; другие запускают генератор HDL-кода или сторонние программы. Каждая папка в верхнем уровне HDL Workflow Advisor содержит группу связанных задач, которые можно выбрать и запустить.

Для итоговой информации о каждой папке HDL Workflow Advisor или задаче, выберите папку или значок задачи и затем нажмите кнопку HDL Workflow Advisor Help.

Set Target: задачи в этой категории позволяют вам выбрать желаемое целевое устройство и сопоставить его интерфейс I/O с вводами и выводами вашей модели.

Prepare Model For HDL Code Generation: задачи в этой категории проверяют вашу модель на совместимость генерации HDL-кода. Задачи также сообщают относительно настроек модели, блоков или других условий (таких как алгебраические циклы), который препятствовал бы генерации кода, и предоставлять консультацию о том, как решить такие проблемы.

HDL Code Generation: Эта категория поддерживает все связанные с HDL опции диалогового окна Параметров конфигурации, включая установку HDL-кода и параметров генерации испытательного стенда и генерации кода, испытательного стенда или cosimulation модели.

FPGA Synthesis and Analysis: задачи в этой поддержке категории:

Синтез и анализ синхронизации посредством интеграции со сторонними инструментами синтеза

Обратная корректировка проекта модели с критическим путем и другой информацией получена во время синтеза

FPGA-in-the-Loop Implementation: Эта категория реализует фазы FIL, включая обеспечение генерации блока, синтеза, логического отображения, PAR (место-и-маршрут), программируя генерацию файла и коммуникационный канал. Эти возможности спроектированы для конкретной платы и адаптированы в соответствии с вашим кодом RTL. Лицензия HDL Verifier™ требуется для FIL.

Download to Target: задачи в этой категории зависят от выбранного целевого устройства и потенциально включают:

Генерация целевого файла программирования FPGA

Программирование целевого устройства

Генерация модели, которая содержит Simulink® Подсистема интерфейса Real-Time™

В папке Set Target можно выбрать целевое устройство FPGA и задать интерфейс, сгенерированный для устройства.

Set Target Device and Synthesis Tool: Выберите целевое устройство FPGA и инструменты синтеза.

Set Target Reference Design: для IP Core Generation рабочий процесс, выберите исходный проект для своего целевого устройства.

Set Target Interface: для IP Core Generation, FPGA Turnkey, и Simulink Real Time FPGA I/O рабочие процессы, используйте таблицу интерфейса целевой платформы, чтобы присвоить каждый порт на вашем DUT к ресурсу ввода-вывода на целевом устройстве. Используйте Enable HDL DUT port generation for test points , чтобы создать выходные порты DUT для сигналов тестовой точки в сгенерированном HDL-коде.

Set Target Frequency: Выберите целевую тактовую частоту для реализации FPGA вашего проекта.

Для получения дополнительной информации о каждой задаче Set Target выберите значок задачи и затем нажмите кнопку HDL Workflow Advisor Help.

Задача Set Target Device and Synthesis Tool позволяет вам выбрать целевое устройство FPGA и связанный инструмент синтеза из выпадающего меню, которое перечисляет устройства, которые в настоящее время поддерживает HDL Workflow Advisor.

Эта задача отображает следующие опции:

Target Workflow: выпадающее меню, которое перечисляет возможные рабочие процессы тот HDL Workflow Advisor поддержки. Выберите из:

Типовой ASIC/FPGA

FPGA в цикле

Тюремщик FPGA

Ввод-вывод FPGA Simulink Real-Time

Генерация ядра IP

Индивидуальная настройка для устройства USRP

Программно определяемое радио

Target platform: выпадающее меню, которое перечисляет устройства HDL Workflow Advisor в настоящее время, поддерживает. Не доступный для Типового рабочего процесса ASIC/FPGA.

Synthesis tool: Выберите инструмент синтеза, затем выберите Family, Device, Package и Speed для вашей цели синтеза.

Если ваш инструмент синтеза не является одной из опций Synthesis tool, смотрите Setup Инструмента Path Синтеза. После того, как вы настроите свой инструмент path синтеза, нажмите Refresh, чтобы сделать инструмент доступным в HDL Workflow Advisor.

Project folder: Задайте имя папки проекта.

Tool version: Это выводы информации на экран текущая версия инструмента синтеза.

Allow unsupported version: Когда вы используете неподдерживаемую версию инструмента синтеза, устанавливая этот флажок. Можно продолжить создавать проект с неподдерживаемой версией инструмента синтеза. Если вы снимаете этот флажок, HDL Coder™ генерирует ошибку, когда вы запускаете эту задачу. Эта опция недоступна, когда вы используете поддерживаемую версию инструмента синтеза.

Не рекомендуется использовать неподдерживаемую версию инструмента, потому что это может потенциально вызвать отказ синтеза. Для получения дополнительной информации о списке поддерживаемых инструментов смотрите Поддержку Языка HDL и Поддерживаемые Сторонние программы и Оборудование

Примечание

Если вы выбираете Intel Quartus Pro или Microsemi Libero SoC как Synthesis tool, можно запустить только Generic ASIC/FPGA рабочий процесс. Когда вы используете эти инструменты, задача Annotate Model with Synthesis Result не доступна. В этом случае можно запустить рабочий процесс для синтеза, и затем просмотреть отчеты синхронизации, чтобы видеть критический путь.

Задача Set Target Reference Design отображает входные параметры исходного проекта и версию инструмента. Раздел Reference design parameters отображает любые пользовательские параметры, которые вы задаете для исходного проекта.

Задача отображает следующие опции:

Reference design: выпадающее меню, которое перечисляет исходные проекты, что поддержки HDL Coder и любые пользовательские исходные проекты, которые вы задаете. Чтобы узнать больше о создании пользовательской платы и исходного проекта, смотрите система регистрации Исходного проекта и Совет.

Reference design tool version: текстовое поле, которое отображает текущую версию инструмента исходного проекта. Рекомендуется использовать версию инструмента исходного проекта, которая совместима с поддерживаемой версией инструмента. Если существует несоответствие версии инструмента, HDL Coder генерирует ошибку, когда вы запускаете эту задачу. Несоответствие версии инструмента может потенциально вызвать задачу Create Project перестать работать.

Если вы устанавливаете флажок Ignore tool version mismatch, HDL Coder генерирует предупреждение вместо ошибки. Можно попытаться продолжить создание проекта исходного проекта.

Reference design parameters: Перечисляет параметры исходного проекта. Они могут быть параметрами, доступными с исходными проектами по умолчанию, которые HDL Coder поддерживает, или параметры, которые вы задаете для своего пользовательского исходного проекта. Для получения дополнительной информации смотрите, Задают Пользовательские Параметры и Функции обратного вызова для Пользовательского Исходного проекта.

Задача Set Target Interface отображает свойства портов ввода и вывода на вашем DUT и позволяет вам сопоставить эти порты с ресурсами ввода-вывода на целевом устройстве.

Set Target Interface отображает Таблицу Интерфейса Целевой платформы, которая показывает:

Имя, тип порта (вводы и выводы) и тип данных для каждого порта на вашем DUT.

Выпадающее меню, перечисляющее доступные ресурсы ввода-вывода для целевого устройства.

Эти ресурсы специфичны для устройства. Для получения дальнейшей информации на каждом ресурсе, см. документацию для своей макетной платы FPGA.

Задайте целевую частоту для этих рабочих процессов:

Generic ASIC/FPGA: Задавать целевую частоту, которой вы хотите, чтобы ваш проект достиг. HDL Coder генерирует ограничительный файл синхронизации для той тактовой частоты и добавляет ограничение в проект инструмента синтеза FPGA, который вы создаете в задаче Create Project. Если целевая частота не достижима, инструмент синтеза генерирует ошибку. Целевая частота не поддерживается с Микрополу® Либеро® SoC.

IP Core Generation: Чтобы задать целевую частоту для HDL Coder, чтобы изменить установку модуля тактовой синхронизации в исходном проекте, чтобы произвести часы сигнализируют с той частотой. Введите целевое значение частоты, которое является в Frequency Range (MHz). Если вы не задаете целевую частоту, HDL Coder использует целевую частоту Default (MHz).

Simulink Real-Time FPGA I/O: Для плат Speedgoat, которые поддерживаются с Xilinx ISE, задайте целевую частоту, чтобы сгенерировать модуль тактовой синхронизации, чтобы произвести сигнал часов с той частотой.

Платы Speedgoat, которые поддерживаются с Xilinx Vivado используйте IP Core Generation инфраструктура рабочего процесса. Задайте целевую частоту для HDL Coder, чтобы изменить установку модуля тактовой синхронизации в исходном проекте, чтобы произвести сигнал часов с той частотой. Введите целевое значение частоты, которое является в Frequency Range (MHz). Если вы не задаете целевую частоту, HDL Coder использует целевую частоту Default (MHz).

FPGA Turnkey: Чтобы сгенерировать модуль тактовой синхронизации, чтобы произвести часы сигнализируют с той частотой автоматически.

Выберите режим синхронизации FPGA процессора и сопоставьте ваши входные порты DUT, выходные порты и тестовые точки к ресурсам ввода-вывода на целевом устройстве.

Режим Coprocessing не поддерживается для рабочего процесса Simulink Real-Time FPGA I/O. Для Processor/FPGA synchronization выберите:

Free running, если вы не хотите, чтобы ваш процессор и FPGA автоматически синхронизировались.

Coprocessing – blocking, если вы хотите, чтобы HDL Coder сгенерировал логику синхронизации для FPGA автоматически, так, чтобы процессор и FPGA, запущенный в тандеме. Выберите этот режим, когда время выполнения FPGA коротко относительно шага расчета процессора, и вы хотите, чтобы FPGA завершился, прежде чем процессор продолжится.

Эта установка сохранена с моделью как ProcessorFPGASynchronization Свойство блока HDL для блока DUT.

Выбор Enable HDL DUT port generation for testpoints:

Отмечает сигналы тестовой точки для генерации кода. Смотрите Сигналы Тестовой точки Модели и Отладки с HDL Coder.

Включает генерацию порта Enable HDL DUT для опции конфигурации модели тестовых точек.

Обновляет целевую интерфейсную таблицу, чтобы отобразить выходные порты тестовой точки в интерфейсной таблице.

Табличные отображения Интерфейса Целевой платформы:

Имя, тип порта (вход, выход и тестовая точка), и тип данных для каждого порта на вашем DUT.

Контекстное меню, перечисляющее доступные ресурсы ввода-вывода для целевого устройства.

Эти ресурсы специфичны для устройства. Для получения дальнейшей информации на каждом ресурсе, см. документацию для своей макетной платы FPGA.

Выберите режим синхронизации FPGA процессора и сопоставьте ваши порты ввода и вывода DUT с ресурсами ввода-вывода на целевом устройстве. Опционально, задайте исходный проект.

Reference design: Выберите предопределенный проект интегрирования встраиваемой системы, в который HDL Coder вставляет ваше сгенерированное ядро IP.

Reference design path: Введите путь к своим загруженным компонентам исходного проекта. Это поле доступно, только если заданный Reference design требует загружаемых компонентов.

Режим Coprocessing не поддерживается для рабочего процесса Simulink Real-Time FPGA I/O. Для Processor/FPGA synchronization выберите:

Free running, если вы не хотите, чтобы ваш процессор и FPGA автоматически синхронизировались.

Coprocessing – blocking, если вы хотите, чтобы HDL Coder сгенерировал логику синхронизации для FPGA автоматически, так, чтобы процессор и FPGA, запущенный в тандеме. Выберите этот режим, когда время выполнения FPGA коротко относительно шага расчета процессора, и вы хотите, чтобы FPGA завершился, прежде чем процессор продолжится.

Эта установка сохранена с моделью как ProcessorFPGASynchronization Свойство блока HDL для блока DUT.

Таблица Интерфейса Целевой платформы показывает:

Имя, тип порта (вводы и выводы) и тип данных для каждого порта на вашем DUT.

Выпадающее меню, перечисляющее доступные ресурсы ввода-вывода для целевого устройства.

Эти ресурсы специфичны для устройства. Для получения дальнейшей информации на каждом ресурсе, см. документацию для своей макетной платы FPGA.

Задачи в папке Prepare Model For HDL Code Generation проверяют модель на совместимость с генерацией HDL-кода. Если бы проверка сталкивается с условием, которое повысило бы предупреждение генерации кода или ошибку, правую панель информации об отображениях HDL Workflow Advisor об условии и как зафиксировать его. Папка Prepare Model For HDL Code Generation содержит эти проверки:

Проверка Check Model Settings ускоряет модель, проверяет удаляющие избыточные проверки. Проверка предоставляет вам, опция, чтобы открыть HDL Code Advisor регистрируется в отдельном окне и осуществляет те проверки.

Check FPGA-in-the-Loop Compatibility: Проверяйте совместимость модели с FPGA в цикле в частности:

Не позволенный: снизьтесь/получите подсистемы, одно/двойные типы данных, обнулите шаг расчета

Должен присутствовать: лицензия HDL Verifier

Эта опция доступна, только если вы выбираете FPGA-in-the-Loop для Целевого рабочего процесса.

Check USRP Compatibility: модель должна иметь два входных порта и два выходных порта 16-битных сигналов со знаком.

Эта опция доступна, только если вы выбираете Customization for the USRP Device для Целевого рабочего процесса.

Для итоговой информации о каждой задаче Prepare Model For HDL Code Generation выберите значок задачи и затем нажмите кнопку HDL Workflow Advisor Help.

Check Model Settings проверяет установки параметров всей модели на совместимость генерации HDL-кода.

Эта проверка ускоряет модель, проверяет удаляющие избыточные проверки. Проверка обеспечивает кнопку, чтобы открыться, HDL Code Advisor регистрируется в отдельном окне. Следующие проверки были заменены проверками HDL Code Advisor :

Check Global Settings.

Check Algebraic Loops

Check Block Compatibility

Check Sample Times

Нажатие на Run This Task не откроет проверки HDL Code Advisor.

Check Model Settings проверяет установки параметров всей модели на совместимость генерации HDL-кода.

Эта проверка исследует параметры модели на совместимость с генерацией HDL-кода и отмечает условия, которые повысили бы ошибку или предупреждение во время генерации кода. HDL Workflow Advisor отображает таблицу со следующей информацией о каждом обнаруженном условии:

Блок: Гиперссылка на страницу диалогового окна настройки модели, которая содержит ошибку или предупреждение условия

Настройки: Имя параметра модели, который вызвал ошибку или предупреждение условия

Текущий: Текущее значение установки

Рекомендуемый: Рекомендуемое значение установки

Серьезность: Уровень серьезности предупреждения или состояния ошибки. Минимально, необходимо зафиксировать настройки, которые помечены как error.

Проверка также предоставляет кнопку открытому Советнику по вопросам HDL-кода в отдельном окне. Советник по вопросам HDL-кода может осуществить дополнительные проверки совместимости генерации HDL-кода, не покрытые этой задачей. Для большего количества информации смотрите проверки настройки Модели.

Совет

Чтобы установить настройки, о которых сообщают, на их рекомендуемые значения, нажмите кнопку Modify All . Можно затем осуществить проверку снова и перейти к следующей проверке.

Нажатие на Run This Task не откроет проверки HDL Code Advisor.

Обнаружьте алгебраические циклы в модели.

Программное обеспечение HDL Coder не поддерживает генерацию HDL-кода для моделей, в которых существуют алгебраические условия цикла. Check Algebraic Loops исследует модель и приводит проверку к сбою, если это обнаруживает алгебраический цикл. Устраните алгебраические циклы из своей модели перед продолжением дальнейших проверок HDL Workflow Advisor или генерации кода.

Проверяйте DUT на неподдерживаемые блоки.

Check Block Compatibility проверяет блоки в DUT для совместимости с генерацией HDL-кода. Проверка перестала работать, если она сталкивается с блоками, которые не поддерживает HDL Coder. HDL Workflow Advisor сообщает о несовместимых блоках, включая полный путь с каждым блоком.

Проверяйте решатель, шаги расчета и настройки режима управления задачами для модели.

Check Sample Times проверяет опции решателя, шаги расчета, определяя задачу для режима и диагностики перехода уровня для совместимости генерации HDL-кода. Опции решателя, которых программное обеспечение HDL Coder требует или рекомендует:

Ввод: фиксированный шаг. (Кодер в настоящее время поддерживает решатели переменного шага при ограниченных условиях. Смотрите hdlsetup для деталей.)

Solver: Дискретный (никакие непрерывные состояния). Другие решатели фиксированного шага могли быть выбраны, но эта опция обычно является лучшей для симуляции дискретных систем.

Tasking mode: SingleTasking. Кодер не делает в настоящее время моделей поддержки, которые выполняются в многозадачном режиме. Не устанавливайте Tasking mode на Auto.

Multitask rate transition и опции диагностики Single task rate transition: установите на Error.

HDL Verifier проверяет модель на совместимость с FPGA в обработке цикла.

Подготовьте DUT к генерации интерфейса FIL (HDL Verifier).

Задачи в папке HDL Code Generation включают вам к:

Установите и подтвердите HDL-код и параметры генерации испытательного стенда. Поддерживается большинство параметров панели HDL Code Generation диалогового окна Configuration Parameters и Model Explorer.

Сгенерируйте любой из:

Код RTL

Испытательный стенд RTL

Модель Cosimulation

Испытательный стенд SystemVerilog DPI

Чтобы запустить задачи в папке HDL Code Generation автоматически, выберите папку и нажмите Run All.

Совет

После каждой задачи в этой папке запуски HDL Coder обновляет диалоговое окно Configuration Parameters и Model Explorer.

Дополнительная задача открыть окно параметров конфигурации HDL Coder.

Set HDL Options является дополнительной задачей. Эта задача предоставляет вам опцию, чтобы запустить диалоговое окно HDL Coder Configuration Parameters в отдельном окне. Изменения в параметрах конфигурации используются в следующей задаче HDL Coder Workflow Advisor.

Примечание

Прежде, чем сделать эту задачу, закройте диалоговое окно Параметров конфигурации HDL Coder.

Когда окно Workflow Advisor открыто для текущего проекта под тестом (DUT), эти параметры конфигурации отключены для редактирования:

Имя модели DUT или подсистемы.

Имя и путь целевой папки генерации кода.

Имя инструмента синтеза.

Выбор семейства устройств.

Выбор устройства.

Выбор пакета устройства.

Выбор скорости устройства.

Целевая частота.

Если вы вносите какие-либо изменения в эти параметры конфигурации, повторно выполняете всего предыдущего Советника по вопросам Рабочего процесса задачи.

Установите параметры, которые влияют на полную генерацию кода.

Задача Set Basic Options устанавливает опции, которые являются основным принципом генерации HDL-кода. Эти опции включают выбор DUT и выбор выходного языка. Основные опции совпадают с найденными в панели HDL Code Generation верхнего уровня диалогового окна Configuration Parameters, за исключением того, что группа Code generation output не использована.

Установите параметры, которые задают разделы, которые вы хотите видеть в Отчете Генерации кода.

Опции - то же самое как найденные в HDL Code Generation> панель Report диалогового окна Configuration Parameters и Model Explorer.

Установите параметры, которые задают подробные характеристики сгенерированного кода.

Расширенные настройки совпадают с найденными в HDL Code Generation> панель Global Settings диалогового окна Configuration Parameters и Model Explorer.

Установите параметры, которые задают оптимизацию, такую как разделение ресурсов и конвейерно обрабатывающий, чтобы улучшить область и синхронизацию.

Опции оптимизации совпадают с найденными в HDL Code Generation> панель Target and Optimizations диалогового окна Configuration Parameters и Model Explorer.

Установите опции, которые определяют характеристики сгенерированного кода испытательного стенда.

Опции испытательного стенда совпадают с найденными в HDL Code Generation> панель Test Bench диалогового окна Configuration Parameters и Model Explorer.

Сгенерируйте код RTL и высокоуровневую обертку HDL.

Задача Generate RTL Code генерирует код RTL и высокоуровневую обертку HDL для подсистемы DUT. Это также генерирует ограничительный файл, который содержит информацию об отображении контакта и ограничения часов.

Выберите и инициируйте генерацию кода RTL, испытательного стенда RTL и cosimulation модели.

Задача Generate RTL Code and Testbench позволяет выбрать, какой код или модель, которую вы хотите сгенерировать. Можно выбрать любую комбинацию следующего:

Generate RTL code: Сгенерируйте код RTL на выходном языке.

Generate test bench: Сгенерируйте испытательный стенд (стенды), выбранный в Set Testbench Options.

Generate validation model: Сгенерируйте модель валидации, которая подсвечивает сгенерированные задержки и другие различия между вашей исходной моделью и сгенерированной cosimulation моделью. С моделью валидации можно наблюдать эффекты потоковой передачи, разделения ресурсов и балансировки задержки.

Модель валидации содержит DUT из исходной модели и DUT из сгенерированной cosimulation модели. Используя модель валидации, можно проверить, что выход оптимизированного DUT битно-верен для результатов, приведенных исходным DUT.

Генерация модели Simulink для Cosimulation с симулятором HDL (Filter Design HDL Coder).

Запустите этот шаг, чтобы проверить сгенерированный HDL с помощью cosimulation между симулятором HDL и испытательным стендом Simulink. Этот шаг показывает, только если вы выбрали Cosimulation model и задали симулятор HDL в Set Testbench Options.

Выберите и инициируйте генерацию кода RTL и пользовательского ядра IP.

В задаче Generate RTL Code and IP Core задайте характеристики сгенерированного ядра IP:

IP core name: Введите имя ядра IP.

Эта установка сохранена с моделью как IPCoreName Свойство блока HDL для блока DUT.

IP core version: Введите номер версии ядра IP. HDL Coder добавляет номер версии к имени ядра IP, чтобы сгенерировать выходное имя папки.

Эта установка сохранена с моделью как IPCoreVersion Свойство блока HDL для блока DUT.

IP core folder (не доступный для редактирования): HDL Coder генерирует файлы ядра IP в выходной показанной папке, включая документацию HTML.

IP repository: Если вы имеете папку репозитория IP, вводите ее путь вручную или при помощи кнопки Browse. Кодер копирует сгенерированное ядро IP в папку репозитория IP.

Additional source files: Если вы используете интерфейс черного квадрата в своем проекте, чтобы включать существующий Verilog® или VHDL® код, введите имена файлов. Введите вручную каждое имя файла, разделенное точкой с запятой (;), или при помощи кнопки Add. Язык исходного файла должен совпадать с вашим выходным языком.

Эта установка сохранена с моделью как IPCoreAdditionalFiles Свойство блока HDL для блока DUT.

FPGA Data Capture buffer size: Задайте размер памяти в сгенерированном ядре IP. Ширина памяти является общей битной шириной сигналов данных. Buffer size использует значения, равные 128* (2n), где n является целым числом. По умолчанию buffer size является 128 (n = 0). Максимальным значением n является 13, что означает, что максимальное значение для buffer size равняется 128* (213) = 1048576.

Эта установка сохранена с моделью как IPDataCaptureBufferSize Свойство блока HDL для блока DUT.

FPGA Data Capture maximum sequence depth: Задайте максимальную глубину последовательности, чтобы собрать данные от FPGA на одном или нескольких триггерных этапах. Максимальная глубина последовательности является целым числом, которое лежит в диапазоне от 1 до 10. По умолчанию максимальной глубиной последовательности является 1. Чтобы собрать заданные данные путем обеспечения набора триггерных условий на нескольких этапах, установите максимальную глубину последовательности на значение, больше, чем 1.

Эта установка сохранена с моделью как IPDataCaptureSequenceDepth Свойство блока HDL для блока DUT.

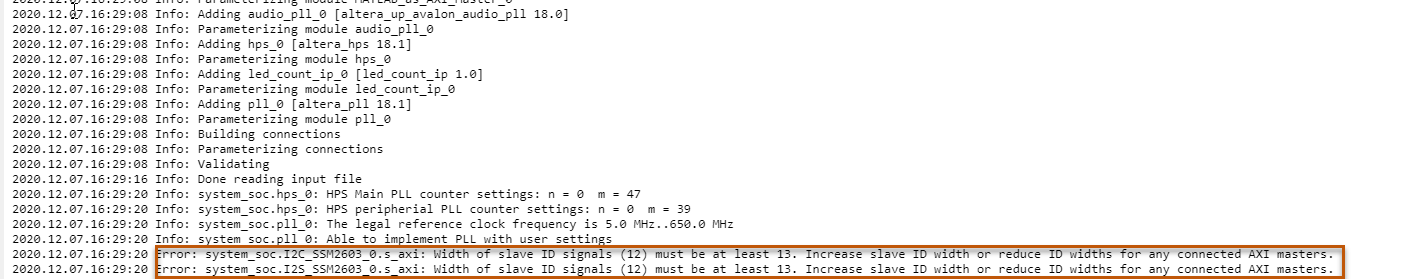

Когда вы выбираете Insert JTAG MATLAB as AXI Master, значение AXI4-Slave ID Width настроено для ядра IP DUT, которое генерирует HDL Coder. Когда вы выбираете Insert JTAG MATLAB as AXI Master и добавляете пользовательского дюйм/с, необходимо задать новое настроенное ведомое значение ширины ID. Например, когда вы выбираете Insert JTAG MATLAB as AXI Master и добавляете пользовательского дюйм/с, если вы получаете это сообщение об ошибке во время задачи Create Project:

Регенерируйте ядра IP путем установки целевой платформы или как Типового Intel или как Типового Xilinx. Затем сопоставьте один из портов DUT к интерфейсу AXI4, вычислите новую ширину при помощи New width = Base Width + log2(Number of AXI Masters +1), и введите расчетное значение ширины в AXI4 Slave ID width. Добавьте регенерированные ядра IP с новыми значениями ширины к папке исходного проекта. Щелкните правой кнопкой по Create Project и выберите Run to Selected Task. В этом примере два пользовательских дюйм/с I2C и I2s. Новая расчетная ширина равняется 13.

Generate IP core report: Оставьте эту опцию выбранной, чтобы сгенерировать документацию HTML для ядра IP.

Enable readback on AXI4 slave write registers: Выберите эту опцию, если вы хотите считать назад значение, которое записано в ведомые регистры AXI4 при помощи ведомого интерфейса AXI4. Когда вы запускаете эту задачу, генератор кода добавляет мультиплексор для каждого регистра AXI4 в логике дешифратора адреса. Этот мультиплексор сравнивает адрес, что данные записаны в при чтении значений. Если вы читаете из нескольких ведомых регистров AXI4, readback логика становится длинной цепью мультиплексора, которая может влиять на частоту синтеза.

Эта установка сохранена с моделью как AXI4RegisterReadback Свойство блока HDL для блока DUT.

Generate default AXI4 slave interface: Оставьте эту опцию выбранной, если вы хотите сгенерировать ядро IP HDL с ведомым интерфейсом AXI4 для сигналов, таких как часы, сбросьте, подготовьте, установите метку времени и так далее. Если вы хотите сгенерировать типовое ядро IP HDL без каких-либо ведомых интерфейсов AXI4, снимите этот флажок. Кроме того, убедитесь, что вы не сопоставляете ни одного из портов DUT к AXI4 или AXI4-облегченным интерфейсам. Можно только сопоставить порты с Внешними или Внутренними интерфейсами IO или интерфейсом AXI4-Stream с отображением TLAST.

Эта установка сохранена с моделью как GenerateDefaultAXI4Slave Свойство блока HDL для блока DUT.

Expose DUT clock enable input port: Выберите эту опцию, если вы хотите отсоединить часы DUT, включают входной порт. Триггер DUT от восходящего дюйм/с при помощи часов включает входной порт. Если ваш проект имеет какие-либо порты, сопоставленные с интерфейсом AXI4 Slave, эта опция отключена.

Expose DUT cock enable output port: Выберите эту опцию, если вы хотите отсоединить часы, включают выходной порт к нисходящему дюйм/с. Управляйте или синхронизируйтесь, нисходящий пользовательский дюйм/с при помощи часов включают выходной порт.

Создайте проекты для поддерживаемых инструментов синтеза FPGA, выполните синтез FPGA, отображение и задачи места/маршрута, и аннотируйте критические пути в исходной модели

Задачи в папке FPGA Synthesis and Analysis включают вам к:

Создайте проекты синтеза FPGA для поддерживаемых инструментов синтеза FPGA.

Запустите поддерживаемые инструменты синтеза FPGA, с помощью файлов проекта, чтобы выполнить синтез, отображение и задачи места/маршрута.

Аннотируйте свою исходную модель информацией о критическом пути, полученной из инструментов синтеза.

Для списка поддерживаемых сторонних инструментов синтеза смотрите Сторонние Инструменты Синтеза и Поддержку версии.

Задачи в папке:

Create Project

Perform Synthesis and P/R

Annotate Model with Synthesis Result

Создайте проект синтеза FPGA для поддерживаемого инструмента синтеза FPGA.

Эта задача создает проект синтеза для выбранного инструмента синтеза и загружает проект с HDL-кодом, сгенерированным для вашей модели.

Когда создание проекта завершается, HDL Workflow Advisor отображает ссылку на проект на правой панели. Щелкните по этой ссылке, чтобы просмотреть проект в окне проекта инструмента синтеза.

Выберите цель синтеза сгенерировать специфичную для инструмента оптимизацию команды Tcl для вашего проекта. Если вы задаете None, никакие команды Tcl не сгенерированы.

Чтобы изучить, как цели синтеза сопоставляют с командами Tcl, смотрите Цель Синтеза к Отображению Команды Tcl.

Введите дополнительные исходные файлы HDL, которые вы хотите включенный в ваш проект синтеза. Введите вручную каждое имя файла, разделенное точкой с запятой (;), или при помощи кнопки Add Source.

Например, можно включать исходные файлы HDL (.vhd или.v) или ограничительный файл (.ucf или .sdc).

Введите дополнительное создание проекта файлы Tcl, которые вы хотите включать в свой проект синтеза. Введите вручную каждое имя файла, разделенное точкой с запятой (;), или при помощи кнопки Add Tcl.

Например, можно включать скрипт Tcl (.tcl), чтобы выполниться после создания проекта.

Запустите поддерживаемые инструменты синтеза FPGA, чтобы выполнить синтез, отображение и задачи места/маршрута.

Задачи в папке Perform Synthesis and P/R позволяют вам запустить поддерживаемый инструмент синтеза FPGA и:

Синтезируйте сгенерированный HDL-код.

Выполните отображение и синхронизацию анализа.

Выполните место и направьте функции.

Для списка поддерживаемых сторонних инструментов синтеза смотрите Сторонние Инструменты Синтеза и Поддержку версии.

Запустите поддерживаемый инструмент синтеза FPGA и синтезируйте сгенерированный HDL-код.

Задача Perform Logic Synthesis:

Запускает инструмент синтеза в фоновом режиме.

Открывает ранее сгенерированный проект синтеза, компилирует HDL-код, синтезирует проект и испускает списки соединений и связанные файлы.

Отображается синтез входят в систему подпанель Result.

Запуски поддержали инструмент синтеза FPGA и сопоставляют синтезируемое логическое проектирование с целевым FPGA.

Задача Perform Mapping:

Запускает инструмент синтеза в фоновом режиме.

Запускает процесс отображения, который сопоставляет синтезируемое логическое проектирование с целевым FPGA.

Испускает файл описания схемы для использования в фазе маршрута и месте.

Также испускает время выполнения перед маршрутизацией для использования в анализе критического пути и обратной корректировке проекта вашей исходной модели.

Отображает журнал в подпанели Result.

Включите Skip pre-route timing analysis, если ваш инструмент не поддерживает рано синхронизирующую оценку. Когда эта опция включена, задача Annotate Model with Synthesis Result устанавливает Critical path source на post-route.

Запускает инструмент синтеза в фоновом режиме и запускает процесс Места и Маршрута.

Задача Perform Place and Route:

Запускает инструмент синтеза в фоновом режиме.

Запускает процесс Места и Маршрута, который берет описание схемы, произведенное предыдущим процессом отображения, и испускает описание схемы, подходящее для программирования FPGA.

Также испускает время выполнения постмаршрутизации для использования в анализе критического пути и обратной корректировке проекта вашей исходной модели.

Отображает журнал в подпанели Result.

Совет

Если вы выбираете Skip this task, HDL Workflow Advisor выполняет рабочий процесс, но не использует задачу Perform Place and Route, отмечая его Passed. Вы можете хотеть выбрать Skip this task, если вы предпочитаете делать, место и маршрут работают вручную.

Совет

Если Perform Place and Route перестал работать, но вы хотите использовать результаты синхронизации постотображения найти критические пути в вашей модели, можно выбрать Ignore place and route errors и продолжить к задаче Annotate Model with Synthesis Result.

Запуски Xilinx® Vivado® и выполняет шаг Synthesis Vivado.

Включите Skip pre-route timing analysis, если вы не хотите делать рано синхронизирующую оценку.

Запуски Xilinx Vivado и выполняют шаг Implementation Vivado.

Если вы выбираете Skip this task , HDL Workflow Advisor не использует задачу Run Implementation, отмечая его Passed. Выберите Skip this task , если вы предпочитаете делать, место и маршрут работают вручную.

Если Run Implementation перестал работать, можно выбрать Ignore place and route errors и продолжить к задаче Annotate Model with Synthesis Result.

Если там синхронизируют отказы во время этой задачи, задача не перестала работать. Необходимо проверять отчет синхронизации на синхронизацию отказов.

Анализирует пред - или время выполнения постмаршрутизации и визуально подсвечивает критические пути в вашей модели.

Задача Annotate Model with Synthesis Result помогает вам идентифицировать критические пути в своей модели. По вашей опции задача анализирует пред - или время выполнения постмаршрутизации, произведенное исследовательской группой Perform Synthesis and P/R, и визуально подсвечивает один или несколько критических путей в вашей модели.

Примечание

Если вы выбираете Intel Quartus Pro или Microsemi Libero SoC как Synthesis tool, задача Annotate Model with Synthesis Result не доступна. В этом случае можно запустить рабочий процесс к синтезу и затем просмотреть отчеты синхронизации, чтобы видеть критический путь.

Если Generate FPGA top level wrapper выбран в задаче Generate RTL Code and Testbench, Annotate Model with Synthesis Result не доступен. Чтобы выполнить анализ обратной корректировки проекта, снимите флажок для Generate FPGA top level wrapper.

Выберите pre-route или post-route.

Опция pre-route недоступна, когда Skip pre-route timing analysis включен в предыдущей исследовательской группе.

Можно аннотировать до 3 критических путей. Выберите количество путей, которые вы хотите аннотировать.

Покажите критические пути, включая дублирующиеся пути.

Покажите только первую инстанцию пути, который дублирован.

Аннотируйте совокупную задержку синхронизации на каждом пути.

Покажите конечные точки каждого пути, но не используйте соединяющиеся сигнальные линии.

Когда задача Annotate Model with Synthesis Result выполнение до завершения, HDL Coder отображает DUT с подсвеченной информацией о критическом пути.

Папка Download to Target поддерживает следующие задачи:

Generate Programming File: Сгенерируйте файл программирования FPGA.

Program Target Device: Загрузите сгенерированный файл программирования на целевую макетную плату.

Generate Simulink Real-Time Interface (только для целевых устройств Speedgoat): Сгенерируйте модель, которая содержит подсистему интерфейса Simulink Real-Time.

Для итоговой информации о каждой задаче Download to Target выберите значок задачи и затем нажмите кнопку HDL Workflow Advisor Help.

Задача Generate Programming File генерирует файл программирования FPGA, который совместим с выбранным целевым устройством.

Задача Program Target Device загружает сгенерированный файл программирования FPGA на выбранное целевое устройство.

Прежде, чем выполнить задачу Program Target Device, убедитесь, что ваш PC хоста правильно соединяется с целевой макетной платой через необходимый кабель программирования.

Задача Generate Simulink Real-Time Interface генерирует модель, содержащую интерфейсную подсистему, которую можно включить к модели Simulink Real-Time.

Соглашение о присвоении имен для сгенерированной модели:

gm_fpgamodelname_slrt

где fpgamodelname имя исходной модели.

Можно сохранить текущие настройки HDL Workflow Advisor к именованному restore point. Позже, можно восстановить те же настройки путем загрузки данных о точке восстановления в HDL Workflow Advisor.

Установите опции FIL и запустите обработку FIL.

Установите тип подключения, IP платы и Мак адреса и выберите дополнительные файлы при необходимости.

Выберите JTAG (Altera® только платы) или Ethernet.

Используйте эту опцию для установки IP-адреса платы, если это не IP-адрес по умолчанию (192.168.0.2).

При большинстве обстоятельств вы не должны изменять Мак адрес Совета. Необходимо будет сделать так, если вы соедините больше чем одну макетную плату FPGA с одиночным компьютером (для которого у вас должен быть отдельный NIC для каждой платы). Необходимо изменить Мак адрес Совета для дополнительных плат так, чтобы каждый адрес был уникален.

Выберите дополнительные исходные файлы для проекта HDL, который должен быть проверен на плате FPGA при необходимости. HDL Workflow Advisor пытается идентифицировать тип файла; измените тип файла в столбце File Type, если это неправильно.

Во время процесса сборки происходят следующие действия:

FPGA в цикле генерирует блок FIL, названный в честь модуля верхнего уровня, и помещает его в новую модель.

После новой генерации модели FIL открывает командное окно. В этом окне программное обеспечение проекта FPGA выполняет синтез, подгонку, место-и-маршрут, синхронизируя анализ и FPGA, программируя генерацию файла. Когда процесс завершается, сообщение в командных строках вы, чтобы закрыть окно.

FPGA в цикле создает тестовую модель вокруг сгенерированного блока FIL.

Модель должна иметь два входных порта и два выходных порта 16-битных сигналов со знаком.

Этот шаг инициирует FPGA, программируя создание файла. Для Входных Параметров войдите, путь к FPGA Ettus Research™ USRP™ регистрирует, вы ранее загрузили. Если вы еще не загрузили эти файлы, смотрите Пакет поддержки для Радио-документации USRP.

Когда этот шаг завершится, см. инструкции для загрузки файла программирования к FPGA и выполнению симуляции в Пакете поддержки для Радио-документации USRP для Предназначения FPGA.

DUT должен придерживаться определенных интерфейсных требований сигнала. Во время Проверки Совместимость SDR следующие интерфейсные проверки выполнены (Вводы и выводы проходят те же проверки).

Должен включать один комплексный сигнал, два скалярных сигнала или один векторизованный сигнал размера 2

Должен иметь bitwidth 16

Должен быть подписан

Должен быть один уровень

Если векторизовали порты, должен использовать опцию Векторов Scalarize

Если имеют несколько уровней, должен использовать Одни часы

Должен использовать синхронный сброс

Должен использовать возбуждаемый высоким уровнем сигнала сброс

Должен использовать пользователя, разгоняющего фактор 1

Все проверки на ошибки делают для данного шанса задачи и сообщают в таблице. Это позволяет одной итерации фиксировать все ошибки.

FPGA SDR интегрирует потребительскую логику, как сгенерировано на предыдущих шагах, а также SDR-специфичном коде, чтобы обеспечить данные и пути к управлению между платой RF и хостом.

Этот шаг состоит из следующих задач:

Установите Опции SDR: Выберите опции настройки.

Создайте SDR: Сгенерируйте файл программирования FPGA для цели SDR.

Выберите опции настройки для завершения реализации FPGA SDR.

RF board for target

Выберите одно из следующего:

Epic Bitshark FMC-1Rx RevB

Epic Bitshark FMC-1Rx RevC

Folder with vendor HDL source code

Задайте папку, которая содержит HDL интерфейса RF, загруженный с сайта поддержки поставщика. Используйте Browse, чтобы перейти к правильной папке.

User logic synthesis frequency

Задайте максимальную частоту, на которой вы хотите запустить свой проект. Это значение должно быть больше частот дискретизации для ADC и DAC, как задано в блоке ADI FMCOMMS или Epiq Bitshark™.

User logic data path

Выберите Receiver data path или Transmitter data path.

Board IP address

Установите IP-адрес платы в этом поле, если это не IP-адрес по умолчанию (192.168.10.1).

Board MAC address

При большинстве обстоятельств вы не должны изменять Мак адрес Совета. Однако необходимо сделать так, если вы соединяете больше чем одну макетную плату FPGA с одиночным компьютером (для которого у вас должен быть отдельный NIC для каждой платы). Необходимо изменить Мак адрес Совета для дополнительных плат так, чтобы каждый адрес был уникален.

Задайте файлы, которые вы хотите включенный в проект ISE или Vivado. Необходимо включать только типы файлов, поддержанные ISE или Vivado. Если включенный файл не существует, HDL Workflow Advisor не может создать проект.

File: Имя файла добавляется к проекту (с Add).

FileType : FileType . Программное обеспечение попытается определить тип файла автоматически, но можно заменить выбор. Опциями является VHDL, Verilog, EDIF netlist, VQM netlist, QSF fileОграничения, и Others.

Добавление: Добавьте новый файл в список.

Удаление: Удаляет в настоящее время выбранный файл из списка.

Up: Перемещает в настоящее время выбранный файл список.

Down: Перемещается в настоящее время выбранный, спиливают список.

Show full paths to source files (флажок): Инициировал отображение полного пути. Отъезд этого поля снял флажок с отображениями только имя файла.

HDL Workflow Advisor создает новый Xilinx ISE или проект Vivado и добавляет следующее:

Все необходимые файлы от репозитория FPGA

Сгенерированные файлы HDL для выбранной подсистемы и алгоритма

Если никакие ошибки не найдены во время генерации проекта FPGA и проверки синтаксиса, FPGA, программируя процесс генерации файла запускается. Можно просмотреть этот процесс во внешнем командном процессоре и контролировать его прогресс. Когда процесс закончен, сообщение в командном окне предлагает вам закрывать окно.

Задачи в этой папке интегрируют ваше сгенерированное ядро IP HDL со встраиваемым процессором.

Создайте проект для инструмента встраиваемой системы.

В окне сообщения, после того, как сгенерирован проект, можно щелкнуть по ссылке проекта, чтобы открыть сгенерированный проект инструмента встраиваемой системы.

Встроенный Design Tool.

Папка, где ваши сгенерированные файлы проекта сохранены.

Выберите цель синтеза сгенерировать специфичную для инструмента оптимизацию команды Tcl для вашего проекта. Если вы задаете None, никакие команды Tcl не сгенерированы.

Чтобы изучить, как цели синтеза сопоставляют с командами Tcl, смотрите Цель Синтеза к Отображению Команды Tcl.

Сгенерируйте модель программного интерфейса или скрипт или обоих с блоками драйверов ядра IP для встроенной генерации кода C.

Если у вас нет Embedded Coder® пакет аппаратной поддержки для требуемой платы установил, эта опция не будет доступна. Например, если плата целевого компьютера является устройством Zynq, у вас должен быть Пакет поддержки Embedded Coder для Xilinx Zynq® Платформа установлена.

После того, как вы сгенерируете модель программного интерфейса, можно сгенерировать код С от нее с помощью Embedded Coder. Скрипт содержит команды, которые позволяют вам соединиться с целевым компьютером, и записать в или читать из сгенерированного ядра IP при помощи блоков драйверов AXI.

Когда вы очищаете обоих флажки Generate Simulink software interface model и Generate MATLAB software interface script, эта задача пропущена.

Operating system: Выберите свою целевую операционную систему.

Сгенерируйте поток битов для встраиваемой системы.

Позвольте этой опции запустить процесс сборки параллельно с MATLAB®. Если эта опция отключена, вы не можете использовать MATLAB, пока сборка не закончена. Эта опция только допустима, когда вы используете IP Core Generation рабочий процесс.

Чтобы настроить вашу сборку синтеза, сохраните свои пользовательские команды Tcl в файле и выберите Custom. Введите путь к файлу вручную или при помощи кнопки Browse. Содержимое вашего пользовательского файла Tcl вставляется между командами Tcl, которые открывают и закрывают проект.

Если вы выбираете Custom и хочу сгенерировать поток битов, генерация потока битов, которую команда Tcl должна отослать к главному названию и местоположению обертки файла или непосредственно или неявно. Например, следующая команда Xilinx Vivado Tcl генерирует поток битов и неявно относится к главному имени файла и местоположению:

launch_runs impl_1 -to_step write_bitstream

Выберите эту опцию, чтобы ускорить время генерации потока битов при помощи контрольной точки проекта от предыдущей сборки. Эта опция доступна только при использовании инструмента синтеза Xilinx Vivado.

Чтобы использовать эту опцию, выберите Enable routed design checkpoint for build. Использовать значение по умолчанию направило файл контрольной точки проекта, выберите Default. Расположением файла по умолчанию является hdl_prj\checkpoint\system_routed.dcp. Чтобы использовать пользовательский направленный файл контрольной точки проекта, выберите Custom и обеспечьте путь к файлу к своему пользовательскому расположению файла. Эта опция доступна только при использовании инструмента синтеза Xilinx Vivado.

Чтобы использовать эту опцию, выберите Custom для Routed design checkpoint file for build. Используйте эту опцию, чтобы указать на ваш пользовательский направленный файл контрольной точки проекта. После того, как генерация потока битов завершается, новый направленный файл проекта контрольной точки будет записан в местоположение, заданное в Routed design checkpoint file. Эта опция доступна только при использовании инструмента синтеза Xilinx Vivado.

Уменьшайте времена генерации потока битов при помощи нескольких логических ядер PC. Используйте эту опцию, чтобы выбрать максимальное количество ядер PC, чтобы использовать. Выбор synthesis tool default выбирает максимальное количество набора ядер в инструменте синтеза. Чтобы вручную выбрать максимальное количество ядер выбирают между 2 и 32.

Программируйте соединенное целевое устройство SoC. Задайте Programming method для целевого устройства:

JTAG: Использует кабель JTAG, чтобы программировать целевое устройство SoC.

Download: Это - Programming method по умолчанию. Копирует сгенерированный поток битов FPGA, дерево устройств и системные скрипты инициализации к SD-карте на плате Zynq, и сохраняет поток битов на SD-карте постоянно. Чтобы использовать этот метод программирования, вы не требуете лицензии Embedded Coder. Можно создать объект SSH путем определения IP Address, SSH Username и SSH Password. HDL Coder использует копируемый объект SSH поток битов для SD-карты, и повторно программируйте плату.

Чтобы задать вашу собственную функцию, чтобы программировать целевое устройство в вашем пользовательском исходном проекте, можно использовать Custom

Programming method. Чтобы использовать пользовательское программирование, укажите указатель на функцию пользовательской функции программирования использование CallbackCustomProgrammingMethod метод hdlcoder.ReferenceDesign класс. Например:

hRD.CallbackCustomProgrammingMethod = ...

@parameter_callback.callback_CustomProgrammingMethod;Для получения дополнительной информации смотрите Целевые Советы FPGA Программы или Устройства SoC.