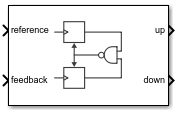

Детектор фазы/частоты, который сравнивает фазу и частоту между двумя сигналами

Mixed-Signal Blockset / PLL / Базовые блоки

Блок PFD производит два выходных импульса, которые отличаются по рабочему циклу. Различие в рабочем цикле пропорционально разности фаз между входными сигналами. В схемах синтезатора частоты, таких как фазовая подстройка частоты (PLL), блок PFD сравнивает фазу и частоту между опорным сигналом и сигналом, сгенерированным блоком VCO, и определяет ошибку фазы.

reference — Ссылочная частотаInput port, который передает ссылочную частоту, чтобы определить ошибку фазы.

Типы данных: double

feedback — Частота обратной связиВыходной порт, который передает частоту обратной связи, чтобы определить ошибку фазы. В системе PLL выход VCO возвращен через порт feedback к PFD после прохождения через делитель часов.

Типы данных: double

up — Частота ссылки передачВыходной порт, который передает ссылочную частоту к Charge Pump, чтобы преобразовать ошибку фазы в ток. Различие в рабочем цикле сигналов в портах up и down пропорционально разности фаз между сигналами в портах reference и feedback.

Типы данных: double

down — Частота обратной связи передачВыходной порт, который передает частоту обратной связи к Charge Pump, чтобы преобразовать ошибку фазы в ток. Различие в рабочем цикле сигналов в портах up и down пропорционально разности фаз между сигналами в портах reference и feedback.

Типы данных: double

Deadband compensation (s) — Задержка, добавленная для активного выхода около, обнуляет возмещенную фазу30e-12 (значение по умолчанию) | положительный действительный скалярЗадержка, добавленная для активного выхода около, обнуляет фазу, возмещенную в виде положительного действительного скаляра в секундах. Мертвая зона является полосой смещения фазы около нулевого смещения фазы, для которого PFD выход незначителен.

Использование get_param(gcb,'DeadbandCompensation') просмотреть текущее значение Deadband compensation.

Использование set_param(gcb,'DeadbandCompensation',value) установить up Rise/fall time на определенное значение.

Типы данных: double

Enable increased buffer size — Включите увеличенный buffer sizeВыберите, чтобы включить увеличенный buffer size в процессе моделирования. Это увеличивает buffer size Variable Pulse Delay, Logic Decision и блоков Slew Rate в блоке PFD. По умолчанию эта опция является невыбранной.

Buffer size — Количество отсчетов буферизации ввода, доступной в процессе моделированияКоличество отсчетов буферизации ввода, доступной в процессе моделирования в виде положительного целочисленного скаляра. Это устанавливает buffer size Variable Pulse Delay, Logic Decision и блоков Slew Rate в блоке PFD.

Выбор различного решателя симуляции или выборка стратегий могут измениться, количество входных выборок должно было произвести точную выходную выборку. Установите Buffer size на достаточно большое значение так, чтобы входной буфер содержал все входные требуемые выборки.

Этот параметр только доступен, когда опция Enable increased buffer size выбрана во вкладке Configuration.

Использование get_param(gcb,'NBuffer') просмотреть текущее значение Buffer size.

Использование set_param(gcb,'NBuffer',value) установить Buffer size на определенное значение.

Типы данных: double

Enable impairments — Ухудшения схемы сложения к симуляцииВыберите к ухудшениям схемы сложения, таким как повышение/время спада и задержка распространения с симуляцией. По умолчанию эта опция выбрана.

Output step size calculation — Определите, как выходной размер шага вычисляетсяDefault (значение по умолчанию) | AdvancedОпределите, как выходной размер шага вычисляется:

Выберите Default вычислить выходной размер шага от повышения/времени спада. Выведите размер шага (ΔT), дают .

Выберите Advanced вычислить выходной размер шага от максимальной частоты интереса. Выведите размер шага (ΔT), дают .

Чтобы включить этот параметр, выберите Enable Impairments во вкладке Impairments.

Maximum frequency of interest (Hz) — Максимальная частота интереса при выходе10e9 (значение по умолчанию) | положительный действительный скалярМаксимальная частота интереса при выходе в виде положительного действительного скаляра в Гц.

Чтобы включить этот параметр, выберите Enable Impairments во вкладке Impairments и выберите Advanced for Output step size calculation.

Использование get_param(gcb,'MaxFreqInterest') просмотреть текущее значение Maximum frequency of interest (Hz).

Использование set_param(gcb,'MaxFreqInterest',value) установить Maximum frequency of interest (Hz) на определенное значение.

Типы данных: double

Rise/fall time (s) — 20%-й - 80% повышение/время спада для выходного порта PFD3e-11 (значение по умолчанию) | положительный действительный скаляр20%-й - 80% повышение/время спада для выходного порта PFD в виде положительного действительного скаляра в секундах.

Чтобы включить этот параметр, выберите Enable Impairments во вкладке Impairments.

Использование get_param(gcb,'RiseFallTime') просмотреть текущее значение Rise/fall time (s).

Использование set_param(gcb,'RiseFallTime',value) установить Impairments на определенное значение.

Типы данных: double

Propagation Delay (s) — Задержитесь от входного порта до выходного порта PFD50e-12 (значение по умолчанию) | положительный действительный скалярЗадержитесь от входного порта до выходного порта PFD в виде положительного действительного скаляра в секундах.

Чтобы включить этот параметр, выберите Enable Impairments во вкладке Impairments.

Использование get_param(gcb,'PropDelay') просмотреть текущее значение Propagation Delay (s).

Использование set_param(gcb,'PropDelay',value) установить Propagation Delay (s) на определенное значение.

Типы данных: double

PFD состоит из двух синхронных D-триггеров. Ссылка и сигналы обратной связи, полученные в соответствующих портах, действуют как триггер. Выходные параметры двух триггеров проходят через логический элемент НЕ-И, который действует как сигнал сброса. Импульсная задержка введена после логического элемента НЕ-И с помощью блока Variable Pulse Delay, чтобы компенсировать мертвую зону.

Ухудшения содержатся в различных подсистемах и активируются, когда ухудшения включены. Подсистема ухудшения использовала блок Slew Rate, чтобы реализовать задержку повышения/времени спада и распространения.

[1] Бэнерджи, декан. Эффективность PLL, симуляция и проект. Индианаполис, IN: Dog Ear Publishing, 2006.

Charge Pump | Fractional Clock Divider with Accumulator | Fractional Clock Divider with DSM | Single Modulus Prescaler | Dual Modulus Prescaler

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.