Задайте доказательство или цели тестирования, не влияя на результаты симуляции или сгенерированный код

Simulink Design Verifier

Этот блок является блоком Subsystem, который предварительно сконфигурирован, чтобы служить начальной точкой для создания подсистемы, которая задает доказательство или цели тестирования для использования с Simulink® Программное обеспечение Design Verifier™.

Программное обеспечение Simulink Coder™ игнорирует блоки Subsystem Верификации во время генерации кода, ведя себя, как будто подсистемы не существуют. Блок Verification Subsystem позволяет вам добавлять компоненты Simulink Design Verifier в модель, не влияя на ее сгенерированный код.

Примечание

Если блок Verification Subsystem содержит блоки, которые зависят от абсолютного времени, и вы выбираете ERT-based target (Simulink Coder) для генерации кода, устанавливаете программную среду на абсолютное время. Откройте диалоговое окно Configuration Parameters. В Code Generation> панель Interface под Software environment, выберите absolute time. Не выбирайте continuous time. Для получения дополнительной информации об этой установке смотрите Поддержку: абсолютное время (Embedded Coder).

При сборе покрытия модели программное обеспечение Simulink Coverage™ только записывает покрытие для блоков Simulink Design Verifier в блоке Subsystem Верификации; это не записывает покрытие ни для каких других блоков в Подсистеме Верификации.

Создать Подсистему Верификации в вашей модели:

Скопируйте блок Subsystem Верификации с библиотеки Simulink Design Verifier в вашу модель.

Откройте блок Subsystem Верификации путем двойного клика по нему.

В окне Verification Subsystem добавьте блоки, которые задают доказательство или цели тестирования. Используйте блоки Inport, чтобы представлять вход снаружи подсистемы.

Блок Subsystem Верификации в библиотеке Simulink Design Verifier предварительно сконфигурирован, чтобы работать с программным обеспечением Simulink Design Verifier. Блок Subsystem Верификации должен:

Не содержите блоки Outport.

Включите его параметр Treat as Atomic Unit.

Задайте его параметр Mask type как VerificationSubsystem.

Если вы изменяете блок Subsystem Верификации так, чтобы предыдущие условия не соблюдали, программное обеспечение Simulink Design Verifier выводит предупреждение.

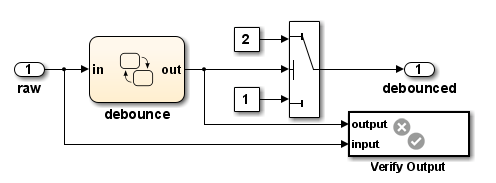

sldvdemo_debounce_validprop модель в качестве примера включает Подсистему Верификации под названием Verify Output, как показано в изображении ниже.

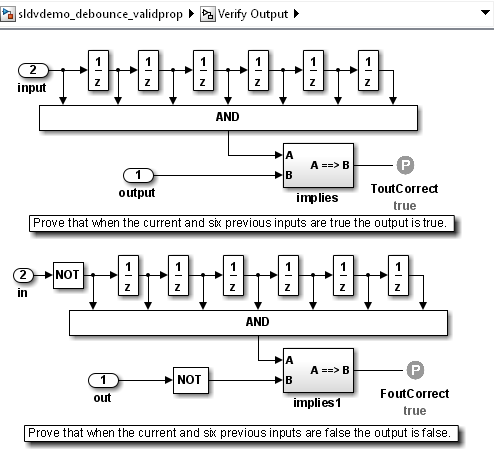

Подсистема Verify Output задает две цели доказательства, детализированные в следующем изображении.

Блок Subsystem в документации Simulink