С Simulink® Design Verifier™, можно анализировать модели Simulink к:

Обнаружьте ошибки проектирования, которые могут произойти подряд время.

Сгенерируйте тесты, которые достигают покрытия модели.

Докажите свойства и идентифицируйте нарушения свойства.

Прежде чем Simulink Design Verifier анализирует модель, проверки программного обеспечения, совместима ли модель для анализа. Модель совместима для анализа когда:

Модель скомпилирована в исполняемую форму.

Модель совместима с генерацией кода.

Модель выполняет нулевую вторую симуляцию без ошибок, которая является симуляцией, запускаются, и временем остановки является 0.

Программное обеспечение поддерживает широкий диапазон Simulink и Stateflow® программные возможности в ваших моделях. Однако существуют возможности, которые продукт не поддерживает, описанный в Ограничениях Поддержки для Программных функций Simulink и Ограничениях Поддержки для Программных функций Stateflow.

Для получения дополнительной информации о поддерживаемых блоках Simulink смотрите Поддерживаемые и Неподдерживаемые блоки Simulink в Simulink Design Verifier.

Прежде чем программное обеспечение начинает анализ, оно проверяет совместимость вашей модели, и затем создает представление модели. Представление модели включает артефакты модели, которые используются во время анализа. Для получения дополнительной информации смотрите Представление Модели для Анализа.

Прежде чем вы запустите анализ, можно осуществить проверку совместимости модели при помощи одного из этих методов. Когда вы используете любой из этих методов, представление модели всегда восстанавливается.

На вкладке Design Verifier, в разделе Analyze, нажимают Check Compatibility.

В Model Advisor выберите By Product> Simulink Design Verifier> Check compatibility with Simulink Design Verifier или By Task> Simulink Design Verifier Compatibility Check> Check compatibility with Simulink Design Verifier. Нажмите Run This Check.

Для получения дополнительной информации смотрите Проверки Simulink Design Verifier.

Осуществлять проверку совместимости программно в командной строке или в MATLAB® программа, используйте sldvcompat функция. Для получения дополнительной информации смотрите sldvcompat.

Чтобы проверять совместимость Subsystem, щелкните правой кнопкой по Subsystem и выберите Design Verifier> Check Subsystem Compatibility.

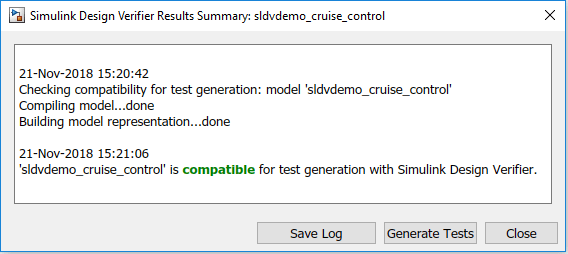

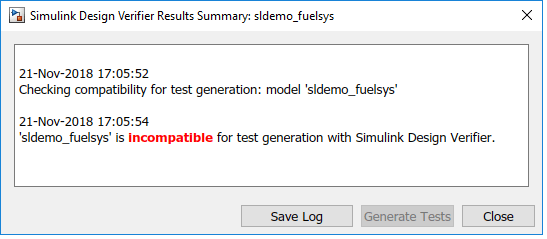

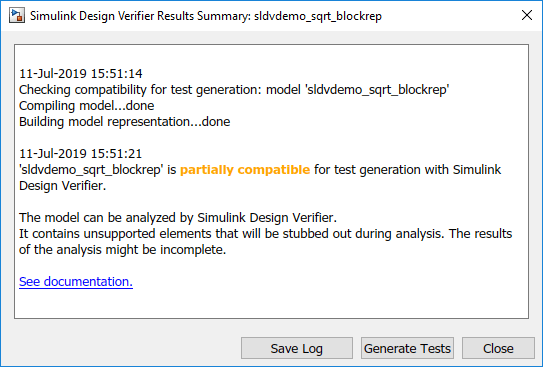

Когда вы осуществляете проверку совместимости модели, окно Results Summary отображает один из этих результатов:

Если ваша модель совместима, можно продолжить анализ в окне Results Summary. Например, чтобы продолжить анализ генерации тестов, нажмите Generate Tests.

Примечание

После того, как вы завершили проверку совместимости, если вы изменяете модель, вы не можете продолжить анализ в окне Results Summary. Если вы изменяете свою модель, повторно выполняете проверку совместимости на анализ.

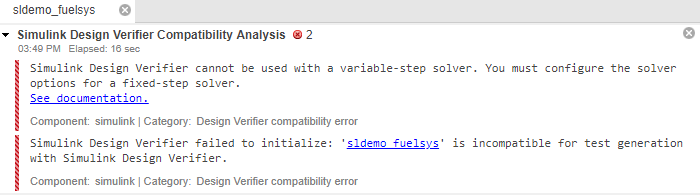

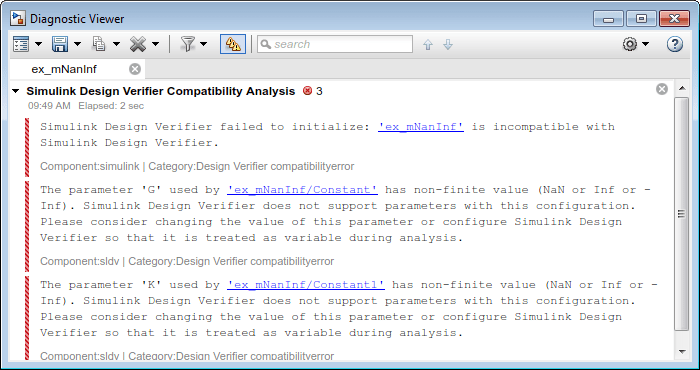

Если модель несовместима с Simulink Design Verifier, можно идентифицировать и зафиксировать несовместимости через Диагностические сообщения Средства просмотра. Для получения дополнительной информации, Диагностика вида на море.

Если ваша модель использует решатель переменного шага, сконфигурируйте Тип решателя к Fixed-step.

Если ваша модель имеет неличные данные, измените значение данных или сконфигурируйте модель так, чтобы данные были обработаны как переменная во время анализа Simulink Design Verifier. Для получения дополнительной информации смотрите Неличные Данные.

Если ваша модель является большой и содержит много подсистем, можно использовать Советника по вопросам Генерации тестов, чтобы определить, вызывают ли определенные подсистемы несовместимость. Для получения дополнительной информации смотрите Советника по вопросам Генерации тестов Использования, чтобы Идентифицировать Поддающиеся анализу Компоненты.

Модель частично совместима, если по крайней мере один объект модели в модели несовместим. Simulink Design Verifier продолжает анализ для частично совместимой модели путем гашения неподдерживаемых элементов. По умолчанию Автоматическое блокирование неподдерживаемой опции блоков и функций установлено в On. Для получения дополнительной информации смотрите Несовместимости Указателя с Автоматическим Блокированием.

Основной рабочий процесс для Simulink Design Verifier | Блокируйте замены для неподдерживаемых блоков | Представление модели для анализа