Используйте Поток от FPGA до шаблона Processor, чтобы создать модель SoC Blockset™ для разработки datapath от оборудования (FPGA) к программному обеспечению (Процессор). Чтобы создать проект с помощью шаблона "Stream to Processor", выполните шаги, чтобы Создать Модель SoC Используя Шаблон SoC Blockset.

Для основанной на выборке обработки не требуются никакие дополнительные продукты.

Для основанной на системе координат обработки требуется DSP System Toolbox™.

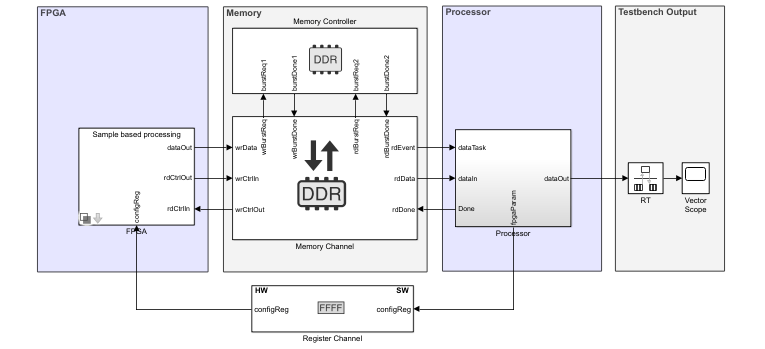

Этот шаблон моделирует счетчик как источник тестовых данных и минимальную логику для алгоритмов процессора и FPGA. Используйте этот шаблон в качестве руководства и замените алгоритм FPGA и алгоритм Процессора с вашей собственной функциональностью. Алгоритм FPGA является простым умножением, выполняемым на входных данных из тестового источника и из параметра configReg. Процессор пишет configReg. Этот параметр моделируется с помощью блока Register Channel. Данные из алгоритма FPGA передаются процессору через блок Memory Channel. Память параметр Channel Type установлена в AXI4-Stream to Software via DMA, который моделирует передачу данных DMA через разделяемую внешнюю память.

Процессор считывает вычисленные данные из памяти и выполняет дополнительное вычисление, которое реализовано в шаблоне как провод передачи. Можно просмотреть результаты симуляции путем двойного клика по блоку Vector Scope в приемнике испытательного стенда.

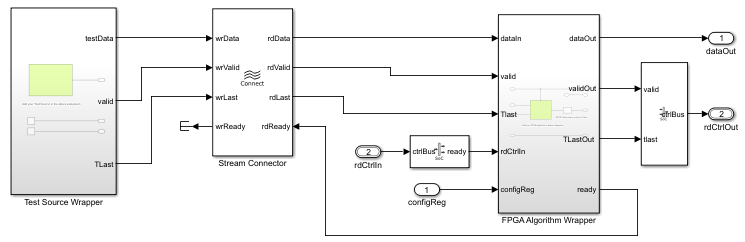

В MATLAB® панель инструментов, на вкладке Project Shortcuts , нажимает Open FPGA sample model, чтобы открыть модель FPGA. В модели две области подсвечены зеленые, который представляет пользовательский код: один в блоке FPGA Algorithm Wrapper и один в блоке Test Source Wrapper.

Обертка Алгоритма FPGA – Дважды кликает, чтобы открыть модель. Обертка алгоритма содержит зеленым подсвеченную подсистему под названием FPGA Algorithm. Этот блок имеет два входных параметров и один выход и реализован как множитель. Замените этот блок на свой собственный алгоритм FPGA. Добавьте вводы и выводы как требуется.

Протестируйте Исходную Обертку – Этот блок включает тестовый источник и предназначается, чтобы сгенерировать стимул как вход к алгоритму FPGA. Этот блок реализован как счетчик в этом шаблоне. Измените тестовый источник к своим потребностям или замените его на альтернативный исходный блок.

Совет

Когда ваша модель FPGA включает больше чем один IP, необходимо задать каждый IP как подсистему и соединить подсистемы с помощью блока Stream Connector или Video Stream Connector. Для получения дополнительной информации смотрите Факторы для Нескольких дюйм/с в Модели FPGA.

Чтобы включить сопоставимое поведение симуляции, нажмите Open FPGA frame model во вкладке Project Shortcuts и повторите этот шаг. Чтобы симулировать основанную на системе координат обработку, у вас должна быть лицензия DSP System Toolbox.

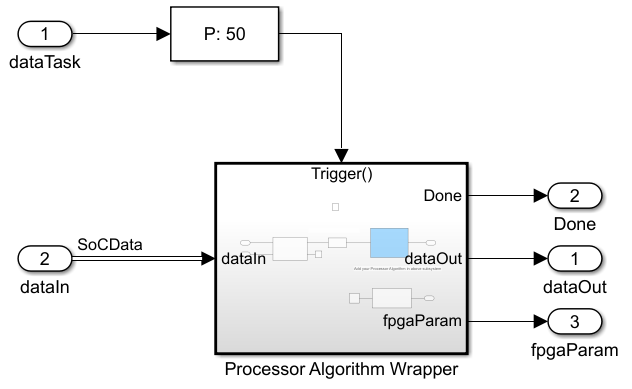

В панели инструментов MATLAB, на вкладке Project Shortcuts , нажимают Open Processor model. Обертка процессора содержит синюю подсвеченную подсистему, представляющую пользовательский код для алгоритма процессора. Откройте обертку Алгоритма Процессора и замените блок Processor Algorithm на ваш желаемый алгоритм.

Топ-модель шаблона также включает канал регистра, чтобы связаться между процессором и моделью FPGA. Используйте канал регистра, чтобы сконфигурировать модель FPGA, или считать и проверять регистры состояния. Блок Register Channel в шаблоне включает один регистр. Чтобы добавить дополнительные регистры, необходимо изменить параметры блоков канала регистра, алгоритм FPGA и алгоритм процессора:

Добавьте, что регистры к каналу регистра – Дважды кликают блок Register Channel, чтобы открыть маску блока и добавить дополнительные регистры по мере необходимости. Добавление регистров создает дополнительные порты на блоке Register Channel. Для получения дополнительной информации смотрите Register Channel.

Добавьте, что порты к модели процессора – Перешли к модели Processor Algorithm Wrapper. Чтобы перейти к модели процессора, нажмите Open Processor model на вкладке Project Shortcuts. Дважды кликните Processor Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте выходной порт в модуль и добавьте логику, чтобы управлять значением к добавленному выходному порту. Для регистров чтения добавьте входной порт и логику, чтобы обработать информацию, возвращенную в регистр чтения. От топ-модели соедините порт с блоком Register Channel.

Добавьте, что порты к модели FPGA – Перешли к модели FPGA Algorithm Wrapper. Чтобы перейти к основанной на FPGA/системе координат модели обработки, нажмите Open FPGA sample model на вкладке Project Shortcuts. Дважды кликните FPGA Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте входной порт в модуль и логику, чтобы обработать информацию, возвращенную в регистр чтения. Для регистров чтения добавьте выходной порт и логику, чтобы управлять значением к добавленному выходному порту.

Для эквивалентного поведения при использовании Simulink® основанный на выборке вариант, повторите этот шаг для основанной на выборке модели обработки в обертке FPGA.

От топ-модели соедините новый порт с блоком Register Channel.