Вычисляет обратное быстрое преобразование Фурье и генерирует оптимизированный HDL-код

Поддержка HDL DSP System Toolbox / преобразовывает

Блок IFFT HDL Optimized обеспечивает две архитектуры, которые реализуют алгоритм для приложения ASIC и FPGA. Можно выбрать архитектуру, которая оптимизирует или для пропускной способности или для области.

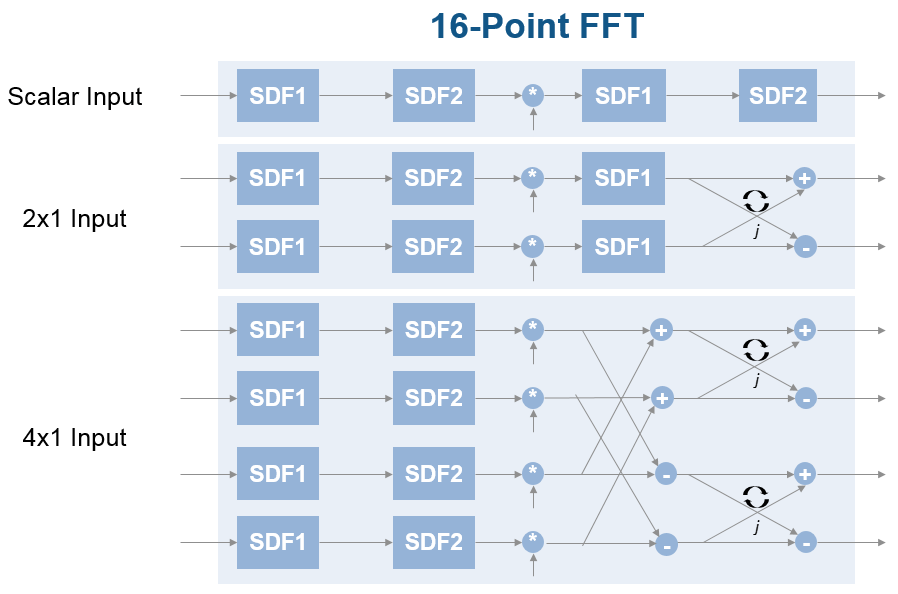

Streaming Radix 2^2 — Используйте эту архитектуру для высокопроизводительных приложений. Эта архитектура поддерживает скалярные или векторные входные данные. Можно достигнуть пропускной способности выборки гига сэмплов в секунду (GSPS) с помощью векторного входа.

Burst Radix 2 — Используйте эту архитектуру для минимизации ресурса размещения, особенно с большеразмерным быстрым преобразованием Фурье (FFT). Ваша система должна смочь допустить принятие пульсирующих данных. Эта архитектура поддерживает только скалярные входные данные.

IFFT HDL Optimized принимает действительные или комплексные данные, обеспечивает благоприятные для оборудования управляющие сигналы и дополнительные выходные сигналы управления кадром.

data — Входные данныеВходные данные в виде скаляра или вектор-столбца действительных или комплексных чисел. Только Streaming Radix 2^2 архитектура поддерживает векторный вход. Размер вектора должен быть степенью 2 в диапазоне от 1 до 64, и меньше чем или равный FFT length.

double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода.

Типы данных: int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point | single | double

Поддержка комплексного числа: Да

valid — Указывает на допустимые входные данныеЭтот порт указывает, допустимы ли входные данные. Когда входом valid является true(1 ), блок получает значение на порте входа data. Когда входом valid является false(0 ), блок игнорирует выборки входа data.

Когда вы устанавливаете параметр Architecture на Burst Radix 2, необходимо применить сигналы входа data и valid только, когда ready является 1 TRUE. Блок игнорирует сигналы входа data и valid, когда ready является 0 ложь.

Типы данных: Boolean

reset — Сбросьте управляющий сигналКогда reset является true(1 ), блок останавливает текущее вычисление и очищает все внутренние состояния. Блок запускает новую систему координат, когда reset является false(0 ) и входом valid является true(1 ).

Чтобы включить этот порт, выберите параметр Enable reset input port.

Типы данных: Boolean

data — Выходные данные канала частотыКогда введенный тип данных с фиксированной точкой, и масштабирование включено, тип выходных данных совпадает с типом входных данных. Когда вход является целочисленным типом, и масштабирование включено, выход является фиксированной точкой с тем же размером слова как входное целое число. Выходной порядок инвертируется битом по умолчанию. Если масштабирование отключено, выходной размер слова увеличивается, чтобы избежать переполнения. Только Streaming Radix 2^2 архитектура поддерживает векторный ввод и вывод. Для получения дополнительной информации смотрите параметр Divide butterfly outputs by two.

Типы данных: fixed point | double | single

Поддержка комплексного числа: Да

valid — Указывает на допустимые выходные данныеЭтот порт указывает, что выход data допустим. Когда valid является true(1 ), блок возвращает допустимые данные по порту выхода data. Когда valid является false(0 ), значения на порте выхода data не допустимы.

Типы данных: Boolean

ready — Указывает, что блок готовЭтот порт указывает, что блок имеет память в наличии, чтобы вместить новую входную выборку. Необходимо применить сигналы входа data и valid только, когда ready является true(1 ). Когда ready является false(0 ), блок игнорирует любые входные данные в следующем временном шаге. Для формы волны, которая показывает этот протокол, см. третью схему в разделе Timing Diagram.

Порт появляется на блоке, когда вы устанавливаете параметр Architecture на Burst Radix 2.

Типы данных: Boolean

start — Указывает сначала на допустимый цикл выходных данныхКогда вы включаете этот порт, блок устанавливает start выход на true(1 ) во время первого допустимого цикла системы координат выходных данных.

Чтобы включить этот порт, выберите параметр Enable start output port.

Типы данных: Boolean

end — Указывает в последний раз на допустимый цикл выходных данныхКогда вы включаете этот порт, блок устанавливает end выход на true(1 ) во время последнего допустимого цикла системы координат выходных данных.

Чтобы включить этот порт, выберите параметр Enable end output port.

Типы данных: Boolean

FFT length — Количество точек данных используется для одного вычисления БПФЭтот параметр задает количество точек данных, используемых для одного вычисления обратного быстрого преобразования Фурье (IFFT). Для генерации HDL-кода длина БПФ должна быть степенью 2 между 23 и 216.

Architecture — Тип архитектурыStreaming Radix 2^2 (значение по умолчанию) | Burst Radix 2Этот параметр задает тип архитектуры.

Streaming Radix 2^2 — Выберите это значение, чтобы задать архитектуру низкой задержки. Этот тип архитектуры поддерживает пропускную способность GSPS при использовании векторного входа.

Burst Radix 2 — Выберите это значение, чтобы задать минимальную архитектуру ресурса. Этот тип архитектуры не поддерживает векторный вход. Когда вы используете эту архитектуру, ваши входные данные должны выполнить сигнал противодавления ready. Для формы волны, которая показывает этот протокол, см. третью схему в разделе Timing Diagram.

Для генерации HDL-кода длина БПФ должна быть степенью 2 между 23 и 216.

Для получения дополнительной информации об этих архитектурах, см. Алгоритмы.

Complex Multiplication — Реализация HDLUse 4 multipliers and 2 adders (значение по умолчанию) | Use 3 multipliers and 5 addersЭтот параметр задает комплексный тип множителя для реализации HDL. Каждое умножение реализовано любой с Use 4 multipliers and 2 adders или с Use 3 multipliers and 5 adders. Скорость реализации зависит от инструмента синтеза и целевого устройства, которое вы используете.

Output in bit-reversed order — Порядок выходных данныхЭтот параметр возвращает выходные элементы в обратном битовом порядке.

Когда вы выбираете этот параметр, выходные элементы инвертируются битом. Чтобы возвратить выходные элементы в линейном порядке, очистите этот параметр.

Алгоритм ОБПФ вычисляет выход в обратном порядке к входу. Если вы задаете выход, чтобы быть в том же порядке как вход, алгоритм выполняет дополнительную операцию реверсирования. Для получения дополнительной информации смотрите Линейный и Инвертированный Битом Выходной Порядок.

Input in bit-reversed order — Ожидаемый порядок входных данныхКогда вы выберете этот параметр, блок ожидает входные данные в обратном битовом порядке. По умолчанию флажок снимается, и вход ожидается в линейном порядке.

Алгоритм ОБПФ вычисляет выход в обратном порядке к входу. Если вы задаете выход, чтобы быть в том же порядке как вход, алгоритм выполняет дополнительную операцию реверсирования. Для получения дополнительной информации смотрите Линейный и Инвертированный Битом Выходной Порядок.

Divide butterfly outputs by two — Масштабирование БПФКогда вы выбираете этот параметр, блок реализует полный 1/N масштабный коэффициент путем деления выхода каждого умножения бабочки два. Эта корректировка сохраняет выход ОБПФ в той же амплитудной области значений как ее вход. Если вы отключаете масштабирование, блок избегает переполнения путем увеличения размера слова на 1 бит после каждого умножения бабочки. Битное увеличение является тем же самым для обеих архитектур.

Rounding Method — Режим Rounding для внутренних вычислений фиксированной точкиFloor (значение по умолчанию) | Ceiling | Convergent | Nearest | Round | ZeroЭтот параметр позволяет вам выбирать тип округления режима для внутренних вычислений фиксированной точки. Для получения дополнительной информации об округлении режимов, смотрите округление метода. Когда вход является любым целым числом или типом данных с фиксированной точкой, алгоритм ОБПФ использует вычисления с фиксированной точкой для внутренних вычислений. Эта опция не применяется, когда входом является single или double ввод. Округление применяется, чтобы вертеть факторное умножение и операции масштабирования.

Enable reset input port — Дополнительный сигнал сбросаЭтот параметр включает входной порт сброса. Когда вы выбираете этот параметр, порт входа reset появляется на значке блока.

Enable start output port — Дополнительный управляющий сигнал, указывающий, запускается данныхЭтот параметр включает порт, который указывает на запуск выходных данных. Когда вы выбираете этот параметр, порт выхода start появляется на значке блока.

Enable end output port — Дополнительный конец указания управляющего сигнала данныхЭтот параметр включает порт, который указывает на конец выходных данных. Когда вы выбираете этот параметр, порт выхода end появляется на значке блока.

Основание потоковой передачи 2^2 архитектура реализует архитектуру низкой задержки. Это сохраняет ресурсы по сравнению с Основанием потоковой передачи 2 реализации путем факторинга и группировки уравнения FFT. Архитектура имеет log4 (N) этапы. Каждый этап содержит двух бабочек обратной связи задержки одно пути (SDF) с контроллерами памяти. Когда вы используете векторный вход, каждый этап работает с меньшим количеством входных выборок, таким образом, некоторые этапы уменьшают до простой бабочки без SDF.

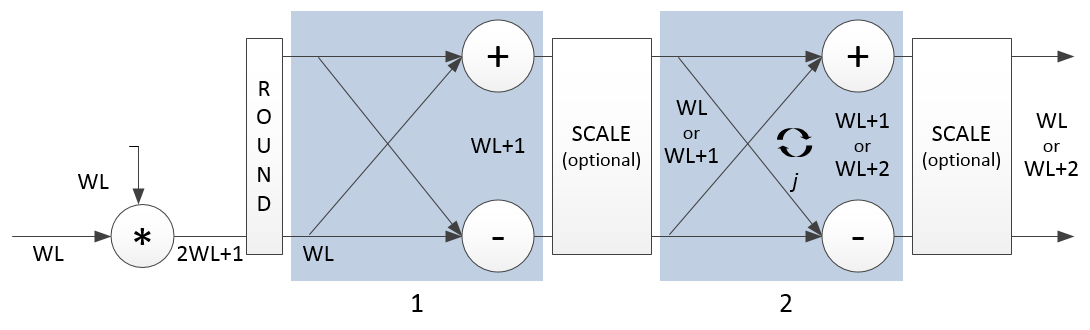

Первый этап SDF является обычной бабочкой. Второй этап умножает выходные параметры первой стадии –j. Чтобы избежать аппаратного множителя, блок подкачивает действительные и мнимые части входных параметров, и снова подкачивает мнимые части получившихся выходных параметров. Каждый этап округляет результат вертеть факторного умножения к входному размеру слова. Вертеть факторы имеют два целочисленных бита, и остальная часть битов используется для дробных битов. Вертеть факторы имеют ту же битную ширину как входные данные, WL. Вертеть факторы имеют два целочисленных бита и WL-2 дробных бита.

Если вы позволяете масштабироваться, алгоритм делит результат каждого этапа бабочки 2. Масштабирование на каждом этапе избегает переполнения, сохраняет размер слова тем же самым как вход и приводит к полному масштабному коэффициенту 1/N. Если масштабирование отключено, алгоритм избегает переполнения путем увеличения размера слова на 1 бит на каждом этапе. Схема показывает бабочек и внутренние размеры слова каждого этапа, не включая память.

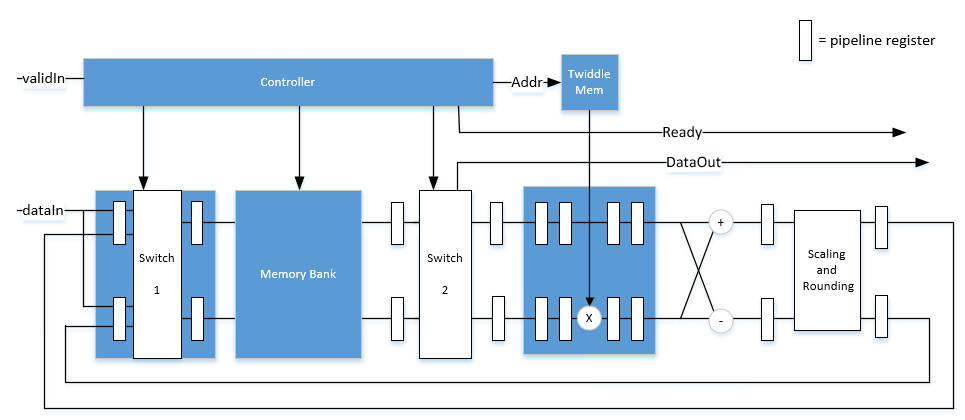

Пакетное Основание 2 реализации архитектуры БПФ при помощи одного комплексного множителя бабочки. Алгоритм не может запуститься, пока он не сохранил целый входной кадр, и он не может принять следующую систему координат, пока расчеты не завершены. Порт выхода ready указывает, когда алгоритм готов к новым данным. Схема показывает пакетную архитектуру с регистрами трубопровода.

Когда вы используете эту архитектуру, ваши входные данные должны выполнить сигнал противодавления ready. Для формы волны, которая показывает этот протокол, см. третью схему в разделе Timing Diagram.

Входные данные процессов алгоритма только, когда порт входа valid равняется 1. Выходные данные допустимы только, когда порт выхода valid равняется 1.

Когда дополнительный порт входа reset равняется 1, алгоритм останавливает текущее вычисление и очищает все внутренние состояния. Алгоритм начинает новые вычисления, когда порт reset 0, и порт входа valid запускает новую систему координат.

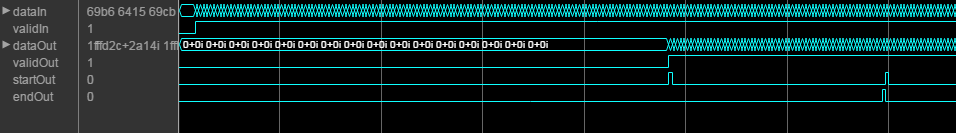

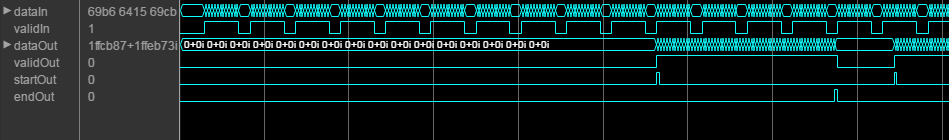

Эта схема показывает значения порта valid ввода и вывода для непрерывных скалярных входных данных, передавая Основание потоком 2^2 архитектура, длина БПФ 1 024 и размер вектора 16.

Схема также показывает дополнительные значения порта start и end, которые указывают на контуры системы координат. Если вы включаете порт start, импульсы значения порта start для одного цикла с первым допустимым выходом системы координат. Если вы включаете порт end, импульсы значения порта start для одного цикла с последним допустимым выходом системы координат.

Если вы примените непрерывные входные кадры, выход также будет непрерывен после начальной задержки.

Порт входа valid может быть, состоящим из нескольких несмежных участков. Данные, сопровождаемые портом входа valid, обрабатываются, когда они прибывают, и получившиеся данные хранятся, пока система координат не заполнена. Затем алгоритм возвращает непрерывные выходные выборки в системе координат N (FFT length) циклы. Эта схема показывает вход, состоящий из нескольких несмежных участков, и непрерывный выход для длины БПФ 512 и размера вектора 16.

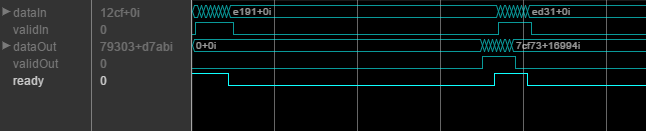

Когда вы используете пакетную архитектуру, вы не можете обеспечить следующую систему координат входных данных, пока пространство памяти не доступно. Сигнал ready указывает, когда алгоритм может принять новые входные данные. Необходимо применить сигналы входа data и valid только, когда ready является 1 TRUE. Алгоритм игнорирует любые сигналы входа data и valid, когда ready является 0 ложь.

Задержка меняется в зависимости от FFT length и размера входного вектора. После того, как вы обновите модель, значок блока отображает задержку. Отображенная задержка является количеством циклов между первым допустимым входом и первым допустимым выходом, принимая, что вход непрерывен. Чтобы получить эту задержку программно, смотрите, что Автоматическая Задержка Совпадает для Задержки HDL БПФ с Оптимизированным Блоком.

При использовании пакетной архитектуры с непрерывным входом, если ваш проект ожидает ready к выходу 0 перед de-утверждением вход valid затем один дополнительный цикл данных прибывает во вход. Эта выборка данных является первой выборкой следующей системы координат. Алгоритм может сохранить одну выборку при обработке текущего кадра. Из-за этого демонстрационного усовершенствования, наблюдаемая задержка более поздних систем координат (от входа valid до выхода valid) является одним циклом короче, чем задержка, о которой сообщают. Задержка измеряется от первого цикла, когда вход valid 1 к первому циклу, когда выход valid равняется 1. Количество циклов между тем, когда порт ready 0 и порт выхода valid, равняется 1, всегда latency – FFTLength.

Эти данные ресурсов и данные о производительности являются синтезом, следуют из сгенерированного HDL, предназначенного к Xilinx® Virtex®- 6 FPGA (XC6VLX75T-1FF484). Примеры в таблицах имеют эту настройку:

Длина БПФ 10:24 (значение по умолчанию)

Комплексное умножение с помощью 4 множителей, 2 сумматоров

Выведите включенное масштабирование

Вход естественного порядка, инвертированный Битом выход

16-битные комплексные входные данные

Часы включают минимизированный (параметр HDL Coder™)

Эффективность синтезируемого HDL-кода меняется в зависимости от вашей цели и опций синтеза. Например, переупорядочение для естественного порядка вывело использование больше RAM, чем значение по умолчанию инвертированный битом выход, и действительный вход использует меньше RAM, чем комплексный вход.

Для скалярного входа Radix 2^2 настройка, проект достигает тактовой частоты на 326 МГц. Задержка является 1 116 циклами. Проект использует эти ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 4597 |

| FFS | 5353 |

Xilinx LogiCORE® DSP48 | 12 |

| Блокируйте RAM (16K) | 6 |

Когда вы векторизуете то же Основание 2^2 реализация, чтобы обработать две 16-битных входных выборки параллельно, проект достигает тактовой частоты на 316 МГц. Задержка является 600 циклами. Проект использует эти ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 7653 |

| FFS | 9322 |

Xilinx LogiCORE DSP48 | 24 |

| Блокируйте RAM (16K) | 8 |

Блок поддерживает скалярные входные данные только при реализации пакетного Основания 2 архитектуры. Пакетный проект достигает тактовой частоты на 309 МГц. Задержка является 5 811 циклами. Проект использует эти ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 971 |

| FFS | 1254 |

Xilinx LogiCORE DSP48 | 3 |

| Блокируйте RAM (16K) | 6 |

Этот блок поддерживает генерацию кода C/C++ для Simulink® акселератор и быстрые режимы Accelerator и для генерации компонента DPI.

HDL Coder обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

Если вы используете блок IFFT HDL Optimized с блоком State Control (HDL Coder) в Enabled Subsystem (Simulink), дополнительный порт сброса не поддерживается. Если вы включите порт сброса на блоке IFFT HDL Optimized в такой подсистеме, модель будет ошибка на Схеме Обновления.

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.