Кодер включает блок комментария заголовка наверху файлов, которые он генерирует. Блок комментария заголовка содержит технические требования генерирующегося фильтра и опции кодера, которые были выбраны в то время, когда HDL-код был сгенерирован.

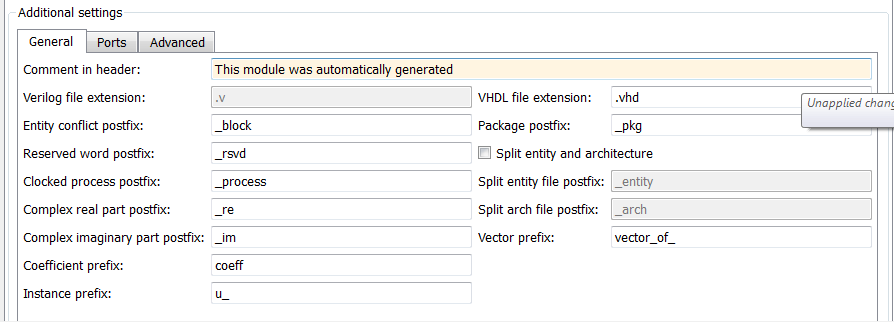

Можно использовать опцию Comment in header, чтобы добавить комментарий в конец блока комментария заголовка в каждом сгенерированном файле. Например, используйте эту опцию, чтобы добавить “This module was automatically generated”. С этим изменением появился бы следующим предыдущий блок комментария заголовка:

-- ------------------------------------------------------------- -- -- Module: Hlp -- -- Generated by MATLAB(R) 7.11 and the Filter Design HDL Coder 2.7. -- -- Generated on: 2010-08-31 13:32:16 -- -- This module was automatically generated -- -- ------------------------------------------------------------- -- ------------------------------------------------------------- -- HDL Code Generation Options: -- -- TargetLanguage: VHDL -- Name: Hlp -- UserComment: User data, length 47 -- Filter Specifications: -- -- Sampling Frequency : N/A (normalized frequency) -- Response : Lowpass -- Specification : Fp,Fst,Ap,Ast -- Passband Edge : 0.45 -- Stopband Edge : 0.55 -- Passband Ripple : 1 dB -- Stopband Atten. : 60 dB -- ------------------------------------------------------------- -- ------------------------------------------------------------- -- HDL Implementation : Fully parallel -- Multipliers : 43 -- Folding Factor : 1 -- ------------------------------------------------------------- -- Filter Settings: -- -- Discrete-Time FIR Filter (real) -- ------------------------------- -- Filter Structure : Direct-Form FIR -- Filter Length : 43 -- Stable : Yes -- Linear Phase : Yes (Type 1) -- Arithmetic : fixed -- Numerator : s16,16 -> [-5.000000e-001 5.000000e-001) -- Input : s16,15 -> [-1 1) -- Filter Internals : Full Precision -- Output : s33,31 -> [-2 2) (auto determined) -- Product : s31,31 -> [-5.000000e-001 5.000000e-001) (auto determined) -- Accumulator : s33,31 -> [-2 2) (auto determined) -- Round Mode : No rounding -- Overflow Mode : No overflow -- -------------------------------------------------------------

Добавить комментарий заголовка,

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

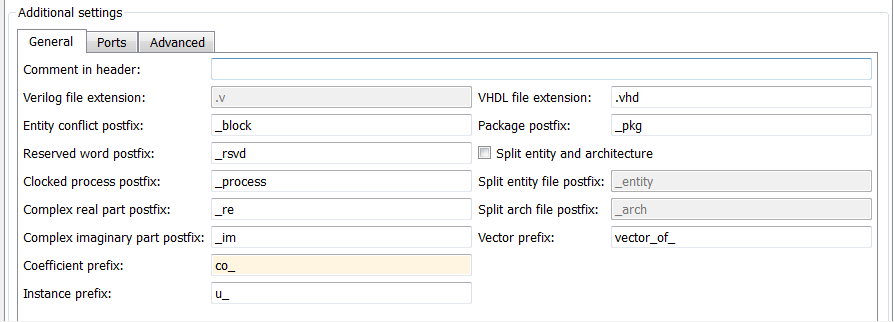

Выберите вкладку General в панели Additional settings.

Введите текст комментария в поле Comment in header как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством UserComment добавить комментарий в конец блока комментария заголовка в каждом сгенерированном файле HDL.

Кодер проверяет, совместно используют ли несколько сущностей в VHDL или несколько модулей в Verilog то же имя. Если конфликт по совпадению имен существует, кодер добавляет постфиксный '_block' к второму из двух соответствующих векторов символов.

Изменить постфикс:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings.

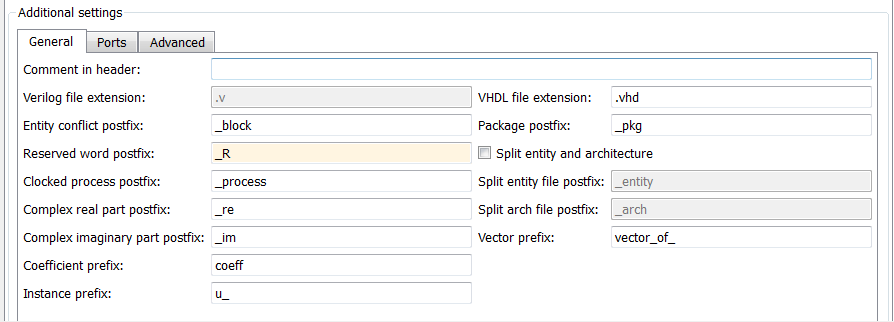

Введите новый вектор символов в поле Entity conflict postfix как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством EntityConflictPostfix чтобы изменить сущность или модуль конфликтуют постфикс.

Кодер проверяет, снабжают ли векторы символов, которые вы задаете как имена, постфиксом значения, или метки являются зарезервированными словами VHDL или Verilog. См. Таблицы Зарезервированного слова для списков зарезервированных слов VHDL и Verilog.

Если вы задаете зарезервированное слово, кодер добавляет постфиксный _rsvd к вектору символов. Например, при попытке назвать свой фильтр mod, для кода VHDL кодер добавляет постфиксный _rsvd сформировать имя mod_rsvd.

Изменить постфикс:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings.

Введите новый вектор символов в поле Reserved word postfix как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством ReservedWordPostfix изменить постфикс зарезервированного слова.

Следующие таблицы приводят зарезервированные слова VHDL и Verilog.

Зарезервированные слова VHDL

abs | access | after | alias | all |

and | architecture | array | assert | attribute |

begin | block | body | buffer | bus |

case | component | configuration | constant | disconnect |

downto | else | elsif | end | entity |

exit | file | for | function | generate |

generic | group | guarded | if | impure |

in | inertial | inout | is | label |

library | linkage | literal | loop | map |

mod | nand | new | next | nor |

not | null | of | on | open |

or | others | out | package | port |

postponed | procedure | process | pure | range |

record | register | reject | rem | report |

return | rol | ror | select | severity |

signal | shared | sla | sll | sra |

srl | subtype | then | to | transport |

type | unaffected | units | until | use |

variable | wait | when | while | with |

xnor | xor |

Зарезервированные слова Verilog

always | and | assign | automatic | begin |

buf | bufif0 | bufif1 | case | casex |

casez | cell | cmos | config | deassign |

default | defparam | design | disable | edge |

else | end | endcase | endconfig | endfunction |

endgenerate | endmodule | endprimitive | endspecify | endtable |

endtask | event | for | force | forever |

fork | function | generate | genvar | highz0 |

highz1 | if | ifnone | incdir | include |

initial | inout | input | instance | integer |

join | large | liblist | library | localparam |

macromodule | medium | module | nand | negedge |

nmos | nor | noshowcancelled | not | notif0 |

notif1 | or | output | parameter | pmos |

posedge | primitive | pull0 | pull1 | pulldown |

pullup | pulsestyle_onevent | pulsestyle_ondetect | rcmos | real |

realtime | reg | release | repeat | rnmos |

rpmos | rtran | rtranif0 | rtranif1 | scalared |

showcancelled | signed | small | specify | specparam |

strong0 | strong1 | supply0 | supply1 | table |

task | time | tran | tranif0 | tranif1 |

tri | tri0 | tri1 | triand | trior |

trireg | unsigned | use | vectored | wait |

wand | weak0 | weak1 | while | wire |

wor | xnor | xor |

По умолчанию кодер добавляет постфиксный _pkg к основному имени файла при генерации файла пакета VHDL. Чтобы переименовать постфикс для файлов пакета, сделайте следующее:

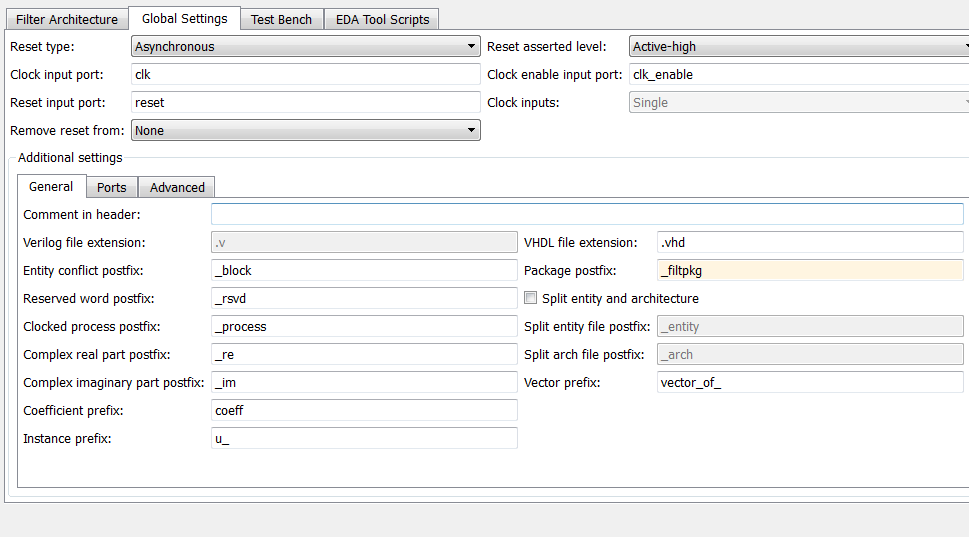

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings .

Задайте новое значение в поле Package postfix.

Примечание

При определении вектора символов для использования в качестве постфикса в именах файлов рассмотрите размер базового имени и специфичных для платформы требований именования файла и ограничений.

Альтернатива командной строки: используйте generatehdl функция с PackagePostfix свойство переименовать имя файла снабжает постфиксом для файлов пакета VHDL.

Кодер объявляет коэффициенты для фильтра как константы в rtl архитектура. Кодер выводит постоянные имена, добавляющие префиксный coeff. Содействующие имена зависят от типа фильтра.

| Для... | Префикс конкатенирован с... |

|---|---|

| КИХ-фильтры | Каждый содействующий номер, начиная с 1. Примеры: |

| БИХ-фильтры | Подчеркивание (_) и Пример: |

Например:

ARCHITECTURE rtl OF filt IS -- Type Definitions TYPE delay_pipeline_type IS ARRAY(NATURAL range <>) OF signed(15 DOWNTO 0);-- sfix16_En15 CONSTANT coeff1 : signed(15 DOWNTO 0) := to_signed(-30, 16); -- sfix16_En15 CONSTANT coeff2 : signed(15 DOWNTO 0) := to_signed(-89, 16); -- sfix16_En15 CONSTANT coeff3 : signed(15 DOWNTO 0) := to_signed(-81, 16); -- sfix16_En15 CONSTANT coeff4 : signed(15 DOWNTO 0) := to_signed(120, 16); -- sfix16_En15

Использовать префикс кроме coeff,

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings.

Введите новый вектор символов в поле Coefficient prefix как показано в следующем рисунке.

Вектор символов, который вы задаете

Должен начаться с буквы.

Не может включать двойное подчеркивание (__).

Примечание

Если вы задаете зарезервированное слово VHDL или Verilog, кодер добавляет постфикс зарезервированного слова к вектору символов, чтобы сформировать допустимый идентификатор. Если вы задаете префикс, который заканчивается подчеркиванием, кодер заменяет символ подчеркивания на under. Например, если вы задаете coef_, кодер генерирует содействующие имена, такие как coefunder1.

Альтернатива командной строки: используйте generatehdl функция со свойством CoeffPrefix изменять базовое название для коэффициентов фильтра.

Кодер генерирует блоки процесса, чтобы изменить содержимое регистров. Метка для каждого из этих блоков выведена из имени регистра и постфиксного _process. Например, кодер выводит метку delay_pipeline_process в следующем блоке из регистра называют delay_pipeline и постфиксный '_process'.

delay_pipeline_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

delay_pipeline (0 To 50) <= (OTHERS => (OTHERS => '0'));

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

delay_pipeline(0) <= signed(filter_in)

delay_pipeline(1 TO 50) <= delay_pipeline(0 TO 49);

END IF;

END IF;

END PROCESS delay_pipeline_process;

Свойство Clocked process postfix позволяет вам изменить постфикс в значение кроме '_process'. Например, чтобы изменить постфикс в '_clkproc', сделайте следующее:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings.

Введите новый вектор символов в поле Clocked process postfix как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством ClockProcessPostfix изменить постфикс, добавленный, чтобы обработать метки.

Instance prefix задает вектор символов, который будет снабжен префиксом к именам экземпляра компонента в сгенерированном коде. Значением по умолчанию является 'u_'.

Можно установить префикс на значение кроме 'u_'. Изменить префикс:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings.

Введите новый вектор символов в поле Instance prefix как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством InstancePrefix изменить префикс экземпляра.

Vector prefix задает вектор символов, который будет снабжен префиксом к векторным именам в сгенерированном коде VHDL. Значением по умолчанию является 'vector_of_'.

Примечание

Vector prefix не поддерживается для генерации кода Verilog.

Можно установить префикс на значение кроме 'vector_of_'. Изменить префикс:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку General в панели Additional settings.

Введите новый вектор символов в поле Vector prefix как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством VectorPrefix изменить префикс экземпляра.