Можно сгенерировать код, который имеет несколько испытательных стендов от подсистемы. Для сгенерированного кода, чтобы иметь несколько испытательных стендов, вход к вашей подсистеме должен состоять из нескольких групп сигнала.

Сгенерировать несколько испытательных стендов для вашей подсистемы:

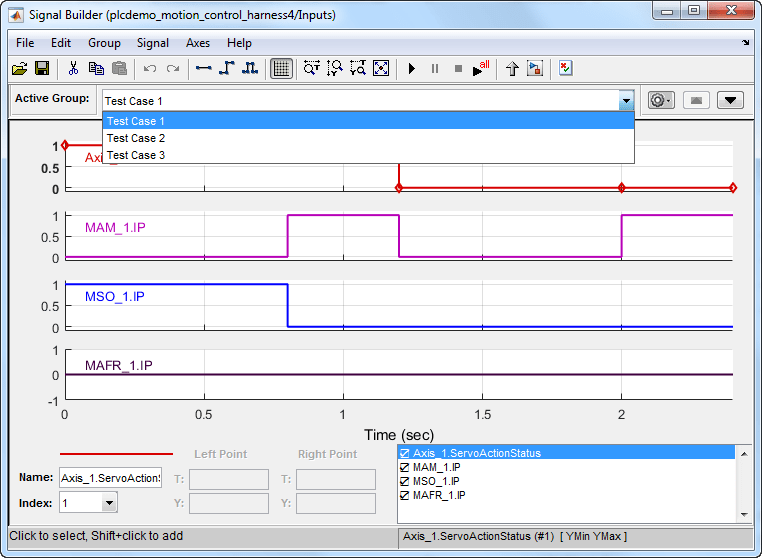

Предоставьте нескольким группам сигнала как входным параметрам при помощи блока Signal Builder, который имеет несколько групп сигнала.

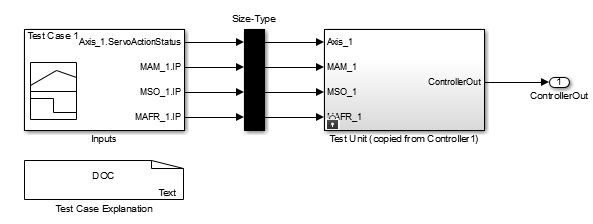

Используйте Simulink® Design Verifier™, чтобы создать модель тестовой обвязки из подсистемы. В модели тестовой обвязки блок Signal Builder, который имеет одну или несколько групп сигнала, предоставляет вход подсистеме. Используйте этот блок Signal Builder, чтобы предоставить входные параметры вашей подсистеме. Если ваша модель является комплексной, Simulink Design Verifier может создать большое количество групп сигнала. Смотрите Поиск и устранение проблем: Тестовые данные Превышают Целевой Размер данных.

Создать ваш блок Signal Builder:

Щелкните правой кнопкой по подсистеме и выберите Design Verifier> Generate Tests for Subsystem.

В окне Simulink Design Verifier Results Summary выберите Create harness model.

Откройте блок Inputs в модели тестовой обвязки. Блоком Inputs является блок Signal Builder, который может иметь одну или несколько групп сигнала.

В окне Signal Builder убедитесь, что больше чем одна группа сигнала доступна в Active Group выпадающий список.

Скопируйте блок Signal Builder с режима тестовой обвязки. Используйте этот блок, чтобы предоставить входные параметры вашей исходной подсистеме.

Сгенерируйте испытательные стенды для подсистемы:

Откройте приложение PLC Coder. Кликните по вкладке PLC Code> Settings> PLC Code Generation.

Выберите опцию Generate testbench for subsystem.

Откройте свою модель и откройте PLC Coder App. Нажмите Settings, и затем выберите Verify Code in IDE.

В вашем целевом IDE вы видите несколько испытательных стендов. Каждый испытательный стенд соответствует группе сигнала.

Если тестовые данные от нескольких групп сигнала превышают максимальный размер данных на вашей цели, можно столкнуться с ошибками компиляции. Если вы сталкиваетесь с ошибками компиляции при генерации нескольких испытательных стендов попробуйте одно из следующего:

Сократите количество групп сигнала в блоке Signal Builder и регенерируйте испытательные стенды.

Увеличьте размер шага симуляции для подсистемы.

Когда вы переключаетесь между группами сигнала, время симуляции модели должно остаться то же самое для целой симуляции. Не изменяйте время симуляции модели.