Анализируйте Simulink® модель при помощи socModelAnalyzer функционируйте, чтобы оценить ресурсы, используемые в модели, сравнить различные архитектуры и изучить компромиссы проекта. Используйте socFunctionAnalyzer функция, чтобы анализировать ресурсы в MATLAB® функция.

socModelAnalyzer и socFunctionAnalyzer функции создают отчет, детализирующий количество операций в модели Simulink или функции MATLAB, соответственно.

Используйте информацию в отчете к:

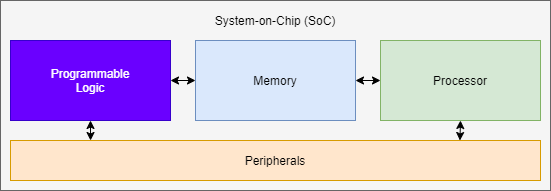

Решите, как разделить ваш алгоритм в программное и аппаратное обеспечение.

Оптимизируйте аппаратный алгоритм.

Оптимизируйте алгоритм программного обеспечения.

Сравните различные реализации алгоритма, чтобы сделать обоснованные решения о проектных решениях.

socModelAnalyzer | Оцените количество операций в модели Simulink |

socFunctionAnalyzer | Оцените количество операций в функции MATLAB |

socAlgorithmAnalyzerReport | Открытый аналитический отчет алгоритма |

socExportReferenceDesign | Экспортируйте пользовательский исходный проект для HDL Workflow Advisor |

| Logic Analyzer | Визуализируйте, измерьте и анализируйте переходы и состояния в зависимости от времени |

Факторы для нескольких дюйм/с в модели FPGA

Когда ваша модель FPGA включает больше чем один блок, для которого требуется сгенерировать HDL с помощью HDL Coder™, необходимо использовать модель коннектора, чтобы соединить блоки.

Используя алгоритм отчет анализатора

Переместитесь по деталям отчета, сгенерированного socModelAnalyzer или socFunctionAnalyzer функция.

Экспортируйте пользовательский исходный проект из модели SoC

Используйте socExportReferenceDesign функционируйте, чтобы экспортировать пользовательский исходный проект из модели SoC Blockset™.

Создайте ошибку когда FPGA или модель процессора, не обнаруженная

Режим Unsupported в при генерации проекта SoC с помощью SoC Builder.