Модель SoC Blockset™ состоит из топ-модели, которая включает по крайней мере один из этих образцов модели.

Образец модели FPGA представляет часть FPGA устройства SoC. Топ-модель может включать самое большее один образец модели FPGA. Для получения информации о том, как настроить образец модели FPGA, смотрите Пользовательскую Логику на FPGA.

Образец модели процессора представляет часть процессора устройства SoC. Топ-модель может включать один или несколько образцов модели процессора. Для получения информации о том, как настроить образец модели процессора, смотрите Управление программным обеспечением и управление задачами на Процессоре.

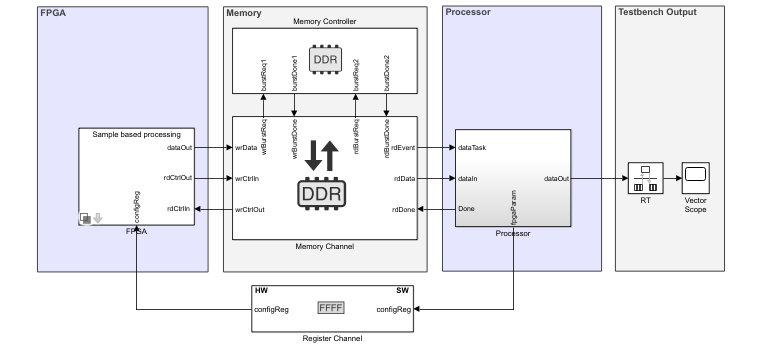

Процессор и подсистемы FPGA связываются через Memory Channel, блок Register Channel или Interrupt Channel.

В дополнение к FPGA и образцам модели процессора, топ-модель может включать дополнительные блоки SoC Blockset, такие как блоки, перечисленные здесь, для моделирования компоненты испытательного стенда и интерфейсы.

Следующее изображение показывает модель SoC Blockset, с образцом модели FPGA, образцом модели процессора, связывающимся по каналу памяти.

Для примера модели SoC Blockset смотрите Данные о Потоковой передаче от Оборудования до программного обеспечения.

SoC Blockset обеспечивает шаблоны проекта для общих примеров использования SoC. Используйте их в качестве начальной точки для вашего проекта.