Обнаружьте ошибки во входных данных с помощью CRC

Wireless HDL Toolbox / Выявление ошибок и Коррекция

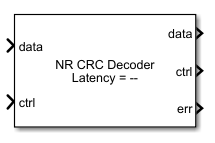

Блок NR CRC Decoder вычисляет контрольную сумму контроля циклическим избыточным кодом (CRC) и сравнивает ее с добавленной контрольной суммой CRC для каждой системы координат потоковой передачи выборок данных. Если две контрольных суммы CRC не соответствуют, блок сообщает об ошибке. Блок принимает и возвращает демонстрационный поток данных с сопроводительными управляющими сигналами. Управляющие сигналы указывают на валидность выборок и контуры системы координат.

Блок поддерживает скалярные и векторные данные о вводах и выводах или как скаляр или как вектор на основе входных данных. Чтобы достигнуть более высокой пропускной способности, блок принимает бинарный вектор или скалярный вход беззнаковых целых чисел и реализует параллельную архитектуру. Ширина входных данных должна быть меньше чем или равна длине полинома CRC, и длина полинома CRC должна быть делимой шириной входных данных. Блок поддерживает все полиномы CRC, заданные согласно стандарту нового радио (NR) 5G 3GPP TS 38.212 [1]. Когда вы выбираете полином CRC24C, блок поддерживает динамическую маску CRC.

Блок обеспечивает интерфейсную и аппаратную оптимизированную архитектуру, подходящую для аппаратного развертывания и генерации HDL-кода.

[1] 3GPP TS 38.212. “NR; мультиплексирование и кодирование канала”. Проект партнерства третьего поколения; сеть радиодоступа Technical Specification Group.

[2] Кампобелло, G., Г. Пэтэйн и М. Руссо. “Параллельная Реализация CRC”. Транзакции IEEE на Компьютерах 52, № 10 (октябрь 2003): 1312–19. https://doi.org/10.1109/TC.2003.1234528.