FPGA в цикле (FIL) позволяет вам запустить Simulink® симуляция, которая синхронизируется с проектом HDL, работающим на Intel® или Xilinx® Плата FPGA. Эта ссылка между средством моделирования и платой позволяет вам проверить реализации HDL непосредственно по Simulink или MATLAB® алгоритмы. Можно применить реальные данные и сценарии тестирования от этих алгоритмов до проекта HDL на FPGA.

При симуляции блоков Wireless HDL Toolbox™ необходимо использовать демонстрационный интерфейс потоковой передачи. Потоковая передача выборочных данных, в то время как требуется для аппаратных реализаций систем связи, длительна в FPGA в интерфейсе цикла с Simulink.

Можно преобразовать от систем координат до выборок и выборок к системам координат или в Simulink или в MATLAB. В зависимости от вашего рабочего процесса можно оптимизировать FPGA в симуляции цикла одним из двух способов.

Один рабочий процесс является моделью Simulink, которая импортирует обрамленные данные из MATLAB. Этот тип модели затем использует Frame To Samples и блоки Samples To Frame, чтобы преобразовать формат данных. Для FPGA в цикле замените эти блоки преобразования на блоки FIL Samples To Frame и FIL Frame To Samples.

Другой рабочий процесс является моделью Simulink, которая импортирует данные о потоковой передаче из MATLAB. Этот тип модели идет со скриптом MATLAB, который использует ltehdlFrameToSamples и ltehdlSamplesToFrames функции. Для FPGA в цикле измените свой скрипт и модель Simulink так, чтобы они передали векторы из данных к FPGA в интерфейсе цикла.

Когда вы генерируете файл программирования для цели FIL в Simulink, инструмент создает модель, чтобы сравнить симуляцию FIL с вашим проектом Simulink. Для проектов Wireless HDL Toolbox блок FIL в той модели реплицирует передающий потоком выборку интерфейс и отправляет одну выборку за один раз в FPGA. И эти модификации создают векторы, которые делают более эффективное использование интерфейса между моделью Simulink и платой FPGA.

Инструкции, которые следуют, показывают, как изменить FPGA в моделях цикла для Проверять Турбо Декодера с Потоковой передачей Данных из MATLAB и Проверить Турбо Декодер с Обрамленными Данными из примеров рабочего процесса MATLAB.

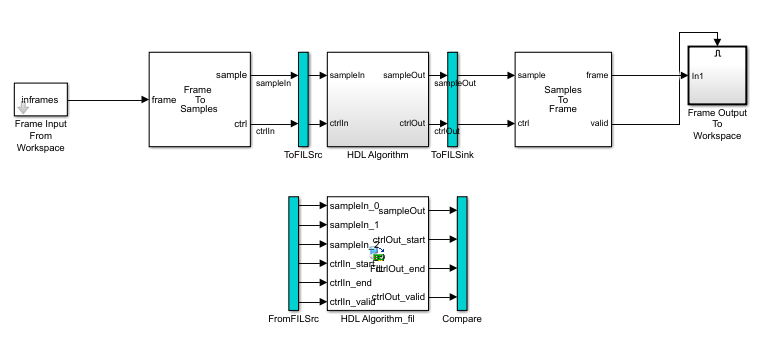

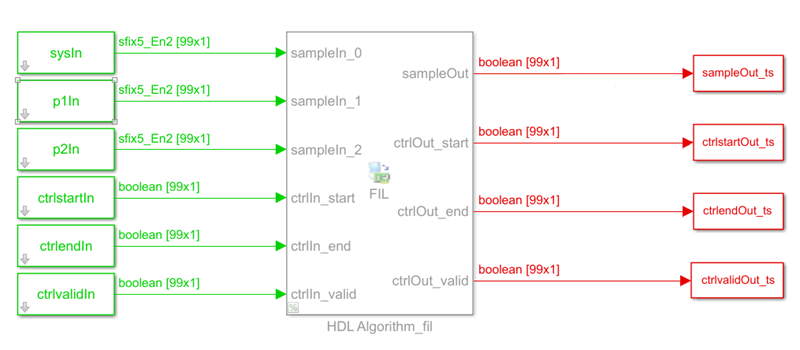

Сгенерированную модель, включая блок FIL, который взаимодействует через интерфейс с платой FPGA, показывают для модели, которая преобразует в потоковую передачу выборок в Simulink. Если каждая выборка представлена несколькими значениями, то значения сглажены в отдельные порты для FIL.

Синяя подсистема ToFILSrc переходит демонстрационный потоковый ввод блока HDL Algorithm к подсистеме FromFILSrc. Синяя подсистема ToFILSink переходит демонстрационный поток выход блока HDL Algorithm в подсистему Compare, где это по сравнению с выходом блока HDL Algorithm_fil. Эта настройка является медленной, потому что модель отправляет только одну выборку и ее связанные управляющие сигналы, в каждом пакете к и от платы FPGA.

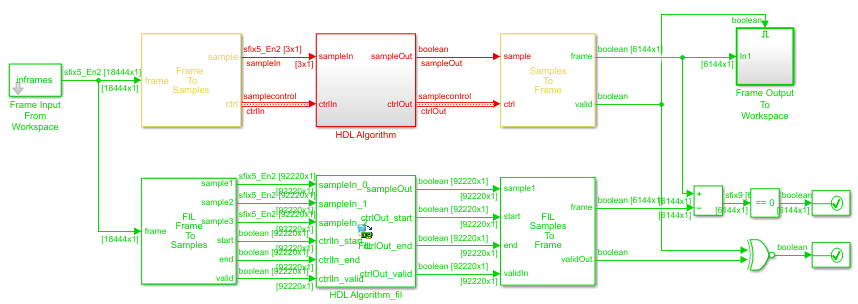

Чтобы улучшить коммуникационную полосу пропускания с платой FPGA, измените автоматически сгенерированную модель. Модифицированная модель использует FIL Frame To Samples и блоки FIL Samples To Frame, чтобы передать один кадр за один раз.

Создать эту модифицированную модель FIL:

Удалите синие подсистемы и создайте ветвь во входном порту frame блока Frame To Samples.

Вставьте блок FIL Frame To Samples перед блоком HDL Algorithm_fil. Вставьте блок FIL Samples To Frame после блока HDL Algorithm_fil.

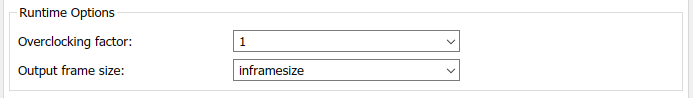

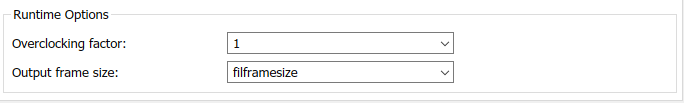

Установите Output frame size на блоке FIL к размеру входного кадра.

В FIL Frame To Samples и блоках FIL Samples To Frame, установленных параметры, чтобы совпадать с настройками Frame To Samples и блоков Samples To Frame.

Ветвь система координат выход блока Samples To Frame для сравнения. Можно сравнить целую систему координат целиком с блоком Diff. Сравните validOut сигналы с помощью блока XOR.

Входной размер в блоке FIL является форматом кадра от систем координат входных данных. Размер вектора портов блока FIL не изменяет сгенерированный HDL-код. Это влияет только на пакетный размер связи между средством моделирования и платой FPGA. Эта модифицированная модель передает целый кадр к плате FPGA в каждом пакете, значительно повысив эффективность линии связи.

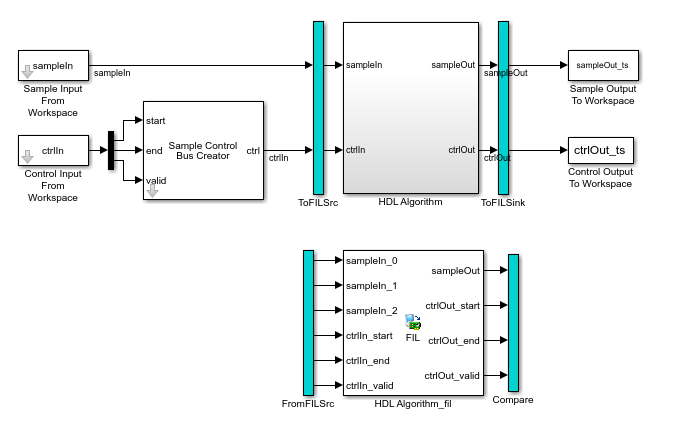

Сгенерированную модель, включая блок FIL, который взаимодействует через интерфейс с платой FPGA, показывают для модели, которая преобразует в потоковую передачу выборок в MATLAB. Если каждая выборка представлена несколькими значениями, то значения сглажены в отдельные порты для FIL.

Синяя подсистема ToFILSrc переходит демонстрационный потоковый ввод блока HDL Algorithm к подсистеме FromFILSrc. Синяя подсистема ToFILSink переходит демонстрационный поток выход блока HDL Algorithm в подсистему Compare, где это по сравнению с выходом блока HDL Algorithm_fil. Эта настройка является медленной, потому что модель отправляет только одну выборку и ее связанные управляющие сигналы, в каждом пакете к и от платы FPGA.

Чтобы улучшить коммуникационную полосу пропускания с платой FPGA, используйте сгенерированный блок FIL в различной модели. Альтернативная модель импортирует и экспортирует векторы из сглаженных данных. Сопроводительный скрипт MATLAB изменяет входные и выходные данные и проверяет FIL выход по поведенческой модели. Изменение данных в MATLAB легче, и симуляция быстрее, чем изменение в Simulink.

Во-первых, измените сопроводительный скрипт MATLAB:

Выберите формат кадра для симуляции FIL. Этот размер не должен совпадать с фактическими форматами кадра в сгенерированных данных. Это может содержать ваш целый набор данных. Блок FIL делит данные на максимальные пакеты размера для связи с платой FPGA.

filframesize = 99;

Объедините массив ячеек входных кадров в одну матрицу.

allframes = [inframes{:}];

Сгладьте выборки и управляющие сигналы, таким образом, существует один вектор для каждого входного порта на блоке FIL. Эта модель включает блок LTE Turbo Decoder, таким образом, входные выборки состоят из трех значений.

sysIn = allframes(1:3:end); p1In = allframes(2:3:end); p2In = allframes(3:3:end); ctrlstartIn = ctrlIn(1:3:end); ctrlendIn = ctrlIn(2:3:end); ctrlvalidIn = ctrlIn(3:3:end);

Вызовите модель FIL.

simTime = size(allframes,1);

modelname = 'TurboDecoderStreamingFILVectortoSL';

open_system(modelname);

sim(modelname);

Измените выходные переменные для входа к whdlSamplesToFrames функция. Воссоздайте N-by-3 матрица управляющего сигнала и вектор из выборочных данных. В этом примере выходная выборка является одним значением. Если выходная выборка является несколькими значениями, создайте N-by-SampleSize демонстрационная матрица.

sampleOut = squeeze(sampleOut_ts.Data); ctrlOut = [squeeze(ctrlstartOut_ts.Data) ... squeeze(ctrlendOut_ts.Data) ... squeeze(ctrlvalidOut_ts.Data)];

Затем создайте модель Simulink:

Скопируйте сгенерированный блок FIL в новую модель.

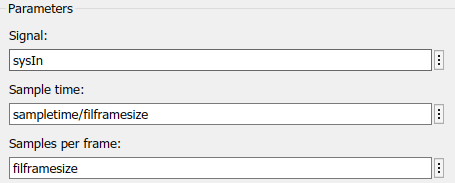

Сконфигурируйте и соедините блок Signal From Workspace для каждого входного порта на блоке FIL. Используйте переменные из своего скрипта MATLAB как значения параметров.

Установите Output frame size на блоке FIL к желаемому формату кадра FIL.

Сконфигурируйте и соедините блок To Workspace для каждого выходного порта блока FIL.

Входной размер в блоке FIL является форматом кадра, который вы задаете на блоках Signal To Workspace. Размер вектора портов блока FIL не изменяет сгенерированный HDL-код. Это влияет только на пакетный размер связи между средством моделирования и платой FPGA. Эта модифицированная модель передает целый кадр к плате FPGA в каждом пакете, значительно повысив эффективность линии связи.