Блоки библиотеки Simulink® Model Verification оценивают сигналы временного интервала в вашей модели, согласно спецификациям, которые вы присваиваете блокам. Для отдельной блочной справочной информации смотрите Образцовую категорию Верификации.

Образцовые блоки Верификации возвращают утверждение, когда сигналы выходят за пределы заданного предела или области значений. Во время моделирования, когда сигнал пересекает предел, может блок верификации:

Остановите моделирование и принесите мгновенное особое внимание на ту часть модели.

Сообщите об отказе с логическим сигналом. Если сигнал не перестал работать, сигнал вывел, true. Если моделирование перестало работать, выводом сигнала является false.

Можно использовать менеджера по Верификации графический интерфейс в диалоговом окне Signal Builder, чтобы управлять Образцовыми блоками Верификации в модели.

Если вы имеете Контроль Simulink Design™, можно также контролировать характеристики частотного диапазона, такие как усиление и поля фазы и пиковое значение. Для получения дополнительной информации смотрите Образцовую Верификацию (Simulink Control Design).

Этот пример показывает, как использовать менеджера по Верификации, чтобы включить и отключить определенные Образцовые блоки Верификации для определенных групп Signal Builder.

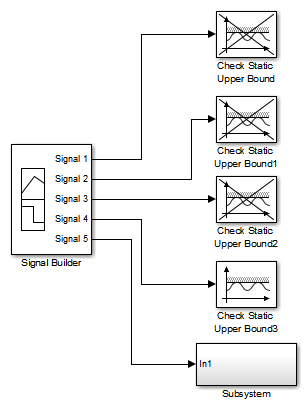

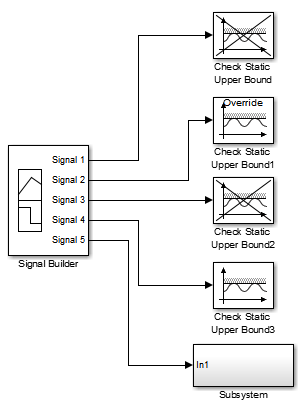

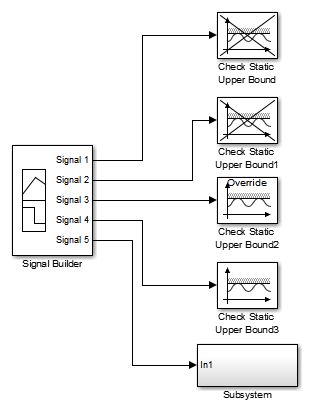

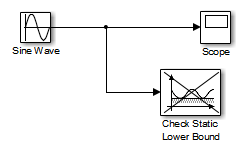

Создайте модель Simulink, которую можно использовать, чтобы исследовать менеджера по Верификации. Создайте следующую модель в качестве примера в перезаписываемом месте на пути MATLAB®.

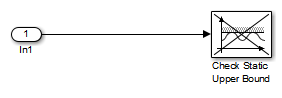

В модели в качестве примера содержимое подсистемы следующие.

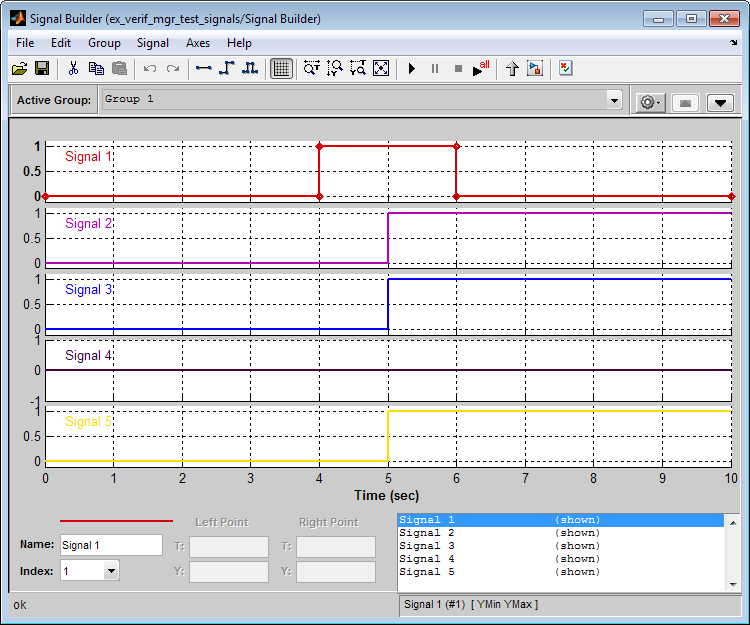

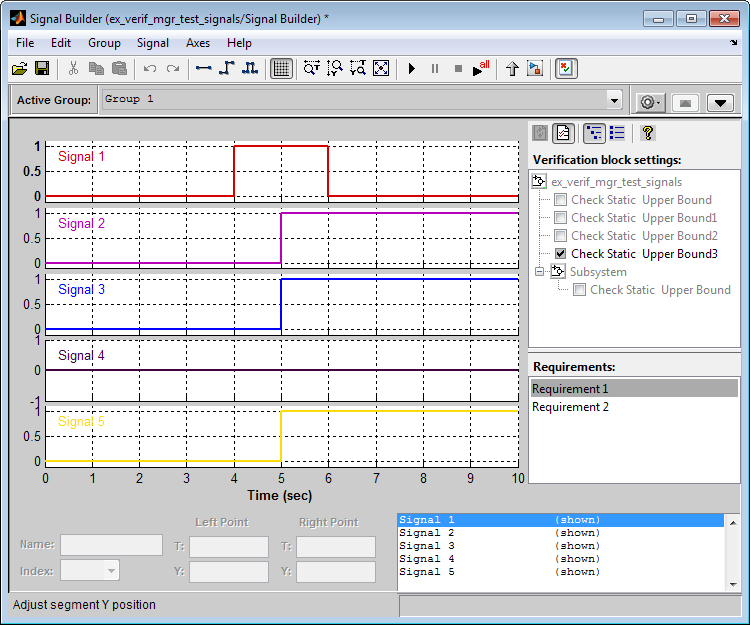

В блоке Signal Builder создайте группу сигнала с пятью сигналами в группе.

Сделайте две копии группы сигнала, так, чтобы у вас было три группы сигнала: Группа 1, Группа 2, Группа 3.

Блок Signal Builder обеспечивает тестовые сигналы для целой модели от одного местоположения. Эта модель содержит блок Signal Builder, который подает пять тестовых сигналов к Образцовым блокам Верификации. Модель отправляет первые четыре сигнала непосредственно, чтобы Проверить Статические блоки Верхней границы. Модель отправляет пятый сигнал в подсистему, которая содержит блок Check Static Upper Bound.

Для получения дополнительной информации о блоке Signal Builder смотрите Signal Groups.

Чтобы установить каждую Проверку Статический блок верификации Верхней границы утверждать для верхней границы 1, установите параметр Верхней границы на 1.

Для следующих блоков отключите утверждение путем очистки Разрешать параметра утверждения:

Проверьте статическую верхнюю границу

Проверьте статический верхний Bound1

Проверьте статический верхний Bound2

Проверьте Статическую Верхнюю границу в подсистему

Эти блоки вычеркнуты в модели.

Чтобы включить блок Check Static Upper Bound3, выберите параметр утверждения Enable.

Сохраните эту модель и назовите ее ex_verif_mgr_test_signals.

Чтобы открыть образцовое диалоговое окно Signal Builder, дважды кликните блок Signal Builder. Сигналы в первой группе (Группа 1 в этом примере) отображены.

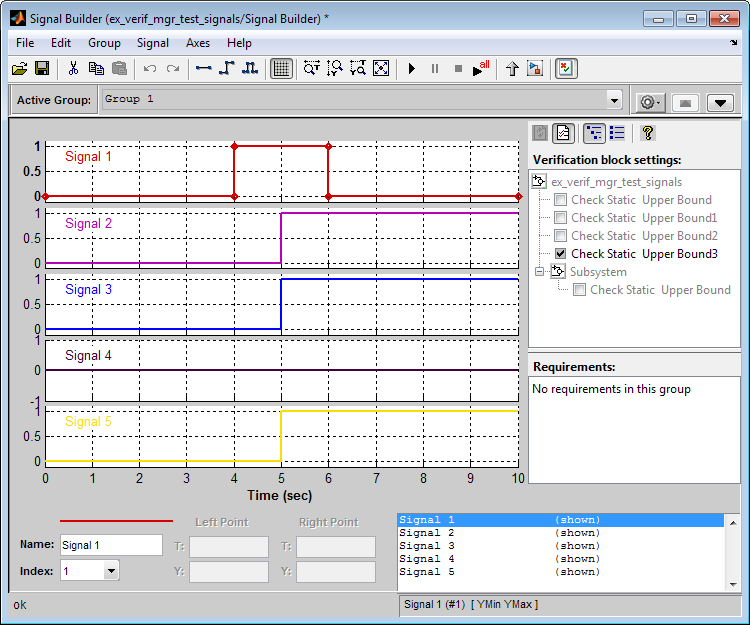

На панели инструментов диалогового окна Signal Builder выберите инструмент Show Verification Settings.![]()

Панель настроек блока Verification и Панель Requirements отображены.

Панель настроек блока Verification перечисляет все Образцовые блоки Верификации в модели, сгруппированной подсистемой. Если вы щелкаете правой кнопкой по этой панели, можно выбрать на трех опций для просмотра Образцовых блоков Верификации в этом окне:

Отобразитесь> Древовидный формат — Если включено, перечисляет блоки, когда они появляются в иерархии модели.

Отобразитесь> Замененные блоки только — Если включено, списки только блоки, которые были отключены.

Отобразитесь> Активные блоки только — Если включено, списки только блоки, которые включены.

Если и Замененные блоки только и Активные блоки только включены, никакие Образцовые блоки Верификации не появляются. Если и Замененные блоки только и Активные блоки только отключены, все Образцовые блоки Верификации появляются.

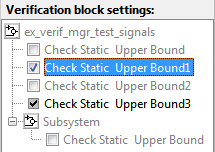

В этом примере панель настроек блока Verification отображает пять Проверок Статические блоки Верхней границы. Четыре находятся в верхнем уровне модели, и каждый находится в подсистеме.

Панель Requirements перечисляет ссылки на документ требований для текущей группы сигнала. Для получения дополнительной информации на добавляющих ссылках на документ требования в диалоговом окне Signal Builder, смотрите Тесты Ссылки к Документам Требований Используя менеджера по Верификации.

Для этого примера выберите![]() , чтобы закрыть Панель Requirements.

, чтобы закрыть Панель Requirements.

Чтобы отобразить только активированные Образцовые блоки Верификации для текущей группы сигнала, на панели инструментов настроек блока Verification, выбирают инструмент List Enabled Verifications![]() .

.

Чтобы вновь отобразить все Образцовые блоки Верификации для текущей группы, кликните по инструменту Show Verification Block Hierarchy![]() .

.

Используйте менеджера по Верификации, чтобы включить и отключить отдельные Образцовые блоки Верификации в группах сигнала. Чтобы открыть менеджера по Верификации в диалоговом окне Signal Builder, щелкнуть![]() .

.

Панель настроек блока Verification перечисляет Образцовые блоки Верификации в модели. Каждый блок верификации имеет узел состояния, который указывает, включено ли его утверждение или отключено. Каждый узел состояния блока верификации также указывает, применяется ли активированная или отключенная установка универсально или к активной группе. Следующая таблица описывает различные типы узлов состояния.

Узел | Состояние |

|---|---|

| Блок Verification отключен для этой группы. Щелкните, чтобы включить для текущей группы. |

| Блок Verification включен для текущей группы. Щелкните, чтобы отключить для текущей группы. |

| Блок Verification включен для всех тестовых групп. |

Используйте менеджера по Верификации, чтобы включить или отключить образцовые блоки верификации в модели ex_verif_mgr_test_signals, что вы создали в поле зрения Образцовые Блоки Верификации.

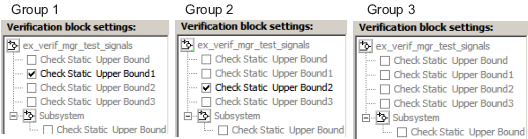

В менеджере по Верификации кликните по пустому флажку рядом с Проверкой Статический Верхний узел Bound1, чтобы включить тот узел для текущей активной группы (Группа 1).

В панели настроек блока Verification, когда вы включаете отключенный блок, вы видите следующее изменение в том, как блок отображен в модели.

Поскольку вы включили блок Check Static Upper Bound1 в текущей группе, метка Переопределения применяется к блоку, и это больше не вычеркивается.

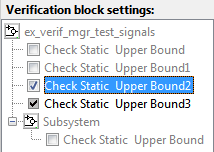

В Signal Builder, из списка Active Group, выбирают Group 2.

Установите пустой флажок рядом с Проверкой Статический Верхний узел Bound2, чтобы включить тот блок для текущей группы (Группа 2).

Блок Check Static Upper Bound2 больше не вычеркивается, указывая, что блок включен для текущей группы. Проверьте, что Статический Верхний Bound1, однако, вычеркнут, потому что он включен в другой группе.

Сохраните модель с этими изменениями.

Если у вас есть много блоков верификации, это утомительно, чтобы включить и отключить блоки индивидуально. Используя менеджера по Верификации, можно включить и отключить блоки из опций контекстного меню. В зависимости от состояния узла у вас есть следующие опции.

Состояние узла | Опции контекстного меню |

|---|---|

|

|

|

|

|

|

|

|

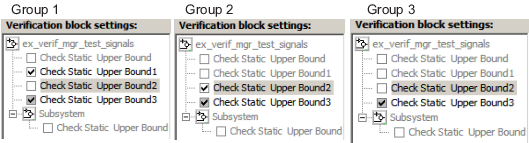

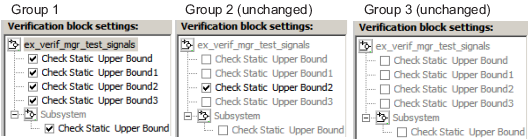

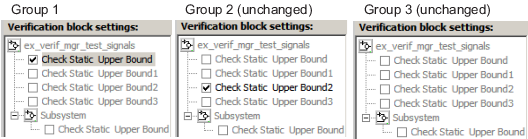

Например, примите, что вы задаете следующие группы в менеджере по Верификации по модели с пятью Образцовыми блоками Верификации.

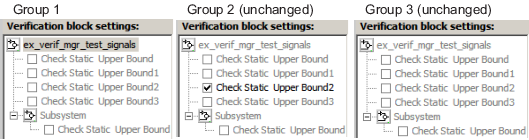

В окне Verification Manager щелкните правой кнопкой по узлу ex_verif_mgr_test_signals и выберите Contents, включают для всех групп.

Эта опция включает все блоки верификации, для всех тестовых групп, во всех подсистемах; настройки для всех групп смотрят можно следующим образом:

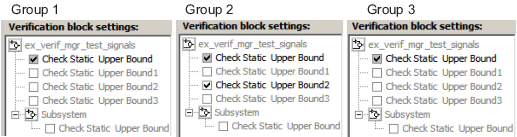

Щелкните правой кнопкой по ex_verif_mgr_test_signals и выберите Contents, включают группой.

Эта опция восстанавливает индивидуально активированные/отключенные настройки для каждого блока верификации в каждой группе.

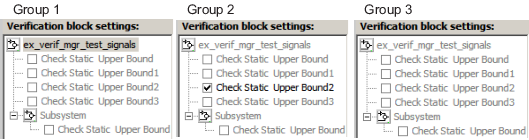

Из списка Active Group выберите Group 1. Щелкните правой кнопкой по ex_verif_mgr_test_signals и выберите группу Contents, включают.

Эта опция индивидуально включает все содержавшие блоки для только Группы 1.

Из списка Active Group выберите Group 1. Щелкните правой кнопкой по ex_verif_mgr_test_signals и выберите группу Contents, отключают.

Эта опция индивидуально отключает все содержавшие блоки для только Группы 1.

Из списка Active Group выберите Group 1. Щелкните правой кнопкой по Проверке Статический узел Верхней границы и выберите Block, включают для всех групп.

Эта опция включает блок Check Static Upper Bound для всех групп.

Из списка Active Group выберите Group 1. Щелкните правой кнопкой по Проверке Статический узел Верхней границы и выберите Block, включают группой.

Эта опция восстанавливает индивидуально активированное / нерабочее состояние к этому блоку для всех групп. Блок включает опцией группы, позволяет вам включить или отключить этот узел индивидуально для каждой группы.

Из списка Active Group выберите Group 1. Щелкните правой кнопкой по Проверке Статический узел Верхней границы и выберите группу Block, включают.

Эта опция включает блок Check Static Upper Bound для этой группы только.

Выбор группы Block отключает, отключает заданный блок для этой группы только.

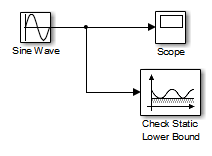

Следующий пример использует блок Check Static Lower Bound, чтобы остановить моделирование, когда сигнал от блока Sine Wave пересекает свой предел нижней границы.

Присоедините блок Check Static Lower Bound к сигналу от блока Sine Wave.

Установите время остановки Моделирования на 2 секунды.

Дважды кликните блок Sine Wave и установите следующие параметры:

Установите амплитуду на 1.

Установите Частоту на радианы pi в секунду.

Дважды кликните блок Check Static Lower Bound и установите параметр Нижней границы на -0.8.

Включите утверждение, значение по умолчанию. Этот параметр включает блок верификации для утверждения. Вы устанавливаете блок Check Static Lower Bound обнаруживать значение сигналов –0.8 или ниже. Если значение сигналов достигает того значения или падений ниже его, остановок моделирования.

Запустите моделирование.

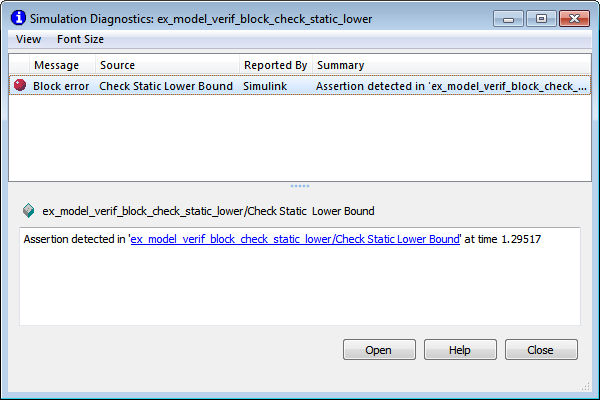

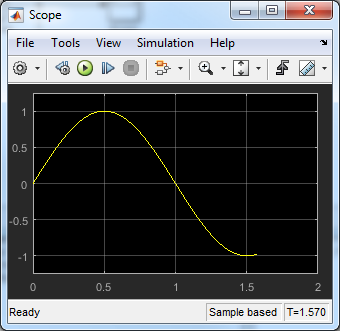

Модель прекращает моделировать после 1,295 секунд, когда вывод –0.8. Программное обеспечение подсвечивает блок Check Static Lower Bound.

Когда моделирование останавливается, вы видите следующее диагностическое сообщение.

Чтобы проверить значение сигналов, дважды кликните блок Scope.

Чтобы отключить блок Check Static Lower Bound от утверждения его предела, снимите Разрешать флажок утверждения.

Блок вычеркнут в модели, как показано.

С Simulink Requirements™ можно соединить документы требований тестам и их соответствующим Образцовым блокам Верификации через менеджера по Верификации Панель Requirements в Signal Builder.

Отобразить Панель Requirements в диалоговом окне Signal Builder:

Нажмите кнопку настроек верификации Show (![]() ).

).

Кликните по кнопке отображения Требований (![]() ).

).

Из контекстного меню выберите Link Editor.

Диалоговое окно Requirements открывается.

Когда вы просматриваете и выбираете документ требований, RMI хранит путь к документу, как задано опцией ссылки Файла документа на диалоговом окне Requirements Settings, вкладке Selection Linking.

Добавьте ссылки к документам требований, как описано в Requirements Management Interface (Simulink Requirements).

Имена соединенных требований появляются в Панели Requirements.

Чтобы просмотреть документ требований в его нативном редакторе, щелкните правой кнопкой по ссылке требования и выберите View.

Опционально, чтобы удалить ссылку требования, щелкните правой кнопкой по ссылке и выберите Delete.

Если у вас есть программное обеспечение Simulink Control Design, вы можете:

Задайте границы на характеристиках линейной системы.

Проверьте, что границы удовлетворены во время моделирования.

Например, можно проверить, удовлетворило ли линеаризовавшее поведение модели верхние и более низкие границы значения на Графике Боде или полях фазы и усилении. Для получения дополнительной информации смотрите отдельные блочные страницы с описанием в Образцовой Верификации (Simulink Control Design).