Программное обеспечение HDL Coder™ предоставляет возможности архитектуры, которые расширяют ваше управление скоростью по сравнению с компромиссами области в реализации проектов фильтра. Чтобы достигнуть желаемого компромисса для сгенерированного HDL-кода, можно или задать полностью параллельную архитектуру или выбрать одну из нескольких последовательной архитектуры. Сконфигурируйте последовательную архитектуру с помощью SerialPartition (HDL Coder) и ReuseAccum (HDL Coder) параметры. Можно также выбрать основанный на кадре фильтр для увеличенной пропускной способности.

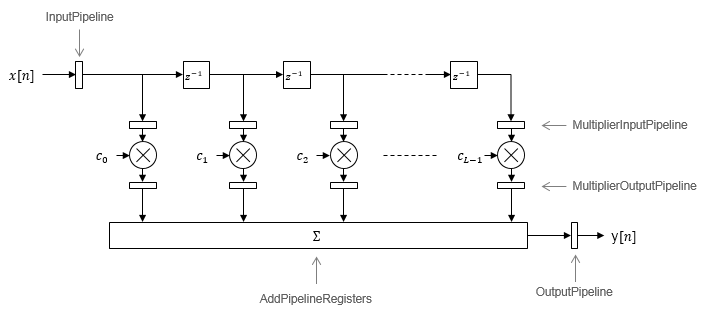

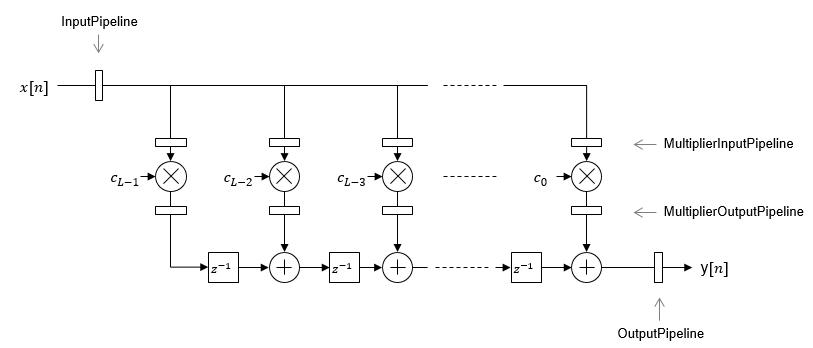

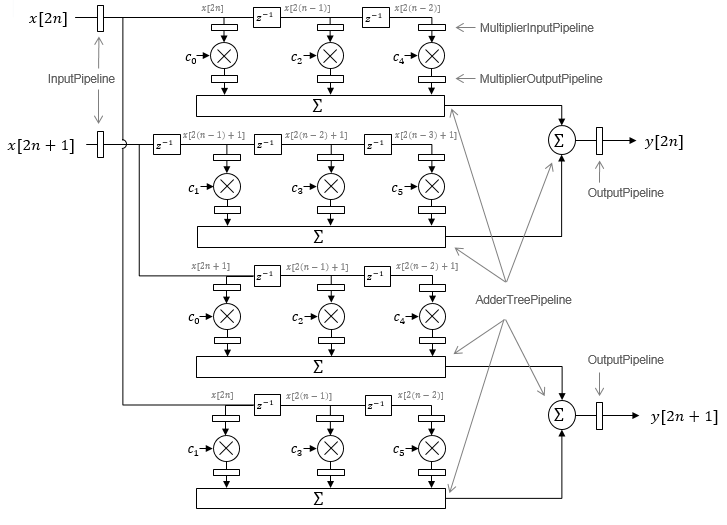

Используйте параметры конвейеризации, чтобы улучшить быстродействие ваших проектов фильтра. Добавьте конвейеры в логику сумматора вашего использования фильтра AddPipelineRegisters (HDL Coder) для скалярных входных фильтров и AdderTreePipeline (HDL Coder) для основанных на кадре фильтров. Задайте настройки канала связи до и после каждого множителя с MultiplierInputPipeline (HDL Coder) и MultiplierOutputPipeline (HDL Coder). Определите номер настроек канала связи до и после использования фильтра InputPipeline (HDL Coder) и OutputPipeline (HDL Coder). Схемы архитектуры показывают местоположения различных конфигурируемых настроек канала связи.

Эта опция является архитектурой по умолчанию. Полностью параллельная архитектура использует специализированный множитель и сумматор для каждого касания фильтра. Касания выполняются параллельно. Полностью параллельная архитектура оптимальна для скорости. Однако это требует большего количества множителей и сумматоров, чем последовательная архитектура, и поэтому использует больше области чипа. Схемы показывают архитектуру для прямой формы и для транспонированных структур фильтра с полностью параллельными реализациями и местоположения конфигурируемых настроек канала связи.

По умолчанию блок реализует линейную логику сумматора. Когда вы включаете AddPipelineRegisters, логика сумматора реализована как конвейерное дерево сумматора. Дерево сумматора использует типы данных полной точности. Если вы генерируете модель валидации, необходимо использовать полную точность в исходной модели, чтобы избежать несоответствий валидации.

Параметр AddPipelineRegisters не имеет никакого эффекта на транспонированную реализацию фильтра.

Последовательные аппаратные ресурсы повторного использования архитектуры вовремя, сохраняя область чипа. Сконфигурируйте последовательную архитектуру с помощью SerialPartition (HDL Coder) и ReuseAccum (HDL Coder) параметры. Доступные последовательные опции архитектуры полностью последовательны, частично последовательный, и каскадный сериал.

Полностью последовательный: полностью последовательная архитектура сохраняет область путем многократного использования множителя и ресурсов сумматора последовательно. Например, проект фильтра с четырьмя касаниями использовал бы один множитель и сумматор, выполняя умножиться/накопить операцию однажды для каждого касания. Умножиться/накопить раздел проекта достигает четыре раза частоты дискретизации ввода/вывода фильтра. Это сохраняет область за счет некоторой потери скорости и более высокого потребления энергии.

В полностью последовательной архитектуре системные часы запускаются на намного более высоком уровне, чем частота дискретизации фильтра. Таким образом, для данного проекта фильтра, максимальная скорость, достижимая полностью последовательной архитектурой, будет меньше, чем та из параллельной архитектуры.

Частично последовательный: Частично последовательная архитектура покрывает полный спектр скорости по сравнению с компромиссами области, которые находятся между полностью параллельной и полностью последовательной архитектурой.

В частично последовательной архитектуре касания фильтра сгруппированы во многие последовательные разделы. Касания в каждом разделе выполняются последовательно, но разделы выполняются параллельно друг относительно друга. Выходные параметры разделов суммированы в окончательном результате.

Когда вы выбираете частично последовательную архитектуру, вы задаете количество разделов и длины (количество касаний) каждого раздела. Например, вы могли задать фильтр с четырьмя касаниями с двумя разделами, каждый имеющий два касания. Системные часы запустились бы на уровне дважды частоты дискретизации фильтра.

Каскадно-последовательный: каскадно-последовательная архитектура тесно напоминает частично последовательную архитектуру. Как в частично последовательной архитектуре, касания фильтра сгруппированы во многие последовательные разделы, которые выполняются параллельно друг относительно друга. Однако накопленный вывод каждого раздела располагается каскадом к аккумулятору предыдущего раздела. Вывод всех разделов поэтому вычисляется в аккумуляторе первого раздела. Этот метод называют повторным использованием аккумулятора. Итоговый сумматор не требуется, который сохраняет область.

Каскадно-последовательная архитектура требует, чтобы дополнительный цикл системных часов завершил итоговое суммирование к выводу. Поэтому частота системных часов должна быть увеличена немного относительно часов, используемых в некаскаде частично последовательная архитектура.

Чтобы сгенерировать каскадно-последовательную архитектуру, задайте частично последовательную архитектуру с включенным повторным использованием аккумулятора. Если вы не задаете последовательные разделы, HDL Coder автоматически выбирает оптимальное разделение.

Полностью последовательная архитектура сохраняет область путем многократного использования множителя и ресурсов сумматора последовательно. Например, проект фильтра с четырьмя касаниями использует один множитель и сумматор, выполнение умножения - накапливает операцию однажды для каждого касания. Умножение - накапливается, раздел проекта достигает четыре раза частоты дискретизации ввода/вывода фильтра. Этот проект сохраняет область за счет некоторой потери скорости и более высокого потребления энергии.

В полностью последовательной архитектуре системные часы запускаются на намного более высоком уровне, чем частота дискретизации фильтра. Таким образом, для данного проекта фильтра, максимальная скорость, достижимая полностью последовательной архитектурой, является меньше, чем та из параллельной архитектуры.

Частично последовательная архитектура покрывает полный спектр скорости по сравнению с компромиссами области, которые находятся между полностью параллельной и полностью последовательной архитектурой.

В частично последовательной архитектуре касания фильтра сгруппированы во многие последовательные разделы. Касания в каждом разделе выполняются последовательно, но разделы выполняются параллельно друг относительно друга. Выходные параметры разделов суммированы в окончательном результате.

Когда вы выбираете частично последовательную архитектуру, вы задаете количество разделов и длины (количество касаний) каждого раздела. Предположим, что вы задаете фильтр с четырьмя касаниями с двумя разделами, каждый имеющий два касания. Системные часы запускаются на уровне дважды частоты дискретизации фильтра.

Каскадно-последовательная архитектура тесно напоминает частично последовательную архитектуру. Как в частично последовательной архитектуре, касания фильтра сгруппированы во многие последовательные разделы, которые выполняются параллельно друг относительно друга. Однако накопленный вывод каждого раздела располагается каскадом к аккумулятору предыдущего раздела. Вывод всех разделов поэтому вычисляется в аккумуляторе первого раздела. Этот метод называют повторным использованием аккумулятора. Итоговый сумматор не требуется, который сохраняет область.

Каскадно-последовательная архитектура требует, чтобы дополнительный цикл системных часов завершил итоговое суммирование к выводу. Поэтому частота системных часов должна быть увеличена немного относительно часов, используемых в некаскаде частично последовательная архитектура.

Чтобы сгенерировать каскадно-последовательную архитектуру, задайте частично последовательную архитектуру с включенным повторным использованием аккумулятора. Если вы не задаете последовательные разделы, HDL Coder автоматически выбирает оптимальное разделение.

Сериализация фильтра увеличивает общую задержку проекта одним тактом. Последовательная архитектура использует аккумулятор (сумматор с регистром), чтобы добавить продукты последовательно. Дополнительный итоговый регистр используется, чтобы сохранить суммированный результат всех последовательных разделов, требуя дополнительного такта для операции. Чтобы обработать задержку, HDL Coder вставляет блок Delay в сгенерированную модель после блока фильтра.

Когда вы выбираете последовательную архитектуру, генератор кода использует полную точность в HDL-коде. HDL Coder поэтому обеспечивает полную точность в сгенерированной модели. Если вы генерируете модель валидации, необходимо использовать полную точность в исходной модели, чтобы избежать несоответствий валидации.

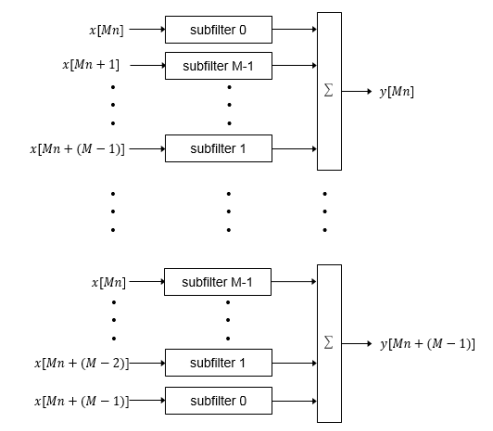

Когда вы выбираете основанную на кадре архитектуру и обеспечиваете M - демонстрационный входной кадр, кодер реализует полностью параллельную архитектуру фильтра. Фильтр включает подфильтры параллели M для каждой входной выборки.

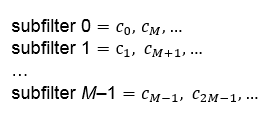

Каждый из подфильтров включает каждый M th коэффициент. Результаты подфильтра добавляются так, чтобы каждая выходная выборка была суммой каждого из коэффициентов, умноженных с одной входной выборкой.

Схема показывает архитектуру фильтра для формата кадра двух выборок (M = 2), и длина фильтра шести коэффициентов. Вход является вектором с двумя значениями, представляющими выборки вовремя. Входные выборки, x[2n] и x[2n+1], представляют n th входная пара. Каждая вторая выборка от каждого потока питается два параллельных подфильтра. Четыре результата подфильтра добавляются вместе, чтобы создать две выходных выборки. Таким образом каждая выходная выборка является суммой каждого из коэффициентов, умноженных с одной из входных выборок.

Суммы реализованы как конвейерное дерево сумматора. Установите AdderTreePipeline (HDL Coder) задавать количество настроек канала связи между уровнями дерева сумматора. Чтобы улучшить тактовую частоту, рекомендуется, чтобы вы установили этот параметр на 2. Чтобы вместить множители в блоки DSP на вашем FPGA, добавьте настройки канала связи до и после использования множителей MultiplierInputPipeline (HDL Coder) и MultiplierOutputPipeline (HDL Coder).

Для симметричных или антисимметричных коэффициентов архитектура фильтра снова использует содействующие множители и добавляет задержку проекта между множителем и этапами суммирования как требуется.