Генератор кода производит код из модели Simulink®, содержащей один или несколько Различная Подсистема, Различный Источник и Различные блоки Приемника. Чтобы изучить, как создать модель, содержащую различные блоки, смотрите, Создают Простую Различную Модель (Simulink). Чтобы изучить, как создать пользовательскую проверку Model Advisor, которая оценивает сгенерированный код от активных и неактивных различных путей в модели вариантной системы, смотрите, Создают Собственную проверку, чтобы Оценить Активные и Неактивные Различные Пути из Модели (Simulink Check).

Во время генерации кода может быть выведено предупреждение, связанное с 'Функцией генерации кода, группирующей' для блока Variant. В диалоговом окне параметров блоков блока Variant нажмите Code Generation и затем выберите Reusable function из Function packaging выпадающий список, чтобы решить эту проблему.

Код сгенерирован для различных вариантов, активного варианта и варианта по умолчанию. Чтобы сгенерировать код для вариантов, установите следующие условия в Различной Подсистеме, Различном Источнике или блоке Variant Sink:

Выберите Expression как Variant Control mode от диалогового окна параметров блоков.

Выберите опцию Analyze all choices during update diagram and generate preprocessor conditionals.

Код, сгенерированный для Различных блоков Subsystem, окружается условными выражениями препроцессора C #if, #else, #elif и #endif. Код, сгенерированный для Различного Источника и Различных блоков Приемника, окружается условными выражениями препроцессора C #if и #endif. Поэтому активный вариант выбран во время компиляции, и условные выражения препроцессора определяют который разделы кода выполниться.

Чтобы создать различные модели и сгенерировать директивы препроцессору в сгенерированном коде, см. Модели Варианта Использования в качестве примера, чтобы Сгенерировать Код Который Использование C Условные выражения Препроцессора.

Чтобы создать различные подсистемы и сгенерировать директивы препроцессору в сгенерированном коде, смотрите Подсистему Варианта Использования в качестве примера, Чтобы Сгенерировать Код Который Использование C Условные выражения Препроцессора.

Чтобы создать модели с различными источниками и приемниками и сгенерировать директивы препроцессору в сгенерированном коде, смотрите, что пример Представляет Различные Блоки Источника и Приемника в Сгенерированном коде.

Чтобы сгенерировать условные выражения препроцессора, типы блоков, которые можно поместить в дочерних подсистемах Различного блока Subsystem, ограничиваются. Связи не позволены в Различной схеме блока Subsystem. Однако во время процесса генерации кода, один блок VariantMerge помещается во вход каждого блока Outport в рамках Различной схемы блока Subsystem. Все дочерние подсистемы соединяются с каждым из блоков VariantMerge.

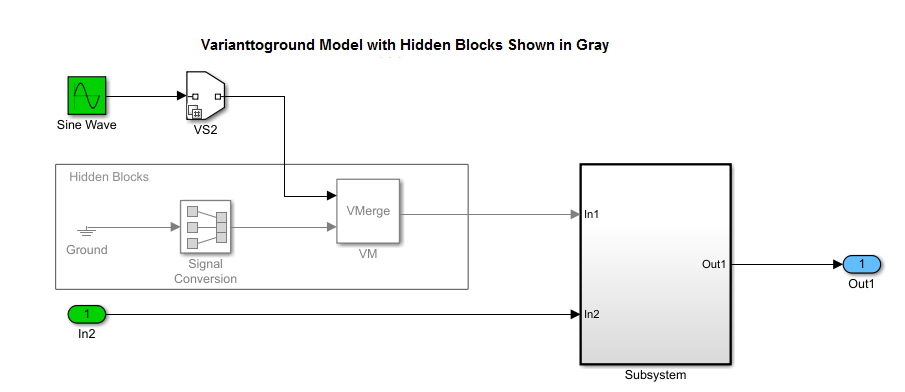

В фигуре ниже, процесс генерации кода устанавливает следующие связи и добавляет блоки VariantMerge в sldemo_variant_subsystems модель.

Когда по сравнению с типичным блоком Merge блок VariantMerge может иметь только один параметр, который является количеством Входных параметров. Блок VariantMerge используется для генерации кода в различных подсистемах внутренне и не доступен внешне, чтобы использоваться в моделях. Количество входных параметров для VariantMerge определено и соединено проводом как показано в фигуре ниже.

Дочерние подсистемы Различного блока Subsystem должны быть атомарными подсистемами. Выберите параметр Treat as atomic unit в диалоговом окне параметров блока Subsystem, чтобы сделать подсистемы атомарными. Блоки VariantMerge вставляются в выходном порту подсистем, если больше чем одна дочерняя подсистема присутствует. Если исходный блок входа блока VariantMerge будет невиртуальным, сообщение об ошибке будет отображено во время генерации кода. Необходимо сделать исходный блок непрерывным путем вставки блоков Преобразования Сигнала в вариантах. Сигналы, которые вводят Различный блок Subsystem, должны иметь те же свойства сигнала (например, размерности сигнала, порт width и класс памяти). Блок VariantMerge не поддерживает различные свойства сигнала, потому что входные порты и выходные порты совместно используют ту же память. Можно использовать символьные размерности, чтобы сгенерировать код для различной подсистемы с дочерними подсистемами различных размерностей выходного сигнала.

Следующие компоненты условно не скомпилированы, даже если только код для различных подсистем или модели, которые условно скомпилированы ссылка их.

Поля структуры данных rtModel

#include служебных файлов

Глобальные постоянные поля структуры параметра, на которые ссылаются несколько подсистем, активированных различными вариантами

Параметры, которые сконфигурированы, чтобы использовать импортированный, экспортируемый или класс памяти генерации пользовательского кода, и ссылаются несколькими подсистемами, которые активируются различными вариантами

Параметры, которые сконфигурированы, чтобы использовать импортированный, экспортируемый или класс памяти генерации пользовательского кода, и используются различными блоками модели

Для моделирования шаблонов, в которых блок Root Inport соединяется с блоком Variant с одним вариантом, Simulink вставляет скрытую комбинацию блока блока Ground, блока Signal Conversion и блока Variant Merge. Если вариант оценивает ко лжи, эта комбинация блока производит вывод 0.0.

Например, модель Varianttoground содержит Различный Исходный блок с одним вариантом. Когда Различное Управление, которое SYSCONST_A==6 оценивает к истине, входу к Subsystem, является синусоидой. Когда SYSCONST_A==6 оценивает ко лжи, входом к Subsystem является 0.0.

Файл varianttoground.c содержит этот код:

/* Sin: '<Root>/Sine Wave' */

#if SYSCONST_A == 6

varianttoground_B.VM_Conditional_Signal_Subsystem_0_r64 = sin

(varianttoground_M->Timing.t[0]);

#endif /* SYSCONST_A == 6 */

/* End of Sin: '<Root>/Sine Wave' */

/* SignalConversion: '<Root>/VM_SignalConversion_Subsystem_0' */

#if SYSCONST_A != 6

varianttoground_B.VM_Conditional_Signal_Subsystem_0_r64 = 0.0;

#endif /* SYSCONST_A != 6 */

/* End of SignalConversion: '<Root>/VM_SignalConversion_Subsystem_0' */

Комментарии в сгенерированном коде указывают на присутствие скрытого блока преобразования сигнала. Код не содержит комментарий для блока Variant Merge, потому что этот блок не имеет сопоставленного сгенерированного кода. Блок Variant Merge используется внутренне и не находится в Библиотеке Simulink.

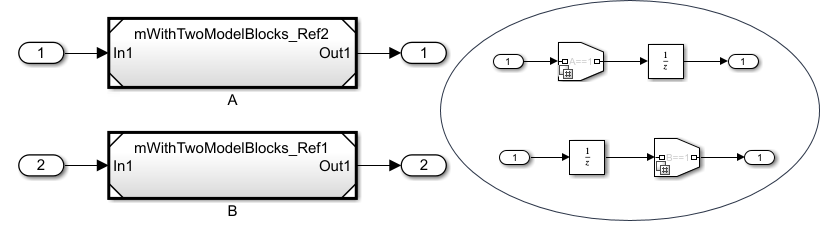

Когда модель имеет блоки Модели - ссылки, которые являются условным выражением, должным встраивать варианты, заголовочный файл и экземпляры, относящиеся к блокам Модели - ссылки, охраняют.

Рассмотрите эту модель с двумя блоками Моделей - ссылок, которые являются условным выражением, должным встраивать варианты.

Когда вы генерируете код для этой модели, заголовочный файл и экземпляры, относящиеся к блокам Модели - ссылки, охраняют как показано в коде ниже.

#include "mWithTwoModelBlocks_Top_types.h" #include "multiword_types.h" #if (A == 1) //Guarding #define mWithTwoModelBlocks_Ref2_MDLREF_HIDE_CHILD_ #include "mWithTwoModelBlocks_Ref2.h" #endif #if (B == 1) //Guarding #include "mWithTwoModelBlocks_Ref1.h" #endif