HDL Coder™ может сгенерировать код VHDL и Verilog из алгоритмов MATLAB®, моделей Simulink® и графиков Stateflow®. Можно затем проверить, что сгенерированный код совпадает исходным алгоритмом, и разверните его на целевом компьютере.

Этот пример иллюстрирует, как можно использовать HDL Coder, чтобы сгенерировать и синтезировать HDL-код для алгоритма MATLAB, который реализует простой фильтр.

Этот пример использует эти файлы:

mlhdlc_sfir.m — Простая функция filter, от которой вы генерируете HDL-код. Видеть, что код MATLAB для КИХ фильтрует алгоритм в командной строке, введите:

edit('mlhdlc_sfir')mlhdlc_sfir_tb.m — Испытательный стенд, что использование проекта HDL Coder, чтобы моделировать фильтр с помощью представительного входного диапазона. Видеть, что код MATLAB для КИХ фильтрует испытательный стенд в командной строке, введите:

edit('mlhdlc_sfir_tb')

Прежде чем вы начнете генерировать код, В пути MATLAB, перейдете к папке, которая перезаписываема, и затем создайте рабочую папку, чтобы сохранить файлы испытательного стенда и проект.

В вашей текущей рабочей папке создайте папку под названием filter_sfir.

mkdir filter_sfir;

Скопируйте учебные файлы, mlhdlc_sfir.m и mlhdlc_sfir_tb.m, к этой папке.

mlhdlc_demo_dir = fullfile(matlabroot, 'toolbox', 'hdlcoder',... 'hdlcoderdemos', 'matlabhdlcoderdemos'); copyfile(fullfile(mlhdlc_demo_dir, 'mlhdlc_sfir.m'), 'filter_sfir'); copyfile(fullfile(mlhdlc_demo_dir, 'mlhdlc_sfir_tb.m'), 'filter_sfir');

Если вы хотите синтезировать сгенерированный HDL-код, прежде чем вы будете использовать HDL Coder, чтобы сгенерировать код, настройте свой инструмент path синтеза. Чтобы создать путь к вашему инструменту синтеза, используйте функцию hdlsetuptoolpath. Например, если вашим инструментом синтеза является Xilinx® Vivado®

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2017.2\bin\vivado.bat');

Чтобы проверять вашу настройку инструмента синтеза Xilinx Vivado, запустите инструмент со следующей командой:

!vivadoЕсли вы используете другой инструмент Synthesis, чтобы видеть, как настроить инструмент path и правильную версию инструмента, чтобы использовать, смотрите Setup Инструмента Path Синтеза.

Чтобы проверить функциональность вашего алгоритма MATLAB, прежде, чем сгенерировать HDL-код, моделируют ваш проект MATLAB.

Сделайте папку filter_sfir вашей рабочей папкой, например:

cd filter_sfirЗапустите испытательный стенд. В командной строке MATLAB, введите:

mlhdlc_sfir_tb

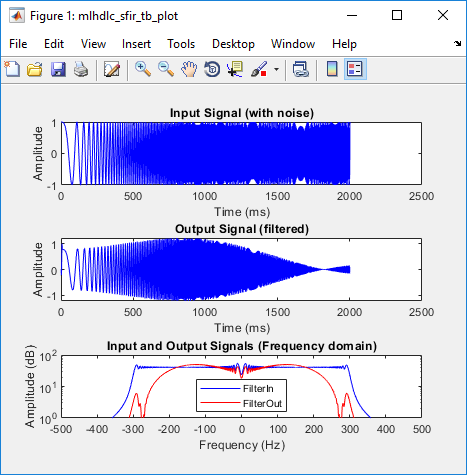

Испытательный стенд запускает и строит входной сигнал и отфильтрованный вывод.

Откройте приложение HDL Coder.

Чтобы открыть Приложение от пользовательского интерфейса, в MATLAB, на вкладке Apps, в разделе Code Generation, выбирают HDL Coder. Можно добавить это Приложение в избранное.

Открыть Приложение из командной строки, введите:

hdlcoder

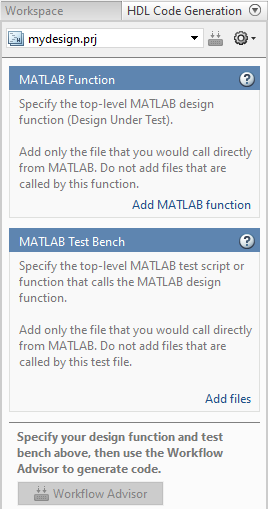

Укажите, что название проекта, например, вводит mydesign.

HDL Coder создает проект, mydesign.prj, в локальной рабочей папке, и открывает проект в правой стороне рабочего пространства MATLAB.

Добавьте файлы испытательного стенда и проект. Для MATLAB Function добавьте файл mlhdlc_sfir.m, и для MATLAB Test Bench, добавьте файл mlhdlc_sfir_tb.m.

Чтобы иметь Приложение автоматически задают типы данных сигналов, когда вы добавляете MATLAB Function, выберите Autodefine types. Выберите файл MATLAB Test Bench mlhdlc_sfir_tb.m, и затем запустите испытательный стенд.

HDL Coder моделирует алгоритм и испытательный стенд, и автоматически задает входные типы. Выберите Use these types.

Используйте HDL Coder Workflow Advisor, чтобы преобразовать ваш алгоритм в фиксированную точку, сгенерировать синтезируемый HDL-код, и затем развернуть код на целевой платформе. Чтобы узнать больше о каждой отдельной задаче в HDL Workflow Advisor, щелкните правой кнопкой по той задаче и выберите What's This?.

![]()

Чтобы открыть Советника по вопросам Рабочего процесса, в проекте, в нижней части панели, нажимают кнопку Workflow Advisor. Вы видите, что задача Define Input Types передала.

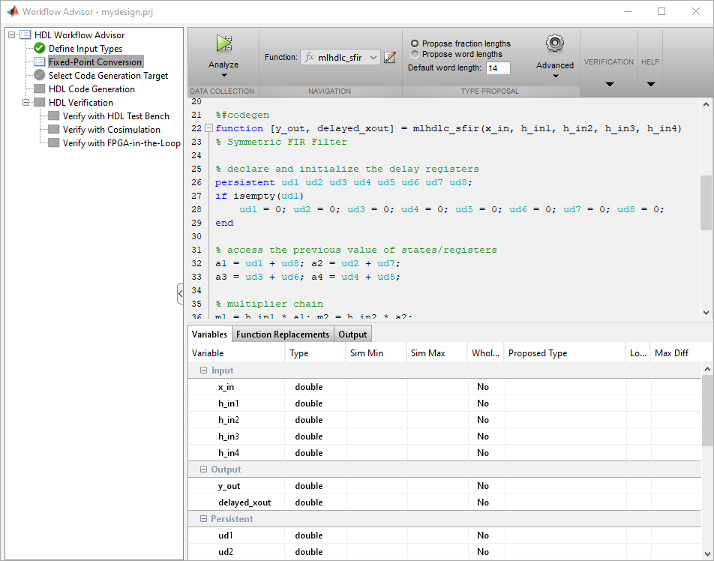

Когда вы запускаете преобразование фиксированной точки, чтобы предложить дробные длины для типов данных с плавающей точкой, HDL Coder использует Default word length. В этом примере Default word length является 14. Советник обеспечивает Safety Margin for Simulation Min/Max по умолчанию 0%. Советник настраивает область значений данных этим запасом прочности. Например, значение 4 указывает, что вы хотите область значений по крайней мере на 4 процента больших.

Выберите задачу Fixed-Point Conversion. Инструмент Fixed-Point Conversion открывается на правой панели.

В левом верхнем выберите Analyze.

После симуляции HDL Coder отображает входной сигнал, отфильтрованный выходной сигнал и график частотного диапазона сигналов ввода и вывода. Если вы перешли к инструменту Fixed-Point Conversion в советнике по вопросам Рабочего процесса Виндоу, вы видите, что каждый вход, выведите, и персистентная переменная имеет Sim Min, Sim Max и Proposed Type в таблице.

Этот пример использует области значений симуляции, чтобы вывести фиксированные точки. Можно использовать Compute Derived Ranges, чтобы получить область значений с помощью статического анализа области значений. Чтобы узнать больше, смотрите Автоматизированное Преобразование Фиксированной точки.

Наверху, в разделе Verification, нажмите Validate Types.

HDL Coder подтверждает сборку с предложенными фиксированными точками и генерирует проект фиксированной точки.

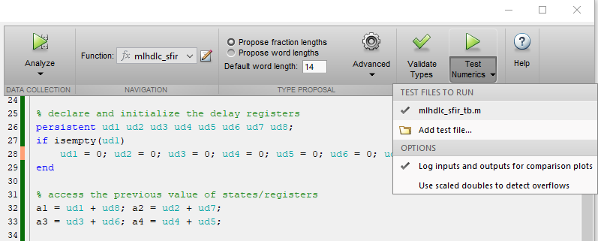

Наверху, в разделе Verification, кликните по стрелке вниз для Test Numerics и выберите Log inputs and outputs for comparison plots. Кликните по верхней части кнопки Test Numerics.

HDL Coder моделирует проект фиксированной точки с исходным испытательным стендом, сравнивает вывод с исходной проектной мощностью с плавающей точкой, и затем отображает различие как сигнал ошибки.

В нижней части вы видите вкладку Verification Output. Вкладка отображает ссылку на отчет mlhdlc_sfir_fixed_report.html. Чтобы исследовать фиксированную точку для функции mlhdlc_sfir, откройте отчет.

Чтобы видеть фиксированную точку в редакторе MATLAB, в папке filter_sfir, вы видите папку codegen. Когда вы перемещаетесь по этой папке, вы видите файл mlhdlc_sfir_fixpt. Откройте этот файл.

Если вы хотите синтезировать свой проект на целевой платформе FPGA, выберите задачу Select Code Generation Target. Оставьте Workflow Generic ASIC/FPGA и задайте Synthesis tool. Если вы не видите инструмент синтеза, выберите Refresh list.

Прежде, чем сгенерировать код, настроить опции генерации кода, в задаче HDL Code Generation, используют Target, Coding Style, Clocks and Ports, Optimizations, Advanced и вкладки Script Options

Чтобы сгенерировать HDL-код, в задаче HDL Code Generation, выбирают Run.

Окно сообщения имеет ссылки на сгенерированный HDL-код и отчет ресурса. Щелкните по ссылкам, чтобы просмотреть отчет ресурса и код.

На левой панели HDL Workflow Advisor выберите HDL Verification> задача Verify with HDL Test Bench.

Включите Generate HDL test bench и отключите Skip this step. Включите Simulate generated HDL test bench и выберите инструмент симуляции. Нажмите Run.

Задача генерирует испытательный стенд HDL, затем моделирует проект фиксированной точки с помощью выбранного инструмента симуляции и генерирует отчет компиляции и отчет симуляции.

Выберите Synthesis and Analysis и отключите Skip this step. Запустите задачу Create Project.

Эта задача создает проект синтеза для HDL-кода. HDL Coder использует этот проект в следующей задаче синтезировать проект.

Выберите и запустите задачу Run Synthesis. Эта задача:

Запускает инструмент синтеза в фоновом режиме.

Открывает проект синтеза, созданный в предыдущей задаче, компилирует HDL-код, синтезирует проект и испускает списки соединений и связанные файлы.

Генерирует отчет синтеза.

Выберите и запустите задачу Run Implementation. Эта задача:

Запускает инструмент синтеза в фоновом режиме.

Запускает процесс Места и Маршрута, который берет описание схемы, произведенное предыдущим процессом отображения, и испускает описание схемы, подходящее для программирования FPGA.

Испускает пред - и постнаправляющий синхронизацию информации для использования в анализе критического пути и обратной корректировке проекта вашей исходной модели.