В HDL Workflow Advisor можно выбрать Processor/FPGA synchronization mode для процессора и FPGA когда вы:

Сгенерируйте пользовательское ядро IP, чтобы использовать в проекте интегрирования встраиваемой системы.

Используйте рабочий процесс Simulink Real-Time FPGA I/O.

Следующие режимы синхронизации доступны:

Free running (значение по умолчанию)

Coprocessing – blocking

Coprocessing – nonblocking with delay (доступный только для рабочего процесса Simulink Real-Time FPGA I/O)

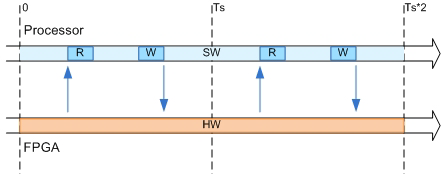

В режиме свободного доступа, процессоре и FPGA каждое несинхронизируемое выполнение, постоянно, и параллельно.

Выберите Free running как Processor/FPGA synchronization mode, когда вы не захотите, чтобы ваш процессор и FPGA автоматически синхронизировались.

Следующая схема показывает, как процессор и FPGA могут связаться в режиме свободного доступа. Заштрихованные области указывают, что процессор и FPGA запускаются постоянно.

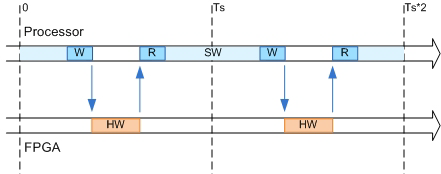

В блокирующемся режиме сопроцессора HDL Coder™ автоматически генерирует логику синхронизации для FPGA так, чтобы процессор и FPGA, запущенный в тандеме.

Выберите Coprocessing – blocking как Processor/FPGA synchronization mode, когда время выполнения FPGA коротко относительно шага расчета процессора, и вы хотите, чтобы FPGA завершился, прежде чем процессор продолжится.

Следующая схема показывает как процессор и FPGA, запущенный в блокировании режима совместной обработки.

Заштрихованные области указывают, когда процессор и FPGA запускаются. Во время каждого шага расчета процессор пишет в FPGA, затем останавливается и ожидает индикации, которую FPGA закончил обрабатывать прежде, чем продолжить запускаться. Каждый раз выполнения FPGA, это выполняет логику, сгенерированную для одного шага расчета подсистемы DUT.

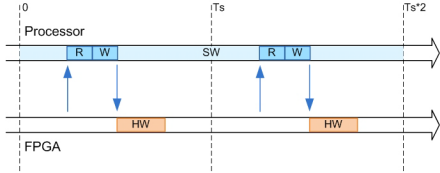

В задержанном режиме сопроцессора неблокирования HDL Coder автоматически генерирует логику синхронизации для FPGA так, чтобы процессор и FPGA, запущенный в тандеме. Этот режим только доступен модулям Speedgoat IO, которые используют Xilinx® ISE с рабочим процессом Simulink Real-Time FPGA I/O.

Выберите Coprocessing – nonblocking with delay как Processor/FPGA synchronization mode, когда время вычислений FPGA долго относительно шага расчета процессора, или вы не хотите, чтобы процессор ожидал FPGA, чтобы закончиться, прежде чем процессор продолжит запускаться.

Следующая схема показывает как процессор и FPGA, запущенный в задержанном режиме сопроцессора неблокирования.

Заштрихованные области указывают, когда процессор и FPGA запускаются. Во время каждого шага расчета процессор считывает данные о FPGA из предыдущего шага расчета, затем пишет в FPGA и продолжает запускаться, не ожидая FPGA, чтобы закончиться. Каждый раз выполнения FPGA, это выполняет логику, сгенерированную для одного шага расчета подсистемы DUT.