Если вы разрабатываете свой алгоритм при помощи переключенных линейных блоков Simscape™, можно запустить HDL Workflow Advisor Simscape, чтобы сгенерировать модель реализации HDL. Когда вы открываете модель реализации HDL, вы видите алгоритм HDL, который моделирует представление пространства состояний при помощи блоков Simulink®, которые совместимы для генерации HDL-кода. Чтобы узнать больше о HDL Workflow Advisor Simscape, смотрите Задачи HDL Workflow Advisor Simscape.

Когда вы генерируете HDL-код и развертываете модель объекта управления на FPGA, можно хотеть улучшить частоту дискретизации. Частота дискретизации зависит от этих параметров:

Частота часов FPGA

Сверхдискретизация фактора

Количество итераций решателя

![]()

Чтобы улучшить уровень выборки, вы хотите максимизировать частоту часов FPGA и минимизировать фактор сверхдискретизации и количество итераций решателя. Когда вы улучшаете уровень выборки, убедитесь, что обновленная частота дискретизации эквивалентна фиксированному шагу расчета, который вы задаете для своей исходной модели Simscape при помощи Блока Configuration Решателя. Чтобы узнать больше, как этот блок используется в вашей модели прежде, чем запустить HDL Workflow Advisor Simscape, смотрите, Генерируют HDL-код из Моделей Simscape.

Предыдущий раздел использует модель конвертера повышения в качестве примера, чтобы проиллюстрировать, как можно изменить фактор сверхдискретизации и количество итераций решателя, чтобы улучшить уровень выборки.

Этот пример использует модель конвертера повышения, чтобы проиллюстрировать изменение в шаге расчета в сгенерированной модели реализации HDL и факторе сверхдискретизации, который сохранен на модели.

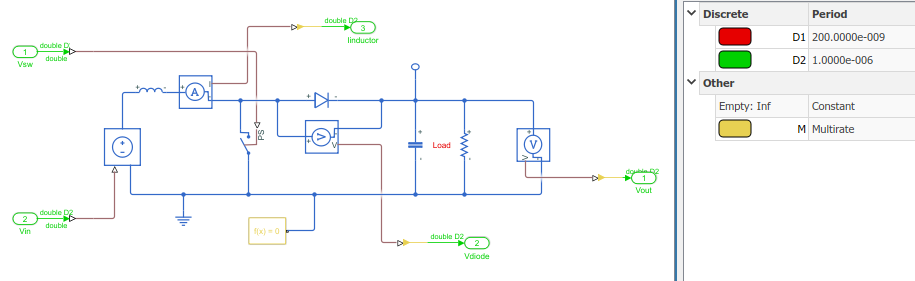

Откройте модель конвертера повышения. Чтобы изучить, как конвертер повышения реализован, откройте Подсистему Simscape_system. Открыть модель конвертера повышения, в Командном окне MATLAB®, введите:

open_system('sschdlexBoostConverterExample') open_system('sschdlexBoostConverterExample/Simscape_system')

Вы видите, что модель запускает в шаге расчета 1e-6. Шаг расчета 200e-9 соответствует шагу расчета источников, которые управляют алгоритмом Simscape.

Сохраните локальную копию этой модели и переименуйте ее как BoostConverter_HDL, чтобы запустить Simscape к рабочему процессу HDL. Откройте HDL Workflow Advisor Simscape для своей модели:

sschdladvisor('BoostConverter_HDL')Запустите рабочий процесс к задаче Generate implementation model.

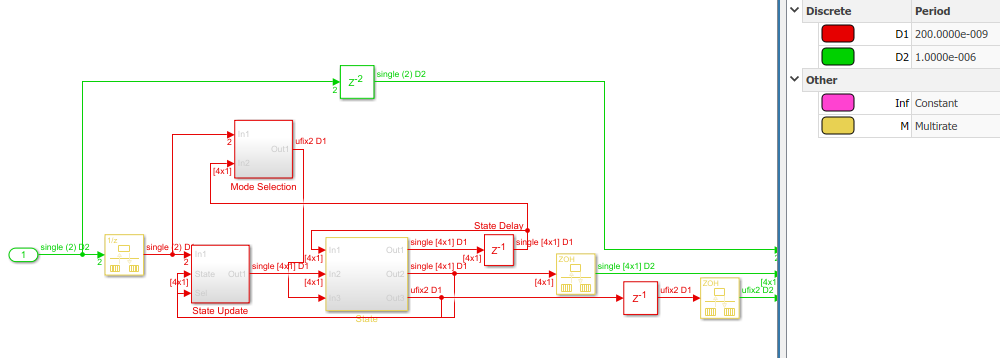

После выполнения этой задачи вы видите ссылку на сгенерированную модель реализации HDL. Щелкните по ссылке, чтобы открыть модель реализации HDL. Если вы моделируете модель реализации HDL и перемещаетесь по модели к Подсистеме HDL Algorithm, вы видите, что модель использует типы данных single и содержит Переход Уровня, и Нулевой Порядок Содержат блоки, которые запускают модель в шаге расчета 200e-9, который является временами 5 быстрее, чем исходная модель Simscape.

Запустите эту команду, чтобы видеть установки параметров HDL, которые сохранены на модели:

hdlsaveparams('gmStateSpaceHDL_BoostConverter_HDL')

%% Set Model 'gmStateSpaceHDL_BoostConverter_HDL' HDL parameters

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', ...

'FloatingPointTargetConfiguration', hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint' ...

, 'LatencyStrategy', 'MIN') ...

);

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'HDLSubsystem', 'gmStateSpaceHDL_BoostConverter_HDL');

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'MaskParameterAsGeneric', 'on');

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL', 'Oversampling', 60);

% Set SubSystem HDL parameters

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL/HDL Subsystem', 'FlattenHierarchy', 'on');

% Set SubSystem HDL parameters

hdlset_param('gmStateSpaceHDL_BoostConverter_HDL/HDL Subsystem/HDL Algorithm/State Update/Multiply State', ...

'SharingFactor', 1);

Параметры HDL, которые сохранены, указывают, что модель имеет нативный режим с плавающей точкой, включил и использует Oversampling factor 60 и установили Latency Strategy на MIN. Эта комбинация по умолчанию параметров HDL, которые сохранены на модели, предлагает оптимальный компромисс между сверхдискретизацией фактора и целевой частотой часов FPGA и улучшает частоту дискретизации. Если вы хотите далее улучшить частоту дискретизации, можно сократить количество итераций и фактора сверхдискретизации, как проиллюстрировано ниже.

HDL Workflow Advisor Simscape использует итерационный метод, который определяет количество итераций, требуемых вычислить режим в каждом временном шаге. Если N является Number of solver iterations, выполнения модели реализации HDL на уровне частоты дискретизации, которая является временами N быстрее, чем исходный алгоритм Simscape. По умолчанию, для коммутируемых линейных моделей, Number of solver iterations является 5. Сгенерированная модель реализации HDL запускает времена 5 быстрее, чем исходная модель Simscape.

Чтобы улучшить уровень выборки, вы хотите сократить количество итераций решателя. Количество итераций решателя зависит от различных факторов, таких как сложность вашего проекта, количество режимов в проекте, который рабочий процесс должен вычислить и так далее. В задаче Generate implementation model HDL Workflow Advisor Simscape запустите путем сокращения Number of solver iterations до значения, такого как 3, выберите Generate validation logic for the implementation model, и затем сгенерируйте модель реализации HDL. Моделируйте модель реализации HDL и откройте Диагностическое Средство просмотра, чтобы убедиться, что модель не выводит предупреждений или утверждений.

Если вы видите предупреждения или утверждения, это указывает на несоответствие симуляции, потому что количество итераций решателя, которые вы задали, не соответствует, чтобы вычислить необходимое количество режимов в проекте пространства состояний. Чтобы разрешить предупреждения, можно хотеть увеличить Validation logic tolerance до значения, такого как 1e-4 и затем моделировать модель реализации HDL. Если вы все еще видите предупреждения, увеличиваете Number of solver iterations.

Рекомендуется, чтобы вы не изменяли Floating-point precision на double. Операции с двойной точностью имеют большие задержки и требуют, чтобы большой Oversampling factor выделил достаточные задержки операций с плавающей точкой, который уменьшает частоту дискретизации.

Чтобы узнать больше, как можно разрешить несоответствие симуляции, смотрите, Подтверждают Модель Реализации HDL к Алгоритму Simscape.

Фактор Сверхдискретизации задает фактор, которым тактовая частота FPGA является кратной базовой частоте дискретизации модели реализации HDL. Модель реализации HDL содержит обратную связь и выполняет умножение больших матриц, которые имеют типы данных с плавающей точкой в обратной связи. Чтобы разместить большую задержку, введенную этими операциями с плавающей точкой в обратной связи, генератор кода использует большое значение сверхдискретизации фактора в сочетании с оптимизацией конвейеризации тактовой частоты на модели. Для получения дополнительной информации см. Стратегию 1: Глобальная Сверхдискретизация.

В диалоговом окне Configuration Parameters, на HDL Code Generation> панель Floating Point, можно задать Latency Strategy Min, Max или Zero на модели. Фактор сверхдискретизации и стратегия задержки оператора с плавающей точкой должны отличаться по соединению. По умолчанию фактор сверхдискретизации 60 и минимальной стратегии задержки дает оптимальную частоту дискретизации. В большинстве случаев, когда вы используете минимальную стратегию задержки, можно запустить с фактора Сверхдискретизации 60, сгенерировать HDL-код, и затем далее уменьшать фактор сверхдискретизации, пока генератор кода не не может выделить задержки операций с плавающей точкой.

Если вы задаете задержку Max, операции с плавающей точкой вводят максимальное количество задержек. Чтобы убедиться, что эти задержки могут быть выделены, увеличьте Oversampling factor. Можно хотеть увеличить Oversampling factor до значения, такого как 100 в зависимости от сложности проекта HDL. Максимальная стратегия задержки обеспечивает максимальную частоту часов FPGA, которой можно достигнуть. Если увеличение частоты часов FPGA перевешивает увеличение сверхдискретизации фактора, можно использовать максимальную стратегию задержки вместо этого.

Для модели конвертера повышения, настроек по умолчанию набора Number of solver iterations к 5, набор Oversampling factor к 60 и набор Latency Strategy к Min обеспечивают оптимальную частоту дискретизации.