Собственный компонент HDL Coder™ технология с плавающей точкой может сгенерировать независимый от цели HDL-код из вашего проекта с плавающей точкой. Можно синтезировать проект с плавающей точкой на любом типичном FPGA или ASIC. Проекты с плавающей точкой имеют лучшую точность, более высокий динамический диапазон и более короткий цикл разработки, чем проекты фиксированной точки. Если ваш проект имеет комплексную математику и тригонометрические операции, используйте нативную технологию с плавающей точкой.

При представлении бесконечно вещественных чисел с конечным числом битов могут быть погрешности округления с правильной областью значений округления значений, которые задает стандарт IEEE 754. Чтобы измерить погрешности округления, можно задать проверку допуска с плавающей точкой на основе relative error или ulp error. Для получения дополнительной информации об этих погрешностях округления, смотрите Факторы ULP и Относительная точность.

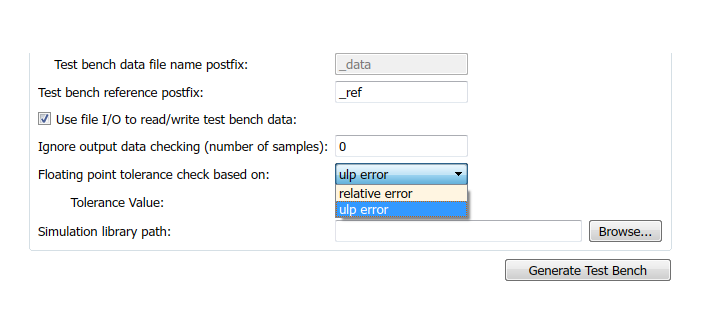

Прежде, чем сгенерировать испытательный стенд, задайте проверку допуска с плавающей точкой на проверку сгенерированного кода.

Чтобы задать допуск регистрируются в диалоговом окне Configuration Parameters:

В HDL Code Generation> панель Testbench, для Floating point tolerance check based on, задают relative error или ulp error.

Введите Tolerance Value и нажмите Apply. Если вы выбираете relative error, значением по умолчанию является значение допуска 1e-07. Если вы выбираете ulp error, значение допуска по умолчанию является нулем. Чтобы узнать больше, смотрите Числовые Факторы с Собственным компонентом, С плавающей точкой.

Чтобы задать стратегию допуска в командной строке, используйте:

Задайте установку проверки допуска с плавающей точкой при помощи FPToleranceStrategy.

hdlset_param('sfir_single', 'FPToleranceStrategy', 'Relative'); % check for floating-point tolerance based on the relative error

hdlset_param('sfir_single', 'FPToleranceStrategy', 'ULP'); % check for floating-point tolerance based on the ULP errorНа основе установки FPToleranceStrategy введите значение допуска при помощи FPToleranceValue.

hdlset_param('FP_test_16a', 'FPToleranceValue', 1e-06); % if using relative error, enter a custom tolerance value

hdlset_param('FP_test_16a', 'FPToleranceValue', 1); % if using ULP error, enter tolerance value greater than or equal to 1

Сгенерировать испытательный стенд HDL для проверки сгенерированного кода:

В диалоговом окне Configuration Parameters, на HDL Code Generation> панель Test Bench, в разделе Test Bench Generation Output, выбирают HDL test bench.

В разделе Configuration убедитесь, что Use file I/O to read/write test bench data включен. Чтобы сгенерировать испытательный стенд, который использует константы вместо файлового ввода-вывода, очистите Use file I/O to read/write test bench data.

Нажмите Apply, и затем нажмите Generate Test Bench.

Чтобы узнать больше, как генерация испытательного стенда HDL работает, смотрите Генерацию Испытательного стенда.

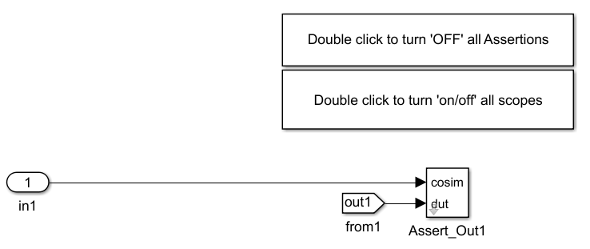

Сгенерировать cosimulation модель для проверки сгенерированного кода:

В диалоговом окне Configuration Parameters, на HDL Code Generation> панель Test Bench, для Cosimulation model for use with, выбирают cosimulation инструмент.

Нажмите Apply, и затем нажмите Generate Test Bench.

После генерации испытательного стенда сохраните cosimulation модель. В модели дважды кликните подсистему Compare.

Если вы дважды кликаете блок Assert_Out1, параметры блоков показывают ToleranceValue, что вы задаете.

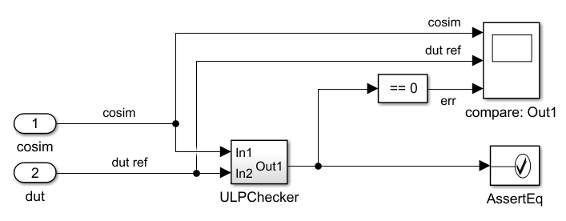

Чтобы посмотреть в блоке Assert_Out1, кликните по маске. Если вы задаете проверку допуска с плавающей точкой на основе ulp error, модель показывает блок ULPChecker.

ULPChecker имеет блок MATLAB function, который показывает, как HDL Coder составляет ошибку ULP при проверке на числовую точность.

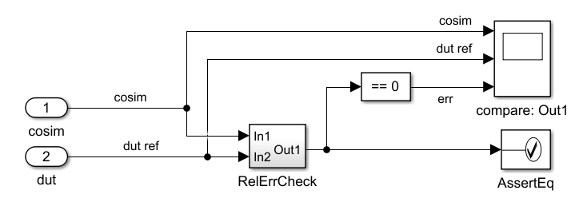

Если вы задаете проверку допуска с плавающей точкой на основе relative error, модель показывает блок RelErrCheck.

RelerrCheck имеет блок MATLAB function, который показывает, как HDL Coder составляет относительную погрешность при проверке на числовую точность.

В Редакторе Simulink® для модели запустите симуляцию. В конце cosimulation проверяйте осциллограф compare: Out1.

Осциллограф сравнивает различие между сигналом результата от блока cosimulation и ссылочным сигналом от DUT.

См. также Генерируют Модель Cosimulation.

При проверке сгенерированного кода построения, которые используют стандарты IEEE до VHDL-2008, не поддержаны с собственным компонентом, с плавающей точкой.