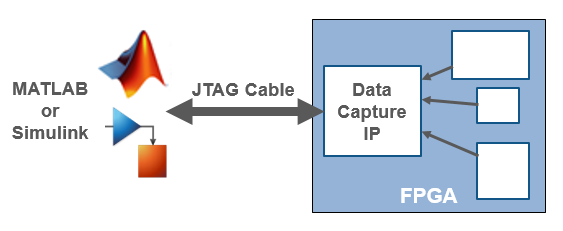

Используйте функцию сбора данных FPGA, чтобы наблюдать сигналы из вашего проекта, в то время как проект работает на FPGA. Эта функция получает окно данных сигнала от FPGA и возвращает данные в MATLAB® или Simulink®.

Чтобы использовать эту функцию, необходимо загрузить пакет аппаратной поддержки для платы FPGA. Смотрите Пакет поддержки плат FPGA Загрузки.

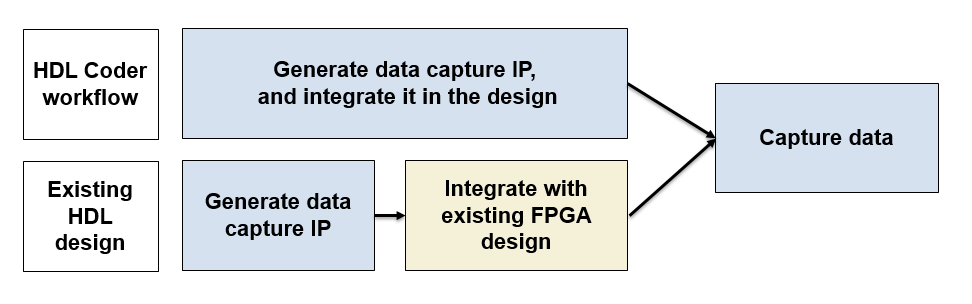

Можно принять решение между двумя рабочими процессами собрать данные от платы FPGA и возвратить его в MATLAB или Simulink.

Если вы генерируете IP HDL с HDL Coder™, используйте HDL Workflow Advisor, чтобы сгенерировать IP сбора данных и интегрировать его в ваш проект FPGA.

Если у вас есть существующий проект HDL, используйте инструменты HDL Verifier™, чтобы сгенерировать IP сбора данных. Затем вручную интегрируйте сгенерированный IP в свой проект FPGA.

Чтобы получить сигналы из вашего проекта, HDL Verifier генерирует ядро IP, которое связывается с MATLAB. Используйте рабочий процесс HDL Coder, чтобы автоматически интегрировать ядро IP сбора данных в вашем проекте. В противном случае вручную интегрируйте это ядро IP в свой проект HDL и разверните его на FPGA наряду с остальной частью вашего проекта. Затем используйте один из этих методов, чтобы собрать данные.

Для того, чтобы собрать данные к MATLAB – HDL Verifier генерирует индивидуально настраиваемое приложение, которое возвращает полученные данные сигнала. Также можно использовать сгенерированную Систему object™, чтобы собрать данные программно.

Для того, чтобы собрать данные к Simulink – HDL Verifier генерирует блок, который имеет выходные порты, соответствующие сигналам, которые вы получили.

В обоих случаях можно задать типы данных для собранных данных, количества окон, чтобы получить, и инициировать условия, которые управляют, когда данные выбираются.

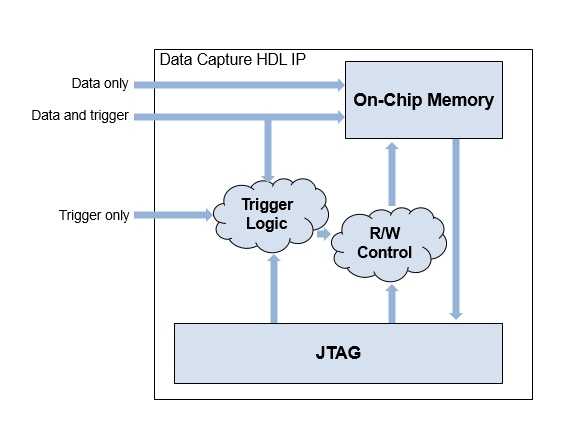

Когда проект работает на FPGA, сначала сгенерированное ядро IP ожидает триггерного условия, которое вы задаете. Задайте триггерное условие путем определения значений, соответствующих на одном или нескольких сигналах. Когда триггер обнаруживается, логика получает обозначенные сигналы к буферу и возвращает данные по интерфейсу JTAG к хост-машине. Можно затем анализировать и отобразить эти сигналы в модели рабочее пространство MATLAB или Simulink.

При использовании HDL Workflow Advisor, чтобы сгенерировать ваш проект HDL, сначала отметьте желаемые сигналы как Тестовые точки (Simulink) в Simulink. Сконфигурируйте свой проект с помощью HDL Workflow Advisor для:

Включите генерацию тестовой точки.

Соедините сигналы тестовой точки с интерфейсом FPGA Data Capture IP.

Настройте buffer size для сбора данных.

Затем выполните остающиеся шаги, чтобы сгенерировать HDL для вашего проекта и программировать FPGA. Ядро IP сбора данных интегрировано в сгенерированный проект FPGA. Можно теперь Собрать Данные от FPGA.

Для примера использования сбора данных с HDL Workflow Advisor смотрите, что Ядро IP Отладки Использует Сбор данных FPGA (HDL Coder).

Прежде, чем собрать данные о FPGA, необходимо сначала задать который сигналы получить и сколько выборок данных, чтобы возвратиться. При использовании существующего проекта HDL используйте приложение FPGA Data Capture Component Generator, чтобы сконфигурировать настройки и сгенерировать ядро IP сбора данных. Ядро IP содержит:

Порт для каждого сигнала вы хотите получить или использовать в качестве части триггерного условия

Память, чтобы получить количество выборок вы запросили для каждого сигнала

Логика интерфейса JTAG, чтобы связаться с MATLAB

Инициируйте логику, которая может быть сконфигурирована во время выполнения

Приложение также генерирует индивидуально настраиваемое приложение FPGA Data Capture, Системный объект и модель, которые связываются с FPGA.

Для MATLAB, чтобы связаться с FPGA, необходимо интегрировать сгенерированное ядро IP HDL в проект FPGA. Если вы использовали HDL Workflow Advisor, чтобы сгенерировать ваш IP сбора данных, этот шаг автоматизирован. В противном случае следуйте инструкциям в отчете генерации. Добавьте сгенерированные файлы HDL от папки hdlsrc в ваш проект FPGA. Затем инстанцируйте ядра IP HDL, datacapture, в вашем HDL-коде, и соедините его с сигналами, которые вы запросили для получения и триггеров. Скомпилируйте проект и программируйте FPGA с новым изображением. Можно теперь Собрать Данные от FPGA.

Ядро IP сбора данных FPGA связывается по кабелю JTAG между вашей платой FPGA и хостом - компьютером. Убедитесь, что кабель соединяется. Прежде, чем собрать данные, можно установить типы данных для собранных данных и установить триггерные условия, которые задают, когда собрать данные. Чтобы сконфигурировать эти опции и собрать данные, вы можете:

Откройте приложение FPGA Data Capture. Установите триггер и параметры типа данных, и затем соберите данные в рабочее пространство MATLAB.

Используйте сгенерированный Системный объект, выведенный от hdlverifier.FPGADataReader. Установите типы данных и инициируйте условие с помощью методов и свойств Системного объекта, и затем вызовите объект собрать данные.

В Simulink, открытом сгенерированная модель, и, конфигурируют параметры блока FPGA Data Reader. Затем запустите модель, чтобы собрать данные.

После того, как вы соберете данные в модель рабочее пространство MATLAB или Simulink, можно анализировать, проверить и отобразить данные.