Декодируйте сверточно закодированное демонстрационное использование алгоритм Viterbi

LTE HDL Toolbox / Выявление ошибок и Исправление

![]()

Блок Convolutional Decoder реализует всеобъемлющий алгоритм Viterbi (WAVA), чтобы декодировать выборки, закодированные с кусающими хвост полиномами, заданными TS 36.212 [1] стандарта LTE. Сверточный код имеет продолжительность ограничения 7 и является хвостом, резким с кодированием уровня 1/3 и восьмеричные полиномы G0=133, G1=171 и G2=165. Блок обеспечивает аппаратную оптимизированную архитектуру и интерфейс.

Этот блок использует демонстрационный интерфейс потоковой передачи с шиной для связанных управляющих сигналов. Этот интерфейс позволяет блоку действовать независимо от формата кадра и соединиться легко с другими блоками LTE HDL Toolbox™. Блок принимает и возвращает значение, представляющее одну выборку и шину, содержащую три управляющих сигнала. Эти сигналы указывают на валидность каждой выборки и контуры кадра. Чтобы преобразовать матрицу в демонстрационный поток и эти управляющие сигналы, используйте блок Frame To Samples или функцию ltehdlFramesToSamples. Для полного описания интерфейса смотрите Демонстрационный Интерфейс Потоковой передачи.

Блок принимает входные выборки, представляющие мягкие или трудные решения. Каждая выборка является вектором 3 на 1, где эти три значения представляют биты, закодированные этими тремя полиномами, [G0 G1 G2].

Декодирование сообщения выборок M требует 2*M+140 циклы, принимая непрерывный допустимый вход. Поэтому необходимо уехать, по крайней мере, который структурируют много неактивных циклов между входом. Также можно использовать выходной сигнал ctrl.end, чтобы определить, когда блок готов к новому входу.

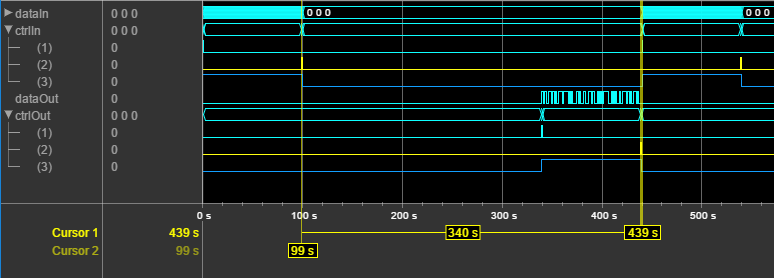

Эта форма волны показывает входной сигнал 100 выборок с 340 неактивными циклами между кадрами. Входные данные являются вектором трех закодированных битов. Ввод и вывод шины ctrl расширен, чтобы показать управляющие сигналы. start и end показывают контуры кадра, и valid квалифицирует выборки данных.

[1] 3GPP TS 36.212. "Мультиплексирование и кодирование канала". Проект Партнерства третьего поколения; Сеть радиодоступа Technical Specification Group; Развитый Универсальный Наземный Радио-доступ (к E-UTRA). URL: http://www.3gpp.org.