Закодируйте бинарные выборки с помощью турбо алгоритма

LTE HDL Toolbox / Выявление ошибок и Исправление

![]()

Блок Turbo Encoder реализует турбо энкодер, описанный TS 36.212 [1] стандарта LTE с помощью интерфейса и архитектуры, оптимизированной для аппаратного развертывания и генерации HDL-кода. Энкодер является параллелью конкатенировала сверточный код (PCCC) с двумя составляющими энкодерами с 8 состояниями и внутренним interleaver. Первый энкодер работает с потоком входных данных, и второй энкодер работает с чередованной версией входных данных. Блок отключает каждый энкодер вывод с независимыми битами хвоста. Уровень кодирования является 1/3. Закодированные выходные биты для каждого входного бита возвращены как вектор 3 на 1, [S P1 P2]. В этом векторе S является систематическим битом, и P1 и P2 являются битами четности от этих двух энкодеров.

Этот блок использует демонстрационный интерфейс потоковой передачи с шиной для связанных управляющих сигналов. Этот интерфейс позволяет блоку действовать независимо от формата кадра и соединиться легко с другими блоками LTE HDL Toolbox™. Блок принимает и возвращает значение, представляющее одну выборку и шину, содержащую три управляющих сигнала. Эти сигналы указывают на валидность каждой выборки и контуры кадра. Чтобы преобразовать матрицу в демонстрационный поток и эти управляющие сигналы, используйте блок Frame To Samples или функцию ltehdlFramesToSamples. Для полного описания интерфейса смотрите Демонстрационный Интерфейс Потоковой передачи.

Блок может принять новые входные данные после того, как предыдущий кадр будет завершен. Примените входные кадры, по крайней мере, с BlockSize + 17 неактивных циклов между ними. Дополнительные 17 циклов задержки должны конвейерно обработать задержки алгоритма и не меняются в зависимости от размера блока. Или, можно использовать выходной сигнал ctrl.end, чтобы определить, когда блок готов к новому входу.

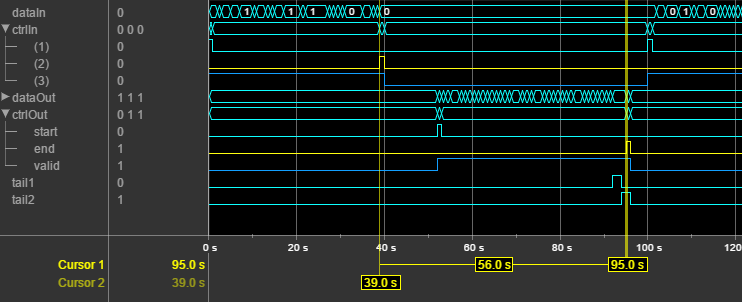

Эта форма волны показывает входной кадр 40 выборок с 57 неактивными циклами между кадрами. Ввод и вывод шины ctrl расширен, чтобы показать управляющие сигналы. start и end показывают контуры кадра, и valid квалифицирует выборки данных. Дополнительный tail1 и сигналы tail2 указывают на циклы, когда биты хвоста от каждого энкодера допустимы.

[1] 3GPP TS 36.212. "Мультиплексирование и кодирование канала". Проект Партнерства третьего поколения; Сеть радиодоступа Technical Specification Group; Развитый Универсальный Наземный Радио-доступ (к E-UTRA). URL: http://www.3gpp.org.