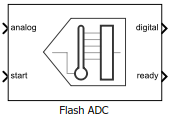

ADC N-bit с архитектурой флэш-памяти

Mixed-Signal Blockset / ADC / Архитектура

Битный ADC флэш-памяти N включает резистивную лестничную структуру, которая содержит 2N резисторы и 2N-1 компараторы.

Ссылочное напряжение каждого компаратора является 1 младшим значащим битом (LSB) выше, чем тот ниже его в лестничной структуре. В результате все компараторы ниже определенного момента будут иметь входное напряжение больше, чем ссылочное напряжение и логический 1 вывод. Все компараторы выше той точки будут иметь входное напряжение меньшим, чем ссылочное напряжение и логический 0 вывод. Вывод 2N-1 компараторов передается через кодер приоритета, чтобы произвести цифровой выход. Эта схема кодирования называется кодированием термометра.

Поскольку аналоговый вход применяется ко всем компараторам целиком, архитектура ADC флэш-памяти очень быстра. Но ADC имеет с низким разрешением и мощные требования из-за большого количества резисторов, требуемых реализовывать архитектуру.

Измерение AC ADC | Измерение DC ADC | Испытательный стенд ADC | Апертурное измерение дрожания | ADC SAR