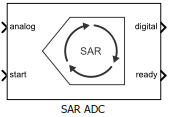

N-bit основанный на регистре последовательного приближения (SAR) ADC

Mixed-Signal Blockset / ADC / Архитектура

Основанный на Регистре последовательного приближения (SAR) ADC состоит из схемы выборки и хранения (SHA), компаратор, внутренний цифро-аналоговый преобразователь (DAC) и регистр последовательного приближения.

Когда ADC получает команду start, SHA помещается в режим хранения. Старший значащий бит (MSB) SAR установлен в логический 1, и все другие биты установлены в логический 0.

Вывод SAR возвращен к DAC, вывод которого по сравнению с входящим входным сигналом. Если DAC, вывод больше, чем аналоговый вход, MSB, сбрасывается, в противном случае это оставляют установленным. Следующий MSB теперь установлен в 1, и процесс повторяется до каждого бита сравнен SAR. Окончательное значение SAR в конце этого процесса соответствует значению аналогового входа. Конец процесса преобразования обозначается сигналом ready.

Измерение AC ADC | Измерение DC ADC | Испытательный стенд ADC | Апертурное измерение дрожания | ADC Flash