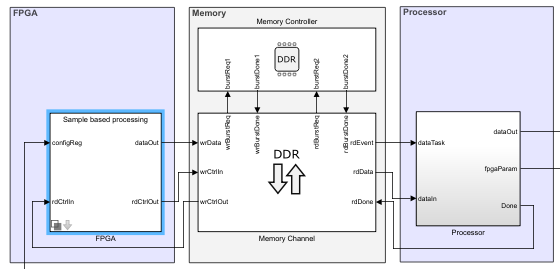

Канал памяти моделирует передачу данных с FPGA на процессор с помощью совместно использованной внешней памяти. Канал регистра моделирует управление логики FPGA от процессора. Можно и сконфигурировать логику FPGA и считать состояние логики FPGA от процессора. Следующие разделы показывают, как соединиться, создают эти связи канала.

Откройте модель soc_hwsw_top.slx.

Добавьте блок Memory Channel и блок Memory Controller к области Memory. Вместе, эти блоки моделируют связь памяти через DDR между процессором и сторонами FPGA вашего приложения.

Откройте диалоговую маску блока Memory Controller. Установите Number of masters на 2. Во вкладке Advanced Контроллер памяти автоматически наследовал параметры от Hardware board, заданного в настройках модели.

Соедините пару пакетных портов Контроллера памяти, burstReq и burstDone, к чтению и пакетным портам запроса записи блока Memory Channel.

В модели откройте диалоговую маску блока Memory Channel. Установите Channel type на AXI4-Stream to Software via DMA. Установите Buffersize (bytes) на FrameSize*4 и Number of buffers к 6. Нажмите OK.

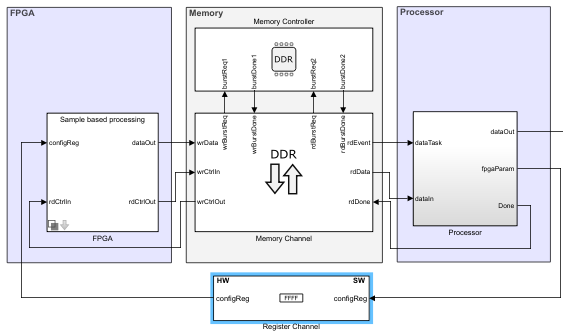

Добавьте блок Register Channel в модель и соедините блок с Processor и подсистемами FPGA как показано в следующем изображении.

Откройте диалоговую маску блока Register Channel. Добавьте два новых регистра с этими свойствами.

| Регистр | Направление | Тип данных | Размерность |

|---|---|---|---|

| configReg | Запись | uint8 | 1 |

Установите Register write sample time на FPGASSTime. Нажмите OK. Этот шаг расчета установлен в файле soc_hwsw_init.m.

Контроллер памяти | Канал памяти | Укажите канал