Кодер поддерживает генерацию блоков Simulink® HDL Cosimulation. Можно использовать сгенерированный HDL блоки Cosimulation для cosimulate создание фильтра с помощью Simulink с симулятором HDL. Чтобы использовать эту функцию, у вас должна быть лицензия HDL Verifier™.

Сгенерированный HDL блоки Cosimulation сконфигурирован, чтобы соответствовать порту и интерфейсу типа данных фильтра, выбранного для генерации кода. Путем соединения блока HDL Cosimulation с моделью Simulink вместо фильтра вы можете cosimulate ваш проект с желаемым симулятором HDL.

Сгенерировать HDL блоки Cosimulation:

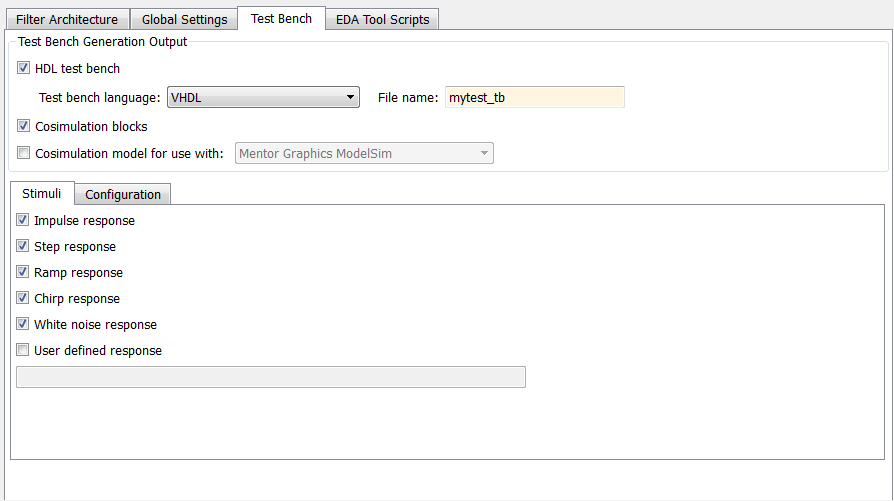

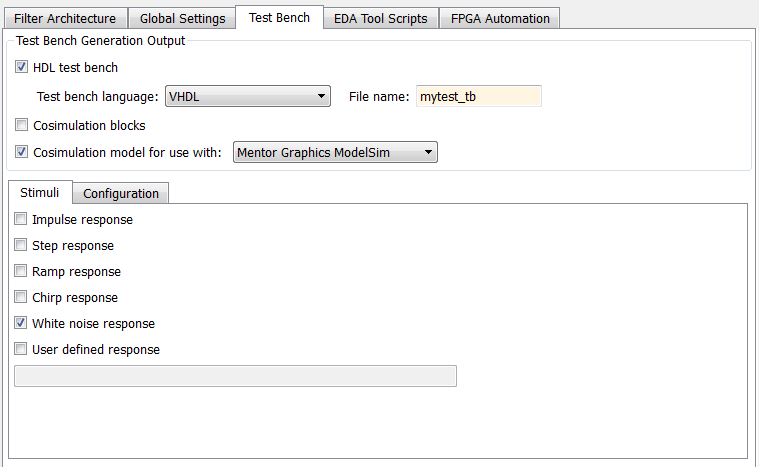

Выберите панель Test Bench в диалоговом окне Generate HDL.

Выберите опцию Cosimulation blocks.

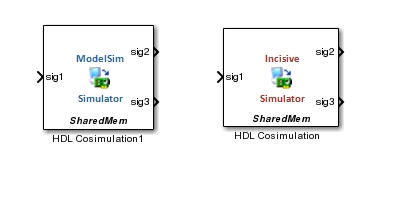

Когда эта опция выбрана, кодер генерирует и открывает модель Simulink, которая содержит блок HDL Cosimulation для каждого поддерживаемого симулятора HDL.

Если вы хотите сгенерировать HDL, Cosimulation блокируется только (не генерируя код испытательного стенда HDL), очистите HDL test bench.

Следующий рисунок показывает и HDL test bench и выбранный Cosimulation blocks.

В диалоговом окне Generate HDL нажмите Generate, чтобы сгенерировать код испытательного стенда и HDL.

В дополнение к обычным файлам кода кодер генерирует модель Simulink, содержащую блок HDL Cosimulation для каждого симулятора HDL, поддержанного HDL Verifier.

Сгенерированная модель не названа и существует в памяти только. Обязательно сохраните его в папку назначения, если вы хотите сохранить модель и блоки для использования на будущих сеансах.

Чтобы сконфигурировать HDL, параметры блоков Cosimulation, такие как синхронизация, задержка, и типы данных, видят, Задают HDL Интерфейс Блока Cosimulation (HDL Verifier).

Альтернатива командной строки: используйте generatehdl функция со свойством GenerateCosimBlock сгенерировать HDL блоки Cosimulation.

Чтобы использовать эту функцию, у вас должна быть лицензия HDL Verifier.

Кодер генерирует модель Simulink, которая запускает симуляцию Simulink вашего создания фильтра, и также cosimulation вашего проекта с симулятором HDL. Модель сравнивает выходные параметры фильтра Simulink с результатами симуляции HDL.

Сгенерированная модель включает:

Поведенческая модель создания фильтра, понятого в Подсистеме Simulink. Подсистема реализует создание фильтра с помощью базисных блоков, таких как сумматоры и задержки.

Соответствующий блок HDL Cosimulation. Кодер конфигурирует этот блок к cosimulate создание фильтра с помощью Simulink с любым из следующего:

Наставник Graphics® ModelSim®

Cadence Incisive®

Данные о тестовом воздействии, вычисленные от стимула испытательного стенда, вы задаете. Кодер хранит тестовые данные в переменной inputdata рабочего пространства модели. Блок From Workspace направляет тестовые данные к подсистеме фильтра и HDL блоки Cosimulation.

Блок Scope, который позволяет вам наблюдать и сравнить сигнал тестового воздействия с выходными параметрами блока Filter и HDL cosimulation. Осциллограф также показывает различие (ошибка) между этими двумя выходными параметрами.

Генерация cosimulation модели требует указанных входных параметров и/или выходных параметров (см. Ограничения). Прежде, чем сгенерировать модель, убедитесь, что ваша модель удовлетворяет это требование, можно следующим образом:

Выберите панель Global Settings диалоговое окно Generate HDL.

В панели Global Settings кликните по вкладке Ports. Опции порта появляются.

Выберите обе из следующих опций:

Add input register

Add output register

Сгенерировать модель:

В диалоговом окне Generate HDL сконфигурируйте другую генерацию кода и параметры испытательного стенда как требуется вашим проектом.

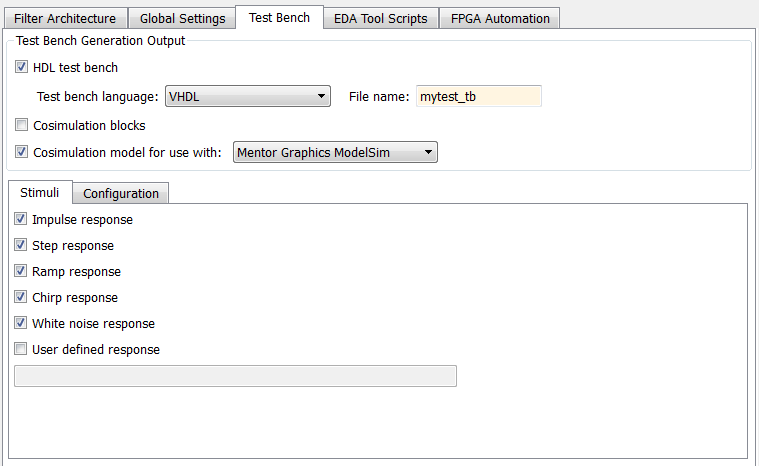

Выберите панель Test bench диалогового окна Generate HDL.

Выберите опцию Cosimulation model for use with:. Выбирание этой опции включает смежное выпадающее меню, где можно выбрать Mentor Graphics ModelSim или Cadence Incisive.

Используя выпадающее меню, выберите, какой тип блока HDL Cosimulation вы хотите в сгенерированной модели. Выберите Mentor Graphics ModelSim (значение по умолчанию) или Cadence Incisive.

В следующем рисунке cosimulation типом модели является Mentor Graphics ModelSim, и сигналом стимула является White noise response.

В диалоговом окне Generate HDL нажмите Generate, чтобы сгенерировать код испытательного стенда и HDL.

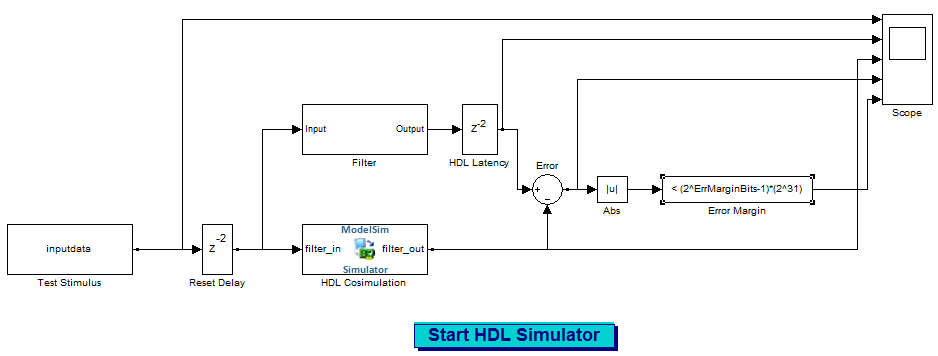

В дополнение к обычным файлам кода кодер генерирует и открывает модель Simulink. Следующий рисунок показывает модель, сгенерированную от настройки кодера, показанной на предыдущем шаге.

Сгенерированная модель не названа и существует в памяти только. Обязательно сохраните его в папку назначения, если вы хотите сохранить модель и блоки для использования на будущих сеансах.

Чтобы сконфигурировать HDL, параметры блоков Cosimulation, такие как синхронизация, задержка, и типы данных, видят, Задают HDL Интерфейс Блока Cosimulation (HDL Verifier).

Сгенерированная модель содержит следующие блоки:

Test Stimulus: Этот блок From Workspace направляет тестовые данные в переменной inputdata рабочего пространства модели к подсистеме фильтра и блокам HDL Cosimulation.

Filter: Эта подсистема понимает поведенческую модель создания фильтра.

HDL Cosimulation: Этот блок cosimulates сгенерированный HDL-код. Таблица HDL Cosimulation Block Settings описывает, как кодер конфигурирует cosimulation параметры блоков.

Reset Delay: Команды Tcl заданы в HDL Cosimulation блок применяет сигнал сброса. Сброс высок на уровне 0 нс и низко на уровне 22 нс (перед третьим возрастающим фронтом синхроимпульса). Симуляция Simulink начинает питать вход в 0, 10, 20 нс. Reset Delay блок добавляет задержку, таким образом, что первая выборка доступна для симуляции RTL, когда это готово после того, как сброс применяется.

HDL Latency: Эта задержка представляет различие между задержкой симуляции RTL и Simulink поведенческий блок.

Error: Вычисляет различие между выходными параметрами Filter блокируйтесь и HDL Cosimulation блок.

Abs: Абсолютное значение ошибочного расчета.

Error margin:: Индикатор, сравнивающий абсолютное значение ошибки со значением допуска на погрешность испытательного стенда (см. Установку Допуска на погрешность для Оптимизированного Кода Фильтра).

Scope: Отображает входной сигнал, выходные параметры от Filter блокируйтесь и HDL Cosimulation блоки и различие (если вы существуете) между двумя.

Start HDL Simulator кнопка: Запускает ваш HDL cosimulation программное обеспечение.

HDL настройки блока Cosimulation

| Панель | Настройки |

|---|---|

Ports | Имена порта: то же самое как имена в сгенерированном коде для фильтра. Типы данных ввода/вывода: Входной шаг расчета: Выходной шаг расчета: То же самое как Simulink зафиксированный размер шага. |

Clocks | Имя порта часов: то же самое как имя в сгенерированном коде для фильтра. Активный фронт синхроимпульса: Период: то же самое как шаг расчета Simulink. |

Timescales | 1 секунда в Simulink соответствует 1 метке деления в симуляторе HDL |

Connection | Режим связи: Метод связи: |

Tcl (Команды перед симуляцией) | force /Hlp/clk_enable 1; force /Hlp/reset 1 0 ns, 0 22 ns; puts ----------------------------------------- puts "Running Simulink Cosimulation block."; puts [clock format [clock seconds]] |

Tcl (Команды постсимуляции) | force /Hlp/reset 1 puts [clock format [clock seconds]] |

Сгенерированные Настройки Модели. Сгенерированная модель имеет следующие настройки не по умолчанию:

Solver: Discrete (no continuous states).

Решатель Type: Fixed-step.

Stop Time: Ts * StimLen, где Ts шаг расчета Simulink и StimLen длина стимула.

Sample Time Colors: активированный

Port Data Types: активированный

Hardware Implementation: ASIC/FPGA

cosimulation, который запускается, не сталкиваясь с ошибками, требует, чтобы выходные параметры от сгенерированного HDL-кода были синхронны с часами. Прежде, чем сгенерировать код, убедитесь, что обе из следующих опций выбраны:

Add input register

Add output register

Если вы не выбираете ни одну из этих опций, кодер отключает генерацию модели с ошибкой. Однако генерация кода испытательного стенда завершается.

Кодер не поддерживает генерацию cosimulation модели, когда выходным языком является Verilog, и данные, типа double, сгенерированы.

Используйте generatehdl функция, передающая в одном из следующих значений для свойства GenerateCosimModel.

generatehdl(filtSysObj,'InputDataType',numerictype(1,16,15), ... 'GenerateCosimModel','Incisive');

generatehdl(filtSysObj,'InputDataType',numerictype(1,16,15), ... 'GenerateCosimModel','ModelSim');