Шаблоны модели SoC Blockset™ предоставляют шаблоны разработки и лучшые практики для моделей, предназначенных для симуляции, генерации HDL-кода или развертывания SoC. Моделям, созданным из любого из шаблонов модели SoC Blockset, настраивали их параметры конфигурации для симуляции и генерации кода.

Чтобы эффективно смоделировать оборудование для проекта SoC, создайте проект при помощи шаблона SoC Blockset.

Во вкладке Home MATLAB® нажмите кнопку Simulink. В качестве альтернативы в командной строке, введите:

simulink

На Simulink® Start Page прокрутите вниз к разделу SoC Blockset, который содержит ссылки на шаблоны SoC для общих рабочих процессов. Выберите шаблон и сохраните проект. Папка проекта открывается в вашей рабочей области, содержащей:

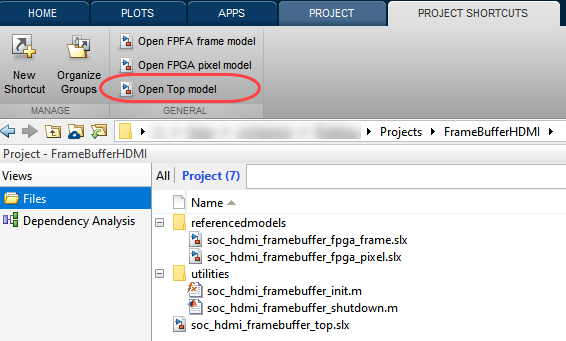

Модель с именем soc_*_top.slx – Модель верхнего уровня для проекта SoC.

referencedmodels – На папку, содержащую модели, ссылаются от топ-модели. Некоторые шаблоны включают модель FPGA и модель процессора. Другие шаблоны только включают тот модель, на которую ссылаются: модель FPGA или модель процессора.

utilities – Папка, содержащая служебные функции или данные об испытательном стенде, используется моделью.

Чтобы открыть модель верхнего уровня в Simulink, на вкладке Project Shortcuts, нажимают Open Top model.

В каждом шаблоне перейдите с блоками, отмеченными FPGA Algorithm в модели FPGA или Processor Algorithm в модели процессора. Эти блоки подсвечены для легкого обнаружения. Замените блоки шаблона на свою собственную модель алгоритма.

Чтобы легко найти блоки алгоритма, следуйте аннотациям в иерархии модели.

Чтобы открыть Библиотеку блоков SoC Blockset, нажмите кнопку Library Browser, затем выберите SoC Blockset на левой панели. В качестве альтернативы в командной строке, введите:

soclib

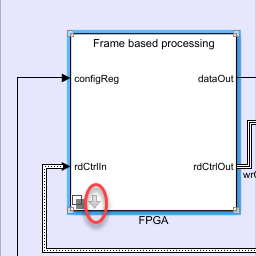

Топ-модель в шаблоне SoC Blockset включает подсистему FPGA, которая представляет логику, предназначенную, чтобы программировать FPGA. Подсистема FPGA включает два варианта модели Simulink:

Основанная на системе координат модель FPGA – Для расширенной производительности симуляции

Основанная на выборке модель FPGA – Для точности цикла и генерации кода

Топ-модель также включает подсистему процессора, которая представляет программу, предназначенную, чтобы работать на процессоре SoC. И FPGA и главные подсистемы содержат блоки, отмеченные как Алгоритм Алгоритма или Процессора FPGA. Замените эти алгоритмы на свою собственную логику. Топ-модель шаблона также включает систему памяти с каналами памяти и контроллером памяти. Эти блоки представляют систему физической памяти на плате. Модель часто включает канал регистра (чтобы включить связь между процессором и FPGA), испытательный стенд или блоки ввода-вывода.

От топ-модели откройте модель FPGA путем нажатия на стрелу в левой нижней части блока FPGA:

Модель FPGA содержит два варианта модели: основанный на системе координат вариант и основанный на выборке вариант. Дважды кликните вариант модели, который вы хотите изменить. Модель FPGA обычно включает две основных подсистемы для вас, чтобы изменить:

Обертка Алгоритма FPGA – Дважды кликает, чтобы открыть модель. Обертка алгоритма содержит зеленым подсвеченную подсистему под названием FPGA Algorithm. Этот блок имеет два входных параметров и один выход и реализован как множитель. Замените этот блок на свой собственный алгоритм FPGA. Добавьте вводы и выводы как требуется.

Протестируйте Исходную Обертку – Этот блок включает тестовый источник и предназначается, чтобы сгенерировать стимул как вход к алгоритму FPGA. Измените тестовый источник к своим потребностям или замените его на альтернативный исходный блок. Если вход к вашему алгоритму FPGA направляется от блока I/O, такого как HDMI или SDR, рассмотрите использование определенного шаблона приложений.

Не все шаблоны включают Тестовый Исходный блок в модель FPGA.

Модель процессора включает блок Task Manager и обертку процессора. Шаблон реализует алгоритм процессора как "передачу" через провод. Откройте обертку алгоритма процессора и замените блок Processor Algorithm (подсвеченный в синем) с вашим желаемым алгоритмом.

Топ-модель шаблона также включает канал регистра, чтобы связаться между процессором и моделью FPGA. Используйте канал регистра, чтобы сконфигурировать режим FPGA, l или считать и проверять регистры состояния. Блок Register Channel в шаблоне включает один регистр. Чтобы добавить дополнительные регистры, необходимо изменить параметры блоков канала регистра, алгоритм FPGA и алгоритм процессора:

Добавьте, что регистры к каналу регистра – Дважды кликают блок Register Channel, чтобы открыть маску блока и добавить дополнительные регистры по мере необходимости. Добавление регистров создает дополнительные порты на блоке Register Channel. Для получения дополнительной информации смотрите Register Channel.

Добавьте, что порты к модели процессора – Перешли к модели Processor Algorithm Wrapper. Чтобы перейти к модели процессора, нажмите Open Processor model на вкладке Project Shortcuts. Дважды кликните Processor Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте выходной порт в модуль и добавьте логику, чтобы управлять значением к добавленному выходному порту. Для регистров чтения добавьте входной порт и логику, чтобы обработать информацию, возвращенную в регистр чтения. От топ-модели соедините порт с блоком Register Channel.

Добавьте, что порты к модели FPGA – Перешли к модели FPGA Algorithm Wrapper. Чтобы перейти к основанной на FPGA/системе координат модели обработки, нажмите Open FPGA sample model на вкладке Project Shortcuts. Дважды кликните FPGA Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте входной порт в модуль и логику, чтобы обработать информацию, возвращенную в регистр чтения. Для регистров чтения добавьте выходной порт и логику, чтобы управлять значением к добавленному выходному порту.

Для эквивалентного поведения при использовании Simulink основанный на выборке вариант повторите этот шаг для основанной на выборке модели обработки в обертке FPGA.

От топ-модели соедините новый порт с блоком Register Channel.

Memory Controller | Memory Channel | Register Channel | Task Manager