Сверхдискретизируйте, отфильтруйте и проредите входные сигналы — оптимизированный для генерации HDL-кода

Поддержка HDL DSP System Toolbox> Фильтрация

dsphdlfiltering

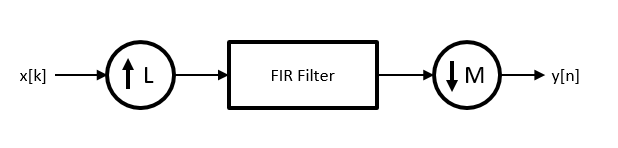

Блок FIR Rate Conversion HDL Optimized сверхдискретизировал, фильтрует и прореживает входные сигналы. Это оптимизировано для генерации HDL-кода и работает с одной выборкой каждого канала за один раз. Блок реализует эффективную многофазную архитектуру, чтобы избежать ненужных арифметических операций и высоких промежуточных частот дискретизации.

Блок сверхдискретизировал целочисленным коэффициентом L, применяет КИХ-фильтр и прореживает целочисленным коэффициентом M.

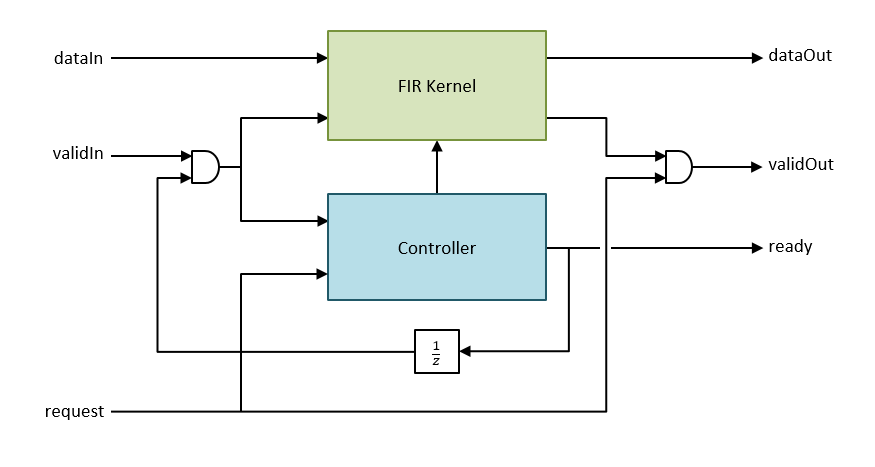

Блок имеет порты управления ввода и вывода для того, чтобы следовать по потоку выборок. В настройке по умолчанию блок использует validIn и validOut управляющие сигналы. Для дополнительного управления потоками можно включить ready выходной сигнал и request входной сигнал.

ready выходной порт указывает, что блок может принять новую выборку входных данных на следующем временном шаге. Когда L ≥ M, можно использовать ready сигнал достигнуть непрерывных выборок выходных данных. Если вы применяете новую входную выборку после каждого раза, когда блок возвращает ready = true, блок возвращает выборку вывода данных с validOut = true на каждом временном шаге.

Когда вы не включаете ready порт, можно применить допустимую выборку данных только каждый ceil(L/M) временные шаги. Например:

L/M = 4/5 — можно применить новую входную выборку на каждый временной шаг.

L/M = 3/2 — можно применить новую входную выборку на любой временной шаг.

Когда вы включаете request входной порт, блок возвращает следующую выходную выборку когда request true и допустимая выходная выборка доступна. Когда вы не используете request , блок возвращает выходные выборки, когда они доступны. Когда нет новых данных доступно, блок возвращает validOut = false.

Можно соединить request входной порт к ready выходной порт нисходящего блока.

Этот значок показывает все дополнительные порты блока FIR Rate Conversion HDL Optimized. ![]()

| Порт | Направление | Описание | Тип данных |

|---|---|---|---|

dataIn | Входной параметр | Выборка данных в виде скаляра, или как вектор-строка, в котором каждый элемент представляет независимый канал. Блок принимает действительные или комплексные данные. |

|

validIn | Входной параметр | Получите значение dataIn, когда validIn true. Можно применяться, допустимые данные производят каждый ceil(L/M) временные шаги. | boolean |

request | Введите (Необязательно) | Запросите для новой выходной выборки. | boolean |

dataOut | Вывод | Передискретизируемая и отфильтрованная выборка данных, возвращенная как скаляр, или как вектор, в котором каждый элемент представляет независимый канал. | То же самое как dataIn |

validOut | Вывод | Проверка dataOut значение. Когда validOut true, dataOut isvalid. | boolean |

ready | Выведите (Необязательно) | Указывает, что блок готов к новой входной выборке, когда ready true. | boolean |

Сверхдискретизировав фактор, L в виде скалярного целого числа. Значение по умолчанию равняется 3.

Прореживая фактор, M в виде скалярного целого числа. Значение по умолчанию равняется 2.

Отфильтруйте коэффициенты в виде вектора в убывающих степенях z-1.

Можно сгенерировать коэффициенты фильтра с помощью функций создания фильтра Signal Processing Toolbox™ (таких как fir1). Спроектируйте фильтр lowpass с нормированной частотой среза, не больше, чем min(1/L,1/M). Блок инициализирует внутренние состояния фильтра, чтобы обнулить. Коэффициентами по умолчанию является firpm(70,[0 .28 .32 1],[1 1 0 0]).

Установите этот флажок, чтобы включить порт, который указывает, когда блок может, на следующем временном шаге, принять новую выборку входных данных.

Установите этот флажок, чтобы включить порт, который запрашивает, чтобы блок возвратил выходную выборку. Когда request портом является true, и существует выходная доступная выборка, блок возвращает новую выходную выборку и устанавливает validOut к true. Когда request false, или нет никакой новой доступной выборки, блок устанавливает validOut к false.

Методом округления значения по умолчанию для внутренних вычислений фиксированной точки является Floor. Simplest округление режима не поддержано.

Обработка Переполнения по умолчанию для внутренних вычислений фиксированной точки является переносом.

Тип данных КИХ фильтрует коэффициенты в виде fixdt(s,wl,fl) объект с signedness, word length, и fractional length свойства. Значением по умолчанию является fixdt(1,16,16).

Тип данных выборок выходных данных. Можно выбрать Inherit: Inherit via internal rule, Inherit: Full precision, или задайте fixdt(s,wl,fl) объект. Значением по умолчанию является Inherit: Same word length as input.

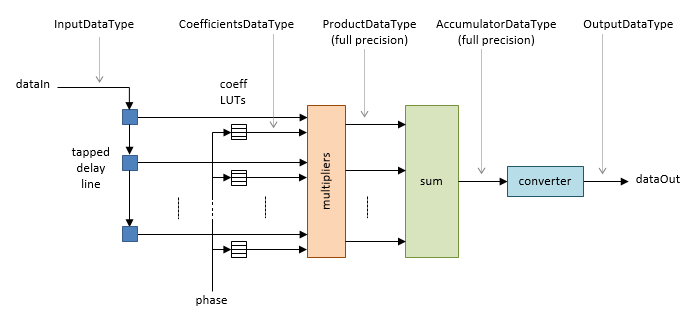

Блок FIR Rate Conversion HDL Optimized реализует полностью параллельную многофазную архитектуру фильтра. Схема показывает, куда блок бросает типы данных, согласно вашей настройке.

Модели HDL блока конвейерно обрабатывают задержку, таким образом, существует начальная задержка нескольких временных шагов, прежде чем объект возвратит первую допустимую выходную выборку. Задержка зависит от коэффициентов фильтра и факторов передискретизации. Чтобы определить задержку из первой выборки в к первой выборке, наблюдайте validOut сигнал.

Для выборки проектных показателей сгенерируйте HDL для блока, как сконфигурировано в Скорости передачи данных Управления Используя Готовое и пример Портов Запроса. Фильтр в качестве примера передискретизирует в 5/2 и использует симметричный фильтр с 71 касанием. Входные выборки и коэффициенты фильтра 16 битов шириной. Проект был предназначен к Xilinx® Virtex®-6 FPGA, с помощью Xilinx синтез ISE и инструменты маршрута и место.

После места и маршрута, проект достигает частоты часов на 535 МГц. Это использует эти ресурсы.

| LUT | 592 |

| FFS | 979 |

Xilinx LogiCORE® DSP48 | 15 |

| Блокируйте RAM (16K) | 0 |

Производительность синтезируемого HDL-кода варьируется в зависимости от ваших коэффициентов фильтра, цели FPGA и опций синтеза.