Обнаружение мертвой логики помогает вам идентифицировать:

Ошибки проектирования модели.

Посторонние элементы модели.

Элементы модели, которые должны быть выполнены, но не являются.

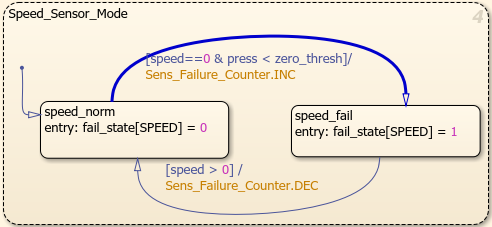

В этом примере вы анализируете топливную модель контроллера скорости, чтобы определить, содержит ли модель мертвую логику. Обнаружение мертвой логики находит неправильное значение переменных, которое заставляет условие перехода в графике Stateflow® оставаться неактивным.

Откройте модель.

sldvdemo_fuelsys_logic_simple

Убедитесь, что текущая папка перезаписываема.

Сконфигурируйте обнаружение мертвой логики.

На вкладке Design Verifier, в разделе Mode, выбирают Design Error Detection.

Выберите Error Detection Settings.

В диалоговом окне Configuration Parameter выберите Dead logic. Очистите Identify active logic. Нажмите OK.

Нажмите Detect Design Errors.

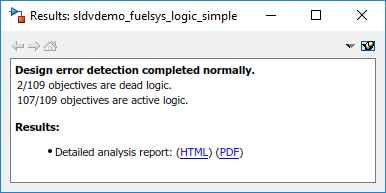

Диалоговое окно результатов показывает, что существуют 2/109 цели, которые являются мертвой логикой.

Создайте аналитический отчет. От инспектора результатов окно нажмите HTML.

Прокрутите к разделу Dead Logic под Design Error Detection Objectives Status. Таблица приводит два экземпляра мертвой логики.

В столбце Description одним из экземпляров мертвой логики является false условие press < zero_thresh. Результат мертвой логики показывает на это в симуляции, false условие не выполнялось. Эта логика является частью Sens_Failure_Counter.INC переход.

Щелкните по ссылке Model Item. Simulink подсвечивает переход в графике.

Логический оператор, управляющий переходом,

speed==0 & press < zero_thresh

Возвратитесь к отчету. Прокрутите к разделу Constraints.

Значение входа control logic/Input Data "press" ограничивается от 0 до 2. Щелкните по ссылке, чтобы открыть вход в Model Explorer.

Выберите Model Workspace в Model Explorer. В таблице содержимого выберите zero_thresh. Значение zero_thresh 250.

Учитывая ограниченное значение press, это всегда меньше zero_thresh и поэтому, false условие никогда не осуществляется.

Измените значение zero_thresh к 0,250.

Повторно анализируйте модель. На вкладке Design Verifier нажмите Detect Design Errors.

В новых результатах цель является более не мертвой логикой.