Модель тестовой обвязки обеспечивает изолированную среду, чтобы протестировать конструктивные изменения. Можно создать модель тестовой обвязки во время анализа Simulink® Design Verifier™ или после анализа.

Содержимое модели тестовой обвязки зависит от значения параметра Mode, установленного в диалоговом окне Configuration Parameters на панели Design Verifier:

Design error detection — Модель тестовой обвязки содержит тесты, которые приводят к ошибкам в процессе моделирования.

Test generation — Модель тестовой обвязки содержит тесты, которые достигают целей тестирования.

Property proving — Модель тестовой обвязки содержит контрпримеры, которые фальсифицируют цели доказательства.

По умолчанию параметр Generate separate harness model after analysis отключен.

Программное обеспечение Simulink Design Verifier генерирует модель тестовой обвязки только, когда модель верхнего уровня, которую вы анализируете, содержит блок Inport.

Чтобы создать модель тестовой обвязки прежде или после анализа, используйте эти методы:

Перед анализом, в диалоговом окне Configuration Parameters, на Design Verifier> панель Results, выбирают Generate separate harness model after analysis.

После анализа, в окне Simulink Design Verifier Results Summary, выбирают Create harness model.

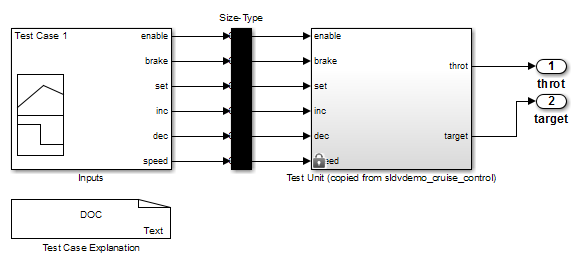

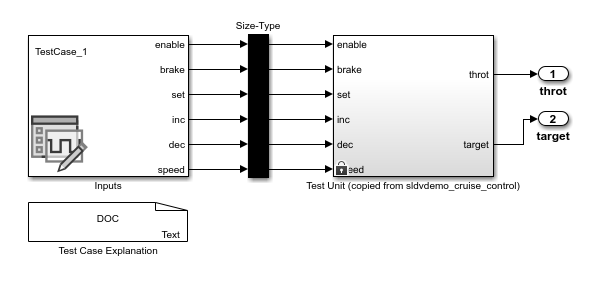

Программное обеспечение Simulink Design Verifier создает модель тестовой обвязки, которая содержит эти элементы:

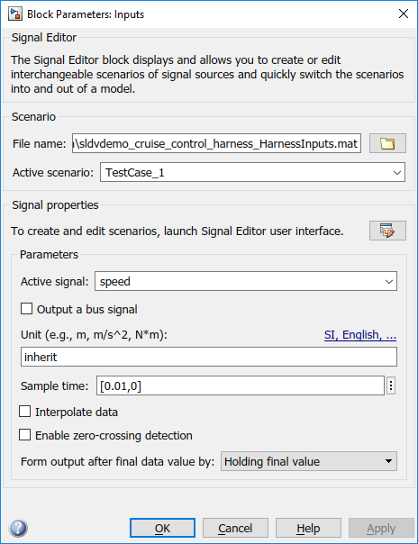

Блок Inputs — The Inputs является блоком Signal Builder или Signal Editor на основе исходного набора опции Обвязки в Design Verifier> панель Results.

Signal Builder: Этот блок содержит сигналы, которые состоят из тестов или контрпримеров, которые генерирует Simulink Design Verifier. Блок Signal Builder содержит сигналы только для входных сигналов, которые используются в модели. Если входной сигнал не оказывает влияния на выход модели, тот сигнал не включен в блок Signal Builder.

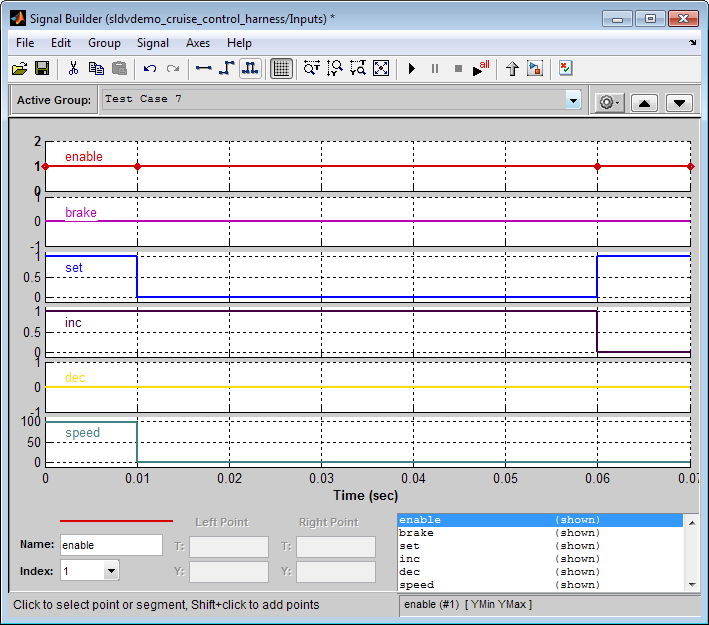

Чтобы открыть диалоговое окно Signal Builder и просмотреть его сигналы, дважды кликните блок Inputs. Каждая группа сигнала представляет уникальный тест или контрпример. Чтобы просмотреть сигналы, сопоставленные с конкретным тестом или контрпримером, в диалоговом окне Signal Builder, выбирают Active Group.

После того, как Simulink Design Verifier выполняет анализ генерации тестов sldvdemo_cruise_control модель с опциями по умолчанию, этот блок Signal Builder показывает сигналы для Test Case 7.

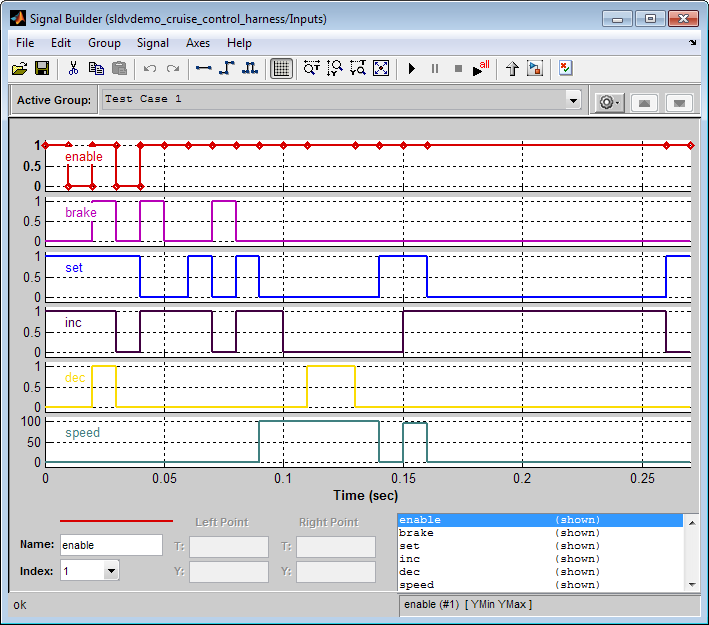

Если вы выбираете LongTestcases опция параметра Test suite optimization, анализ создает меньше, более длинные тесты. Например, если вы выбираете LongTestcases опция для sldvdemo_cruise_control модель, анализ производит один длинный тест вместо девяти более коротких тестов. Это диалоговое окно Signal Builder показывает сигналы для длинного теста. Для получения дополнительной информации о диалоговом окне Signal Builder, смотрите Signal Groups (Simulink).

Signal Editor: Этот блок содержит сценарии, которые состоят из тестов или контрпримеров, которые генерирует Simulink Design Verifier. Блок Signal Editor содержит сигналы только для входных сигналов, которые используются в модели. Если входной сигнал не оказывает влияния на выход модели, тот сигнал не включен в блок Signal Editor.

После того, как Simulink Design Verifier генерирует модель тестовой обвязки, входной MAT-файл для блока Signal Editor сохранен в местоположении по умолчанию <current_folder>\sldv_output\<model_name>\<model_name>_harness_HarnessInputs.mat.

Чтобы открыть диалоговое окно Signal Editor и просмотреть сценарии источников сигнала, дважды кликните блок Inputs. Active scenario перечисляет тесты или контрпримеры. Чтобы создать и отредактировать сценарии, запустите пользовательский интерфейс Редактора Сигнала. Для получения дополнительной информации смотрите, Создают и Данные сигнала Редактирования (Simulink).

Блок Size-Type — This Subsystem передает сигналы от блока Inputs до блока Test Unit. Это проверяет, что размер и тип данных сигналов сопоставимы с блоком Test Unit.

Блок Test Unit — This Subsystem содержит копию исходной модели, которую анализировал Simulink Design Verifier.

Если вы выбираете Reference input model in generated harness на Design Verifier> панель Results, Тестовый Модуль является блоком Model, который ссылается на модель, которую вы анализируете, не подсистема.

Если Тестовый Модуль в модели тестовой обвязки является подсистемой, значения параметров на Optimization и панелях Math and Data Types могут повлиять на результаты покрытия.

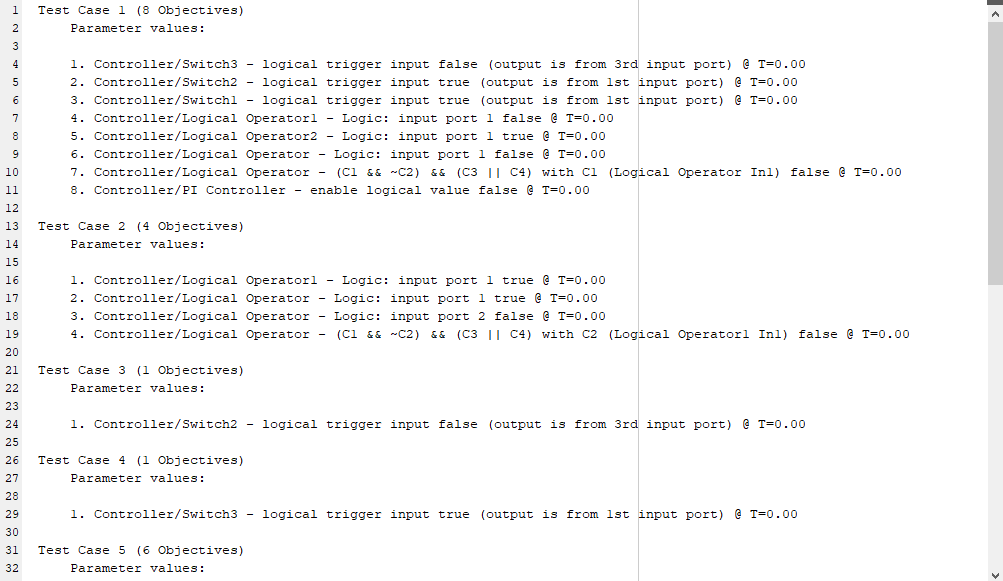

Блок Test Case Explanation — This DocBlock документирует тесты или контрпримеры, которые генерирует Simulink Design Verifier. Чтобы просмотреть описание каждого теста или контрпримера, дважды кликните блок Test Case Explanation. Черные списки или цели тестирования, которых каждый тест достигает или цели доказательства, которые фальсифицирует каждый контрпример.

Simulink Design Verifier генерирует модель тестовой обвязки с этими настройками.

Временем начала модели тестовой обвязки всегда является 0. Если исходная модель использует ненулевое время начала, программное обеспечение игнорирует время начала и использует 0 в течение времени начала симуляции для тестов и контрпримеров.

Время остановки модели тестовой обвязки всегда равняется времени остановки самого длинного теста в блоке Inputs.

По умолчанию программное обеспечение включает анализ покрытия и генерирует отчет покрытия для моделей тестовой обвязки, которые содержат тесты. Создание отчетов покрытия включено с опциями по умолчанию. Можно настроить эти настройки при помощи, Задают Опции Покрытия (Simulink Coverage).

По умолчанию, если вы выбираете Ignore objective based on filter и обеспечиваете файл фильтра покрытия для Тестового Модуля, файл фильтра покрытия применяется к модели тестовой обвязки. Для получения дополнительной информации смотрите файл данных Покрытия.

Модель тестовой обвязки сгенерирована с ними блок Inputs, независимо от Harness source, который вы задаете:

Для моделей, которые используют блок Inport составного типа, блок Signal Editor используется в качестве источника обвязки.

Для моделей, которые используют массив шин как блок Inport, блок Signal Builder используется в качестве источника обвязки.

Для моделей, который использует и составной тип и массив шин, когда блокируется Inport, генерация модели тестовой обвязки не поддержана.

Модель тестовой обвязки позволяет вам симулировать копию своей исходной модели при помощи тестов или контрпримеров, которые генерирует Simulink Design Verifier. Используя модель тестовой обвязки, можно симулировать:

Контрпример.

Один тест, для которого программное обеспечение Simulink Coverage™ собирает и отображает информацию о покрытии модели.

Все тесты, для которых программное обеспечение Simulink Coverage собирает и отображает совокупную информацию о покрытии модели.

Если вы анализируете модель, которая симулирована с предупреждениями шага расчета, когда вы симулируете модель тестовой обвязки, о предупреждениях можно сообщить как ошибки, заставив симуляцию перестать работать.

Симулировать один тест или контрпример:

В модели тестовой обвязки дважды кликните блок Inputs.

В диалоговом окне Signal Builder выберите Active Group с конкретным тестом или контрпримером.

Диалоговое окно Signal Builder отображается сигналы, которые включают выбранный тест или контрпример.

Нажмите кнопку Start simulation![]() .

.

Программное обеспечение Simulink симулирует модель тестовой обвязки при помощи сигналов, сопоставленных с выбранным тестом или контрпримером. При симуляции теста программное обеспечение Simulink Coverage собирает информацию покрытия модели и отображает отчет покрытия.

Симулировать все тесты и измерять их объединенное покрытие модели:

В модели тестовой обвязки дважды кликните блок Inputs.

В диалоговом окне Signal Builder нажмите кнопку Run all![]() .

.

Программное обеспечение Simulink симулирует модель тестовой обвязки при помощи всех тестов, в то время как программное обеспечение Simulink Coverage собирает информацию покрытия модели и отображает отчет покрытия.

Когда вы нажимаете Run all, программное обеспечение симулирует все тесты при помощи времени остановки для модели тестовой обвязки. Время остановки равняется времени остановки для самого длинного теста, таким образом, вы можете накопить дополнительное покрытие, когда вы симулируете более короткие тесты.

Для получения дополнительной информации смотрите Симуляцию с Signal Groups (Simulink).

Симулировать один тест или контрпример:

В модели тестовой обвязки дважды кликните блок Inputs.

В диалоговом окне Signal Editor выберите Active scenario с конкретным тестом или контрпримером и нажмите OK.

В редакторе Simulink нажмите кнопку Run.

Программное обеспечение Simulink симулирует модель тестовой обвязки при помощи сценария источников сигнала, сопоставленных с выбранным тестом или контрпримером. При симуляции теста программное обеспечение Simulink Coverage собирает информацию покрытия модели и отображает отчет покрытия.

Чтобы симулировать все тесты и измерить их объединенное покрытие модели, используйте cvsim или parsim команда. Например, смотрите, Симулируют Модель тестовой обвязки с редактором Инпутсом Блоком Сигнала.

Создайте модель тестовой обвязки | Создание и выполнение тестов