Этот пример использует slvnvdemo_powerwindow модель, чтобы показать, как проверить компонент в контексте модели, которая содержит тот компонент. Когда вы работаете через этот пример, вы используете функции верификации компонента Simulink® Design Verifier™, чтобы создать тесты и покрытие меры для модели, на которую ссылаются. Кроме того, можно выполнить модель, на которую ссылаются, и в режиме симуляции и в программном обеспечении в режиме Loop (SIL) с помощью API Верификации генерации кода (CGV).

У вас должны быть следующие лицензии на продукты, чтобы запустить этот пример:

Stateflow®

Embedded Coder®

Simulink Coder™

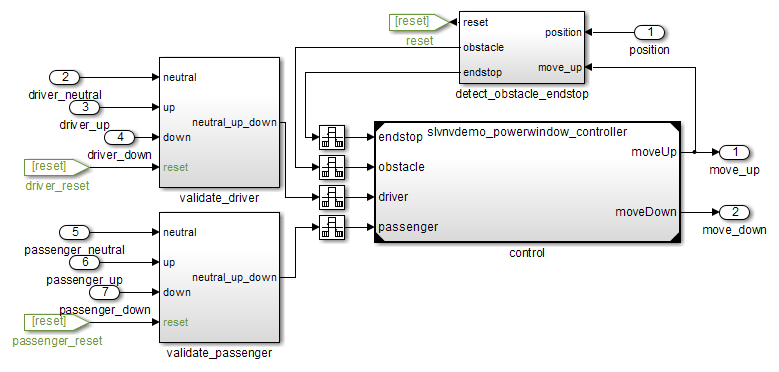

Компонент, который вы проверяете, является блоком Model под названием control. Этот компонент находится в power_window_control_system подсистема в верхнем уровне slvnvdemo_powerwindow модель. power_window_control_system подсистему показывают ниже.

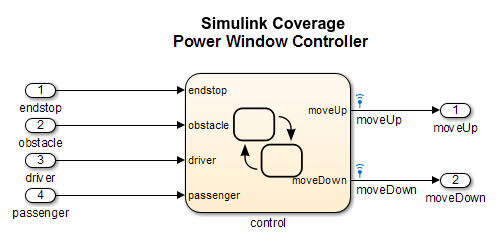

control Блок Model ссылается на slvnvdemo_powerwindow_controller модель.

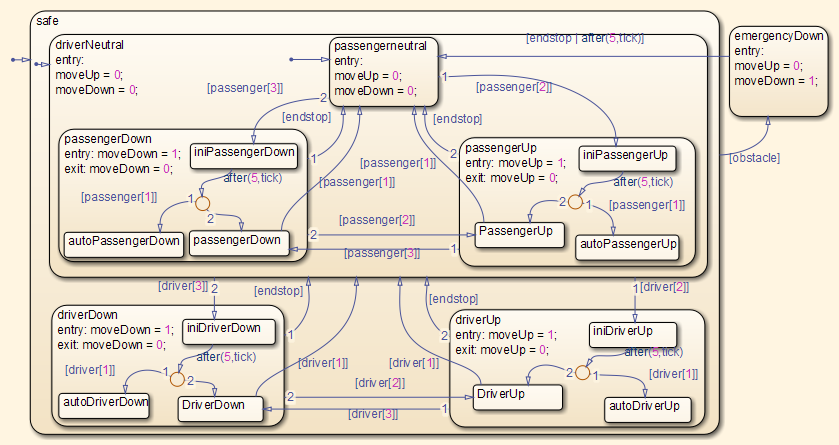

Модель, на которую ссылаются, содержит диаграмму Stateflow control, который реализует логику для контроллера окна со стеклоподъемником.

Проверять модель slvnvdemo_powerwindow_controller, на которую ссылаются,, создайте модель тестовой обвязки, которая содержит входные сигналы, которые симулируют контроллер в модели объекта управления:

Откройте slvnvdemo_powerwindow модель в качестве примера и модель, на которую ссылаются:

open_system('slvnvdemo_powerwindow'); open_system('slvnvdemo_powerwindow_controller');

Откройте power_window_control_system подсистема в модели в качестве примера.

Блок Model под названием control в power_window_control_system подсистема ссылается на компонент, который вы проверяете во время этого примера, slvnvdemo_powerwindow_controller.

Симулируйте блок Model, это ссылается на slvnvdemo_powerwindow_controller модель и журнал входные сигналы с блоком Model:

loggedSignalsPlant = sldvlogsignals( ... 'slvnvdemo_powerwindow/power_window_control_system/control');

sldvlogsignals хранит регистрируемые сигналы в loggedSignalsPlant.

Сгенерируйте модель тестовой обвязки с регистрируемыми сигналами:

harnessModelFilePath = sldvmakeharness( ... 'slvnvdemo_powerwindow_controller', loggedSignalsPlant);

sldvmakeharness создает и открывает модель тестовой обвязки под названием slvnvdemo_powerwindow_controller_harness. Блок Signal Builder содержит один тест, содержащий регистрируемые сигналы.

Для получения дополнительной информации о моделях тестовой обвязки, смотрите Модели тестовой обвязки Simulink Design Verifier.

Для использования позже в этом примере, сохраните имя модели тестовой обвязки:

[~, harnessModel] = fileparts(harnessModelFilePath);

Оставьте все окна открытыми для следующей части этого примера.

Затем вы запишете покрытие для slvnvdemo_powerwindow_controller модель.

Покрытие модели является мерой того, как полностью тест тестирует модель и процент трасс, которые осуществляет тест. Записывать покрытие для slvnvdemo_powerwindow_controller модель:

Создайте объект опций по умолчанию, требуемый sldvruntest функция:

runOpts = sldvruntestopts;

Задайте, чтобы симулировать модель и покрытие записи:

runOpts.coverageEnabled = true;

Симулируйте покрытие записи и модели, на которое ссылаются:

[~, covDataFromLoggedSignals] = sldvruntest( ... 'slvnvdemo_powerwindow_controller', loggedSignalsPlant, runOpts);

Отобразите отчет покрытия HTML:

cvhtml('Coverage with Test Cases', covDataFromLoggedSignals);slvnvdemo_powerwindow_controller модель достигла:

Decision Coverage: 40%

Покрытие условия: 35%

Покрытие MCDC: 10%

Для получения дополнительной информации о Decision Coverage, покрытие условия и покрытие MCDC, видят Типы Покрытия модели (Simulink Coverage).

Поскольку вы не достигли 100%-го покрытия для slvnvdemo_powerwindow_controller модель, затем, вы будете анализировать модель, чтобы записать дополнительное покрытие и создать дополнительные тесты.

Можно использовать Simulink Design Verifier, чтобы анализировать slvnvdemo_powerwindow_controller модель и собирает покрытие. Можно указать, что анализ игнорирует любые цели, которым ранее удовлетворяют, и записывает дополнительное покрытие.

Записывать дополнительное покрытие для модели:

Сохраните данные о покрытии, которые вы записали для регистрируемых сигналов в файле:

cvsave('existingCovFromLoggedSignal', covDataFromLoggedSignals);Создайте объект опций по умолчанию для анализа:

opts = sldvoptions;

Укажите, что анализ генерирует тесты, чтобы записать решение, условие и измененное условие/Decision Coverage:

opts.ModelCoverageObjectives = 'MCDC';Укажите, что анализ игнорирует цели, которым вы удовлетворили, когда вы регистрировали сигналы с блоком Model:

opts.IgnoreCovSatisfied = 'on';Задайте имя файла, который содержит данные о целях, которым удовлетворяют:

opts.CoverageDataFile = 'existingCovFromLoggedSignal.cvt';Укажите, что анализ не отображает невыполнимые цели в Диагностическом Средстве просмотра:

opts.DisplayUnsatisfiableObjectives = 'off';В данном примере особое внимание находится на удовлетворении как можно большему количеству целей.

Укажите, что анализ создает длинные тесты, которые удовлетворяют нескольким целям:

opts.TestSuiteOptimization = 'LongTestcases';Создание меньшего числа тестов, каждый из которых удовлетворяет нескольким целям тестирования, экономит время, когда вы выполняете сгенерированный код в следующем разделе.

Задайте, чтобы создать модель тестовой обвязки, которая ссылается на компонент с помощью блока Model:

opts.saveHarnessModel = 'on'; opts.ModelReferenceHarness = 'on';

Модель тестовой обвязки, в которой вы создали из регистрируемых сигналов, Готовится, Компонент для Верификации использует блок Model, это ссылается на slvnvdemo_powerwindow_controller модель. Модель тестовой обвязки, которую создает анализ, должна также использовать блок Model, это ссылается на slvnvdemo_powerwindow_controller. Можно добавить данные о тесте к первой модели тестовой обвязки, создав один тестовый набор.

Анализируйте модель с помощью Simulink Design Verifier:

[status, fileNames] = sldvrun('slvnvdemo_powerwindow_controller', ... opts, true);

Анализ создает и открывает модель тестовой обвязки slvnvdemo_powerwindow_controller_harness. Блок Signal Builder содержит один длинный тест, который удовлетворяет 74 целям тестирования.

Можно объединить этот тест с тестом, в котором вы создали, Готовят Компонент к Верификации, чтобы записать дополнительное покрытие для slvnvdemo_powerwindow_controller модель.

Сохраните имя новой модели тестовой обвязки и откройте его:

[~, newHarnessModel] = fileparts(fileNames.HarnessModel); open_system(newHarnessModel);

Затем вы объедините эти две модели тестовой обвязки, чтобы создать один тестовый набор.

Вы создали две модели тестовой обвязки когда вы:

Регистрируемый сигналы с блоком Model управления это ссылается на slvnvdemo_powerwindow_controller модель.

Анализируемый slvnvdemo_powerwindow_controller модель.

Если вы комбинируете тесты в обеих моделях тестовой обвязки, можно записать покрытие, которое получает вас ближе к достижению 100%-го покрытия:

Объедините модели тестовой обвязки путем добавления новых тестов к тестам для регистрируемых сигналов:

sldvmergeharness(harnessModel, newHarnessModel);

Блок Signal Builder в slvnvdemo_powerwindow_controller_harness модель теперь содержит оба теста.

Регистрируйте сигналы к модели тестовой обвязки:

loggedSignalsMergedHarness = sldvlogsignals(harnessModel);

Используйте объединенные тесты, чтобы записать покрытие для slvnvdemo_powerwindow_controller_harness модель. Во-первых, сконфигурируйте объект опций для sldvruntest:

runOpts = sldvruntestopts; runOpts.coverageEnabled = true;

Симулируйте модель и запишите и отобразите данные о покрытии:

[~, covDataFromMergedSignals] = sldvruntest( ... 'slvnvdemo_powerwindow_controller', loggedSignalsMergedHarness, ... runOpts); cvhtml('Coverage with Merged Test Cases', covDataFromMergedSignals);

slvnvdemo_powerwindow_controller модель теперь достигает:

Decision Coverage: 100%

Покрытие условия: 80%

Покрытие MCDC: 60%

Чтобы проверить, что сгенерированный код для модели приводит к тем же результатам как симуляция модели, используйте методы API Верификации генерации кода (CGV).

Чтобы выполнить модель в различных режимах выполнения, используйте API CGV, чтобы проверить числовую эквивалентность результатов. Для получения дополнительной информации о API CGV, смотрите Программируемую Верификацию Генерации кода (Embedded Coder).

Когда вы выполняете эту процедуру, симуляция компилирует и выполняет типовой код с помощью обоих тестов.

Создайте объект опций по умолчанию для sldvruncgvtest:

runcgvopts = sldvruntestopts('cgv');Задайте, чтобы выполнить модель в режиме симуляции:

runcgvopts.cgvConn = 'sim';Выполните slvnv_powerwindow_controller модель с помощью этих двух тестов и runcgvopts объект:

cgvSim = sldvruncgvtest('slvnvdemo_powerwindow_controller', ... loggedSignalsMergedHarness, runcgvopts);

Эти шаги сохраняют результаты в переменной cgvSim рабочей области.

Затем вы выполните ту же модель с теми же тестами в программном обеспечении в режиме Loop (SIL) и сравните результаты обеих симуляций.

Для получения дополнительной информации о Нормальном режиме симуляции, смотрите, Выполняют Модель (Embedded Coder).

Когда вы выполняете модель в программном обеспечении в режиме Loop (SIL), симуляция компилирует и выполняет сгенерированный код на вашем хосте - компьютере.

В этом разделе вы выполняете slvnvdemo_powerwindow_controller модель в режиме SIL и сравнивает результаты с предыдущим разделом, когда вы выполнили модель в режиме симуляции.

Задайте, чтобы выполнить модель в режиме SIL:

runcgvopts.cgvConn = 'sil';Выполните slvnv_powerwindow_controller модель с помощью этих двух тестов и runcgvopts объект:

cgvSil = sldvruncgvtest('slvnvdemo_powerwindow_controller', ... loggedSignalsMergedHarness, runcgvopts);

Переменная cgvSil рабочей области содержит результаты выполнения режима SIL.

Сравните результаты в cgvSil к результатам в cgvSim, созданный из выполнения режима симуляции. Используйте compare

for i=1:length(loggedSignalsMergedHarness.TestCases) simout = cgvSim.getOutputData(i); silout = cgvSil.getOutputData(i); [matchNames, ~, mismatchNames, ~ ] = ... cgv.CGV.compare(simout, silout); end

Отобразите результаты сравнения в Командном окне MATLAB®:

fprintf(['\nTest Case(%d):%d Signals match, %d Signals mismatch\r'],... i, length(matchNames), length(mismatchNames));

Как ожидалось, результаты этих двух соответствий симуляций.

Для получения дополнительной информации о программном обеспечении в цикле (SIL) симуляции, смотрите то, Что SIL и PIL симуляции? (Embedded Coder).