Система процессора в этом приложении SoC считывает данные из внешней памяти после записи от FPGA до той памяти. Поскольку записи FPGA и взаимодействие с внешней памятью являются асинхронными, процессор использует событийно-управляемую задачу читать из памяти. Программное обеспечение также управляет регистром на FPGA, который задает коэффициент умножения, который будет использоваться в алгоритме FPGA.

Откройте новую модель Simulink®. Сохраните модель как soc_hwsw_proc.slx в новую подпапку, названную processor, в папке проекта. Добавьте soc_hwsw_proc.slx модель к проекту.

В Simulink сконфигурируйте soc_hwsw_top.slx модель к как приложение SoC. На вкладке Apps, под Setup to Run on Hardware, clickSystem on Chip (SoC).

Во всплывающем окне System on Chip (SoC) выберите Hardware Board> Xilinx Zynq ZC706 evaluation kit. Нажмите Finish.

Модель процессора должна использовать ту же аппаратную плату и настройки параметра конфигурации решателя как модель верхнего уровня.

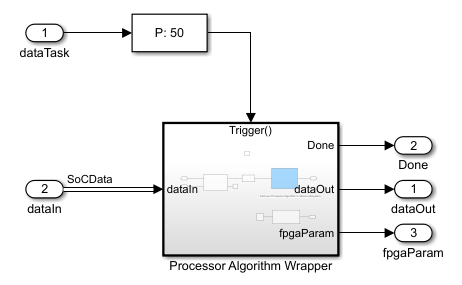

В модели, с помощью блока Function-Call Subsystem, блока Asynchronous Task Specification, блок Inport и блоки Outport, создают следующую систему.

В dataTask блокируйте диалоговую маску, проверяйте Signal Attributes> Output function call, чтобы осушить порт вызова функции на внешней модели.

В диалоговой маске блока Asynchronous Task Specification, набор Task priority к 50.

Приоритет задач блока Asynchronous Task Specification должен совпадать с приоритетом задачи в блоке Task Manager, управляющем этой задачей.

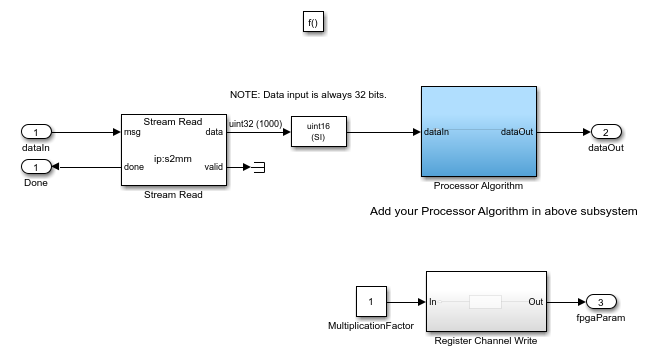

Processor Algorithm Wrapper подсистема считывает данные из внешней памяти только после каждой записи к внешней памяти FPGA.

Откройте Processor Algorithm Wrapper блок.

Используя блок Stream Read, блок Constant, блок Data Type Conversion и блоки Subsystem, создают следующую модель.

Откройте диалоговую маску блока Stream Read. Установите Number of buffers на 6.

Откройте диалоговую маску блока Data Type Conversion и установите Output data type на uint16.

Processor Algorithm подсистема служит основой, чтобы разработать ваш собственный алгоритм обработки.

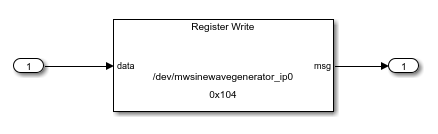

Откройте Register Channel Write блок подсистемы.

Добавьте блок Register Write, чтобы создать следующую модель.

Откройте диалоговую маску блока Register Write. Установите Device name на /dev/mwsinewavegenerator_ip0 и Offset address к hex2dec('100').

В папке проекта откройте модель soc_hwsw_top.slx.

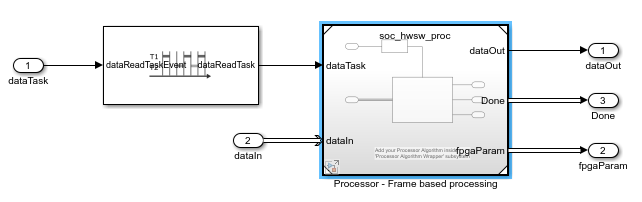

Добавьте блок Subsystem в Processor область и метка блок Processor.

В Processor подсистема, с помощью блока Task Manager и блока Model, создает следующую систему.

Откройте диалоговую маску блока Model и установите Model name на soc_hwsw_proc.slx.

Откройте диалоговую маску блока Task Manager. Поставите задачу Name к dataReadTask и набор Priority к 50. Во вкладке Simulation, набор Mean, Min и Max к 8e-05. Нажмите OK.