Можно настроить и отредактировать опции генерации HDL-кода и затем сгенерировать код в командной строке. Этот пример иллюстрирует, как можно использовать диалоговое окно Configuration Parameters, чтобы сгенерировать HDL-код для Симметричной КИХ-модели фильтра.

Прежде чем вы сгенерируете HDL-код, модель должна быть совместимой для генерации HDL-кода. Чтобы проверять и обновить вашу модель для совместимости HDL, смотрите Совместимость HDL Проверки Модели Simulink Используя Советника по вопросам HDL-кода. Можно также настроить параметры модели при помощи hdlsetup функция.

hdlsetup(gcs)

Этот пример использует Симметричную КИХ-модель фильтра, которая совместима для генерации HDL-кода. Открыть эту модель в командной строке, введите:

sfir_fixed

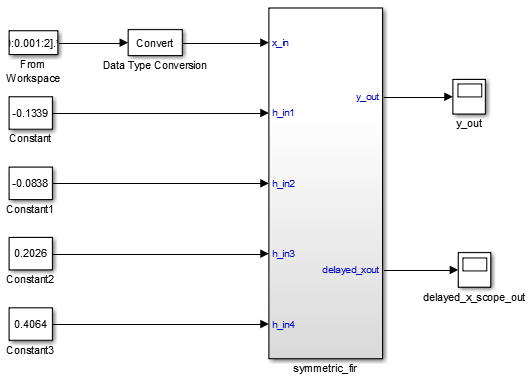

Модель использует разделение труда, которое подходит для проекта HDL.

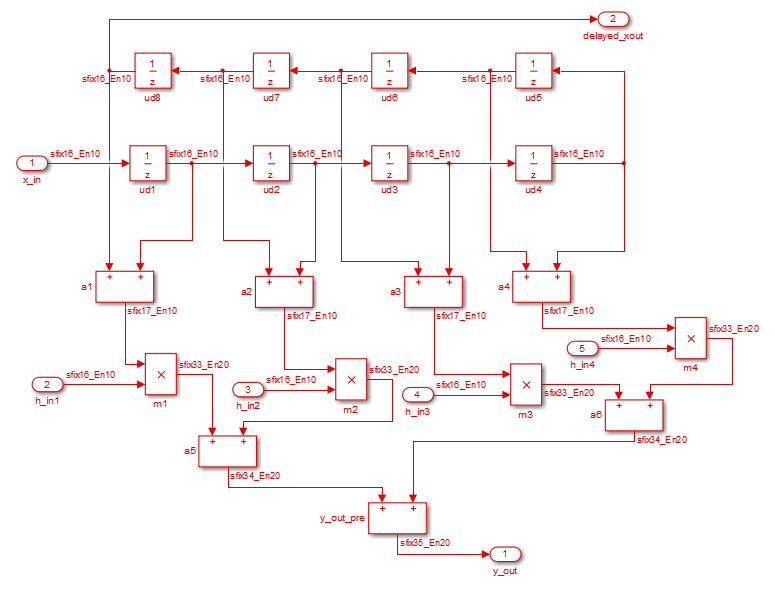

symmetric_fir подсистема, которая реализует алгоритм фильтра, является устройством под тестом (DUT). Сущность HDL сгенерирована от этой подсистемы.

Компоненты модели верхнего уровня, которые управляют подсистемой, работают испытательным стендом.

Модель верхнего уровня генерирует 16-битные входные сигналы фиксированной точки для symmetric_fir подсистема. Блок Signal From Workspace генерирует тестовое воздействие (стимул) сигнал для фильтра. Четыре блока Constant обеспечивают коэффициенты фильтра. Блоки Scope используются для симуляции и не используются для генерации HDL-кода.

Перейти к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB®:

Создайте папку под названием sl_hdlcoder_work, например:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели в качестве примера и папок и сгенерированного HDL-кода. Используйте местоположение папки, которое не является в дереве папки MATLAB.

Сделайте sl_hdlcoder_work папка ваша рабочая папка, например:

cd C:\work\sl_hdlcoder_workСохраните локальную копию sfir_fixed модель к вашей текущей рабочей папке. Оставьте модель открытой.

Чтобы сгенерировать HDL-код для DUT, вы используете makehdl функция. Например, чтобы сгенерировать HDL-код для symmetric_fir подсистема, введите:

makehdl('sfir_fixed/symmetric_fir')Чтобы задать индивидуальные настройки, прежде чем вы сгенерируете HDL-код, используйте hdlset_param функция. Можно также задать различные аргументы пары "имя-значение" с makehdl функция, чтобы настроить опции генерации HDL-кода при генерации HDL-кода. Например, чтобы сгенерировать код Verilog, используйте TargetLanguage свойство.

makehdl('sfir_fixed/symmetric_fir', 'TargetLanguage', 'Verilog')

hdlset_param, установите этот параметр на модели и затем запуститесь makehdl функция.hdlset_param('sfir_fixed', 'TargetLanguage', 'Verilog') makehdl('sfir_fixed/symmetric_fir')

HDL Coder™ компилирует модель прежде, чем сгенерировать код. В зависимости от параметров отображения модели, таких как типы данных порта, модель может изменение внешности после генерации кода. В то время как генерация кода продолжает, HDL Coder отображает сообщения о ходе выполнения в командной строке MATLAB с:

Соединитесь с Конфигурацией модели, которая указывает на модель, для которой применяются Параметры конфигурации.

Ссылки на сгенерированные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните по ссылкам.

symmetric_fir.vhd: Код VHDL. Этот файл содержит определение сущности и архитектуру RTL, реализующую symmetric_fir.vhd фильтр.

symmetric_fir_compile.do: Наставник скрипт компиляции Graphics® ModelSim® (vcom команда), чтобы скомпилировать сгенерированный код VHDL.

symmetric_fir_synplify.tcl: Скрипт синтеза Synplify®.

symmetric_fir_map.txt: Этот отчет сопоставляет сгенерированные сущности с подсистемами, которые сгенерировали их. См., что Код Трассировки Использует Файл Отображения

Процесс завершается с сообщением:

### HDL Code Generation Complete.