Используйте область и оптимизацию скорости в HDL Coder™, чтобы сохранить ресурсы и улучшить синхронизацию вашего проекта на целевом устройстве FPGA. Оптимизация не изменяет функциональное поведение вашего алгоритма, но может оптимизировать определенные ресурсы в вашем проекте, ввести задержку или вызвать различие в частотах дискретизации.

Можно первоначально сгенерировать HDL-код и синтезировать проект на платформе FPGA, не включая оптимизацию. Если проект не удовлетворяет требования синхронизации, можно включить оптимизацию и повторно выполнить рабочий процесс, пока проект не соответствует требования к скорости и область. Смотрите Основной Рабочий процесс генерации HDL-кода.

Чтобы включить оптимизацию на вашем коде MATLAB®, откройте Советника по вопросам Рабочего процесса из MATLAB. В Советнике, на задаче HDL Code Generation, включают настройки во вкладке Optimization.

Можно включить оптимизацию на уровне модели и на блочном уровне. Задайте оптимизацию уровня модели:

В диалоговом окне Configuration Parameters, на HDL Code Generation> панель Optimization. Смотрите Панель генерации HDL-кода: Оптимизация.

В командной строке при помощи makehdl или hdlset_param функционируйте, чтобы установить значение свойства.

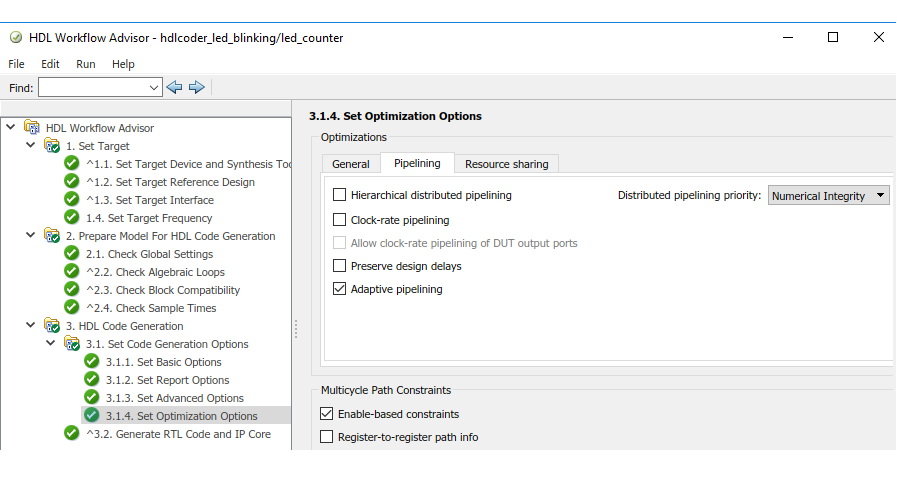

В Simulink® HDL Workflow Advisor, на Set Code Generation Options> задача Set Optimization Options.

Подсистемы в вашей модели наследовали настройки оптимизации уровня модели. Можно изменить настройки уровня подсистемы в диалоговом окне HDL Block Properties для подсистем или при помощи hdlset_param функция. Можно также задать определенные дополнительные настройки для определенных блоков в модели, таких как добавление конвейеров при вводе и выводе. Эта таблица иллюстрирует различную оптимизацию, которая доступна на блочном уровне и уровне модели.

| Оптимизация | Уровень модели? | Уровень подсистемы? | Комментарии |

|---|---|---|---|

| Задержите балансировку | Да | Да | – |

| Отображение RAM | Да | Нет | – |

| Адаптивная конвейеризация | Да | Да | – |

| Конвейеризация тактовой частоты | Да | Да | – |

| Распределенная конвейеризация | Да | Да | На уровне модели вы используете иерархическую распределенную конвейеризацию. Чтобы применить оптимизацию через иерархии подсистемы, включите распределенную конвейеризацию на каждом уровне подсистемы. |

| Разделение ресурсов | Да | Да | На уровне модели вы задаете тип ресурсов, которые вы хотите совместно использовать, такие как сумматоры и множители. На блочном уровне вы задаете SharingFactor. |

| Потоковая передача | Нет | Да | – |

Видеть эффект оптимизации:

Можно сгенерировать отчет оптимизации с HDL-кодом. Чтобы изучить, как включить этот отчет, смотрите, Создают и Отчеты Генерации кода Использования.

Откройте сгенерированную модель или сгенерируйте модель валидации. Сгенерированная модель является поведенческой моделью HDL-кода, который показывает эффект реализаций блока и оптимизации, что вы включили. Чтобы проверить численные данные сгенерированной модели с исходной моделью, можно сгенерировать модель валидации. См. Сгенерированную Модель Модели и Валидации.

Совет

Чтобы эффективно использовать оптимизацию, измените настройки шага расчета для блоков Constant из Inf к -1.

Ваша модель может иметь задержки проекта и конвейерно обработать задержки. Design delays является задержками, которые вы вручную добавляете в свою модель. Pipeline delays является задержками, которые введены путем конвейеризации настроек, заданных на блоках, реализации блока, такие как метод Ньютона-Raphson, нативные операторы с плавающей точкой или оптимизация скорости. Вы видите эти задержки сгенерированного HDL-кода, сгенерированной модели и модели валидации.

Общие параметры оптимизации включают:

Отображение RAM: используйте параметры отображения RAM, чтобы сопоставить большие задержки, персистентные переменные в коде MATLAB и конвейерные задержки с RAM на основе пороговой ширины бита. См. также Отображение RAM для кода MATLAB и Параметров Отображения RAM.

Балансировка задержки: Enabled по умолчанию, эта оптимизация балансирует конвейерные задержки путем вставки соответствия с задержками параллельных путей. Оптимизация совпадает с численными данными сгенерированной модели с исходной моделью. Вы видите эффект этой оптимизации в разделе Delay Balancing отчета оптимизации. Смотрите, что Задержка Балансируется.

Оптимизация скорости улучшает синхронизацию вашего проекта на целевом FPGA путем оптимизации критического пути. Чтобы идентифицировать критический путь, можно запустить Generic ASIC/FPGA рабочий процесс для вашего устройства FPGA и затем аннотирует критический путь или использует отчеты синхронизации.

Чтобы идентифицировать критический путь более быстро и ускорить итеративный процесс нахождения и оптимизации критического пути, используйте оценку критического пути. Вы не должны запускать синтез или генерировать HDL-код. Оценка критического пути использует статический анализ синхронизации с синхронизацией данных из целевых баз данных синхронизации. Вы видите эффект этой оптимизации в разделе Critical Path Estimation отчета оптимизации. Смотрите Оценку Критического пути, Не Запуская Синтез.

Оптимизация скорости включает:

Clock rate pipelining: оптимизация Simulink, которая включена по умолчанию и запускает конвейерные регистры на более быстрой тактовой частоте, когда вы задаете Oversampling factor, больше, чем один. Используйте конвейеризацию тактовой частоты с иерархией, сглаживающейся, чтобы удалить иерархические контуры в подсистеме, таким образом, улучшая повторную синхронизацию. Смотрите, что Тактовая частота Конвейерно обрабатывает.

Distributed pipelining: оптимизация, которая повторно синхронизирует регистры, которые являются существующими задержками, или заданный при помощи настроек блока InputPipeline и OutputPipeline. Чтобы сохранить существующие задержки, включите установку задержек проекта Заповедника. Включите иерархическую распределенную конвейеризацию на модели и распределенную конвейеризацию на подсистемах для повторной синхронизации регистров через иерархии. Вы видите эффект этой оптимизации в разделе Distributed Pipelining отчета оптимизации. Смотрите Распределенную Конвейеризацию и Иерархическую Распределенную Конвейеризацию.

Adaptive pipelining: оптимизация Simulink, которая вставляет конвейерные регистры при вводе или выводе или обоих портах определенных блоков, чтобы создать шаблоны, которые эффективно сопоставляют блоки с модулями DSP на целевом устройстве FPGA. Оптимизация рассматривает целевое устройство, целевую частоту, размеры слова множителя и настройки HDL Block Property. Вы видите эффект этой оптимизации в разделе Adaptive Pipelining отчета оптимизации. Смотрите Адаптивную Конвейеризацию.

Loop Unrolling: оптимизация MATLAB, которая разворачивает цикл путем инстанцирования нескольких экземпляров тела цикла в сгенерированном коде. Можно также частично развернуть цикл. Смотрите Оптимизируют Циклы MATLAB

Оптимизация области уменьшает использование ресурсов вашего проекта. Оптимизация вашего проекта для области может уменьшить скорость, на которой ваш проект работает на FPGA.

Оптимизация области включает:

Resource Sharing: оптимизация, которая идентифицирует несколько функционально эквивалентных ресурсов и заменяет их на один ресурс. На уровне модели вы задаете ресурсы, которые вы хотите совместно использовать, такие как сумматоры и множители. На уровне подсистемы вы задаете SharingFactor в зависимости от количества общих ресурсов в вашем проекте. При помощи оптимизации с конвейеризацией тактовой частоты можно задать, как разогнать совместно используемые ресурсы. Смотрите Разделение ресурсов

Streaming: оптимизация Simulink, которая разделяет векторный информационный канал к нескольким меньшим векторным информационным каналам на основе StreamingFactor, который вы задаете на подсистемах, таким образом, уменьшая потребление аппаратных ресурсов. Смотрите Потоковую передачу.

Loop Streaming: оптимизация MATLAB, которая передает цикл потоком путем инстанцирования тела цикла однажды и использования того экземпляра для каждой итерации цикла. Генератор кода сверхдискретизировал экземпляр тела цикла, чтобы сохранить сгенерированный цикл функционально эквивалентным исходному циклу. Смотрите Оптимизируют Циклы MATLAB