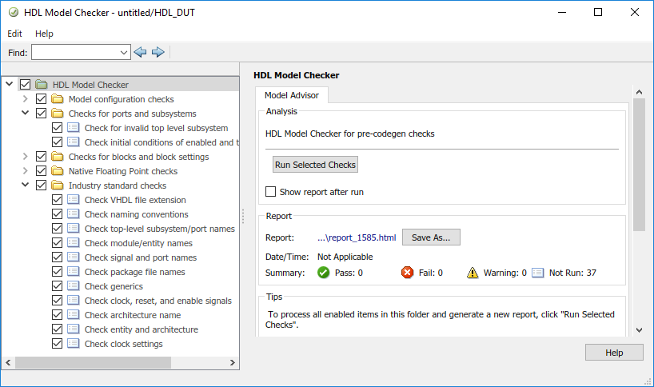

Советник по вопросам HDL-кода и Model Advisor регистрируются в HDL Coder™, проверяют и обновляют вашу модель Simulink® или подсистему для совместимости с генерацией HDL-кода. У Советника Кода есть проверки на:

Настройки конфигурации модели

Настройки Ports и Subsystem

Блоки и настройки блока

Нативная поддержка С плавающей точкой

Инструкции по промышленному стандарту

Когда вы осуществляете проверку, Советник Кода отображает результат как передачу или отказ. Можно зафиксировать предупреждения или отказы при помощи Model Advisor, рекомендуемого настройки.

Используйте регистрации этой папки, чтобы подготовить вашу модель к совместимости с генерацией HDL-кода. Эта папка содержит проверки, которые проверяют, совместимы ли параметры модели с HDL, содержит ли ваш проект алгебраические циклы и так далее.

| Проверяйте имя | Описание |

|---|---|

Проверяйте на параметры модели, которым удовлетворяют для генерации HDL-кода | Проверяйте на параметры модели, настроенные для генерации HDL-кода. |

| Проверяйте модель на внешние символы | Ищите модель неразрешенные ссылки библиотеки, где заданный библиотечный блок не может быть найден. |

| Проверяйте на глобальную установку сброса для устройств Xilinx и Altera | Проверяйте асинхронную установку сброса на устройства Altera® и синхронную установку сброса для устройств Xilinx®. |

| Проверяйте встроенную установку настроек | Проверяйте, есть ли у вас InlineConfigurations активированный. |

| Проверяйте алгебраические циклы | Проверяйте модель на алгебраические циклы. |

| Проверяйте на настройки визуализации | Проверяйте модель на настройки отображения: типы данных порта и расцветка шага расчета. |

| Проверяйте установку балансировки задержки | Проверяйте, что Задержки Баланса включены. |

Примечание

Если вы используете Model Advisor, вы видите модель Check для внешних символов в папке Simulink.

Эта папка содержит проверки, которые проверяют, имеют ли порты и подсистемы в вашей модели настройки, которые совместимы для генерации HDL-кода. Проверки включают, есть ли у вас допустимая Подсистема DUT верхнего уровня и задали ли вы начальное условие для блоков Triggered Subsystem и Enabled Subsystem.

| Проверяйте имя | Описание |

|---|---|

| Проверяйте на недопустимую подсистему верхнего уровня | Проверяйте на подсистемы, которые не могут быть в верхнем уровне для генерации HDL-кода. |

| Проверяйте начальные условия Enabled и Triggered подсистем | Проверяйте на начальное условие Enabled и Triggered подсистем. |

Эти проверки проверяют, поддерживаются ли блоки в вашей модели для генерации HDL-кода, и имеют ли поддерживаемые блоки совместимые с HDL настройки. Проверки включают, имеют ли исходные блоки в вашей модели время непрерывной выборки и имеют ли Графики Stateflow® и блоки MATLAB Function совместимые с HDL настройки и так далее.

| Проверяйте имя | Описание |

|---|---|

| Проверяйте на источники времени бесконечной и непрерывной выборки | Проверяйте исходные блоки со временем непрерывной выборки. |

| Проверяйте на неподдерживаемые блоки | Проверяйте на неподдерживаемые блоки для генерации HDL-кода. |

| Проверяйте на большие операции над матрицей | Проверяйте на большие операции над матрицей. |

| Идентифицируйте несвязанные линии, входные порты и выходные порты | Проверяйте на несвязанные линии или порты. |

| Идентифицируйте отключенные ссылки библиотеки | Поисковая модель для отключенных ссылок библиотеки. |

| Идентифицируйте неразрешенные ссылки библиотеки | Ищите модель неразрешенные ссылки библиотеки, где заданный библиотечный блок не может быть найден. |

| Проверяйте на настройки блока MATLAB function | Проверяйте HDL совместимые настройки на блоки MATLAB Function. |

| Проверяйте на настройки диаграммы Stateflow | Проверяйте HDL совместимые настройки на Stateflow блоки Chart. |

| Проверяйте, что Задержка, Unit Delay и Нулевой Порядок Содержат блоки для перехода уровня | Идентифицируйте Delay, Unit Delay или блоки Zero-Order Hold, которые используются для перехода уровня. Замените эти блоки на фактические блоки Перехода Уровня. |

| Проверяйте на блоки, которые имеют ненулевую выходную задержку | Проверяйте на блоки, которые имеют ненулевую выходную задержку с фиксированной точкой и нативной плавающей точкой. |

| Проверяйте на неподдерживаемый класс памяти для объектов сигнала | Проверяйте, является ли классом хранения объектов сигнала 'ExportedGlobal' или 'ImportedExtern' или 'ImportedExternPointer' |

Примечание

Если вы используете Model Advisor, вы видите Идентифицирование несвязанных линий, входных портов, и выходных портов, Идентифицируете отключенные ссылки библиотеки, Идентифицируете неразрешенные ссылки библиотеки, и Задержка Проверки, Unit Delay и Нулевой Порядок Содержат блоки для перехода уровня в папке Simulink.

Эти проверки проверяют, совместима ли модель для генерации HDL-кода в Native Floating Point режим. Проверки включают, поддерживаются ли блоки в вашей модели Simulink для генерации HDL-кода с Native Floating Point, и ли модель использует один типы данных и так далее. Нативная поддержка с плавающей точкой в HDL Coder генерирует независимый от цели HDL-код из вашей модели с плавающей точкой с одинарной точностью. Для получения дополнительной информации смотрите, Генерируют Независимый от цели HDL-код с Собственным компонентом, С плавающей точкой.

| Проверяйте имя | Описание |

|---|---|

| Проверяйте на один типы данных в модели | Проверяйте на single типы данных в модели. |

| Проверяйте на двойные типы данных в модели с Нативной Плавающей точкой | Проверяйте на double типы данных в модели. |

| Проверяйте на блоки Преобразования типа данных с несовместимыми настройками | Проверяйте режим преобразования блоков Преобразования типа данных. |

| Проверяйте на использование блока HDL Reciprocal | Проверяйте, что блоки HDL Reciprocal не используют типы с плавающей точкой. |

| Проверяйте на использование блока Relational Operator | Проверяйте блоки Relational Operator, которые используют типы с плавающей точкой, имеют булевы выходные параметры. |

| Проверяйте на неподдерживаемые блоки с Нативной Плавающей точкой | Проверяйте на неподдерживаемые блоки с собственным компонентом, с плавающей точкой. |

| Проверяйте блоки с ненулевой ulp ошибкой | Проверяйте на блоки, которые имеют ненулевую ulp ошибку с собственным компонентом, с плавающей точкой. |

Эти проверки проверяют, соответствует ли ваша модель Simulink правилам промышленного стандарта. правила промышленного стандарта рекомендуют использовать определенные инструкции по кодированию HDL. При генерации кода HDL Coder отображает HDL, кодирующий стандартный отчет, который показывает, как хорошо сгенерированный код придерживается инструкций промышленного стандарта.

| Проверяйте имя | Описание |

|---|---|

| Проверяйте расширение файла VHDL | Проверяйте расширения файла файлов VHDL, содержащих сущности. |

| Проверяйте соглашения о присвоении имен | Проверяйте стандартные ключевые слова, используемые инструментами EDA. |

| Проверяйте имена подсистемы/порта верхнего уровня | Проверяйте модуль/сущность верхнего уровня и имена порта. |

| Проверяйте имена модуля/сущности | Проверяйте имена модуля/сущности. |

| Проверяйте имена порта и сигнал | Проверяйте сигнал и длины имени порта. |

| Проверяйте имена файлов пакета | Проверяйте имя файла, содержащее пакеты. |

| Проверяйте дженерики | Проверяйте дженерики в подсистеме верхнего уровня. |

| Проверяйте часы, сбросьте и включите сигналы | Проверяйте соглашение о присвоении имен на часы, сбросьте и включите сигналы. |

| Проверяйте имя архитектуры | Проверяйте имя архитектуры VHDL в сгенерированный HDL-код. |

| Проверяйте сущность и архитектуру | Проверяйте, описаны ли сущность VHDL и архитектура в том же файле. |

| Проверяйте установки часов | Проверочные ограничения на сигналы часов. |

Для получения дополнительной информации см.: