Используя Новый мастер Совета FPGA, можно ввести всю запрошенную информацию, чтобы добавить плату в список плат FPGA. Этот список применяется и к FIL и к рабочим процессам Под ключ. Рассмотрите Требования Совета FPGA прежде, чем добавить плату FPGA, чтобы убедиться, что это совместимо с рабочим процессом, для которого вы хотите использовать его.

Несколько кнопок в Новом мастере Совета FPGA помогают с навигацией:

Back: Перейдите к предыдущей странице, чтобы рассмотреть или отредактировать данные, уже введенные.

Next: Перейдите к следующей странице, когда всем требованиям текущей страницы удовлетворят.

Справка: Открытый Центр Документа и отображение эта тема.

Отмена: Выйдите из Нового мастера Совета FPGA. Можно выйти с или не сохраняя информацию от сеанса.

Добавление Советов однажды для многого пользователя

Чтобы добавить новые платы глобально, следуйте этим инструкциям. Чтобы получить доступ к плате, добавленной глобально, все пользователи должны использовать ту же установку MATLAB®.

Создайте следующую папку:

matlabroot/toolbox/shared/eda/board/boardfiles

Скопируйте XML-файл описания плат в boardfiles папка.

После копирования XML-файла перезапустите MATLAB. Новая плата появляется в списке плат FPGA или для или для и FIL и рабочие процессы Под ключ.

Все платы под этим разоблачением папки в списке плат FPGA автоматически для пользователей с той же установкой MATLAB. Вы не должны использовать менеджера Совета FPGA, чтобы добавить эти платы снова.

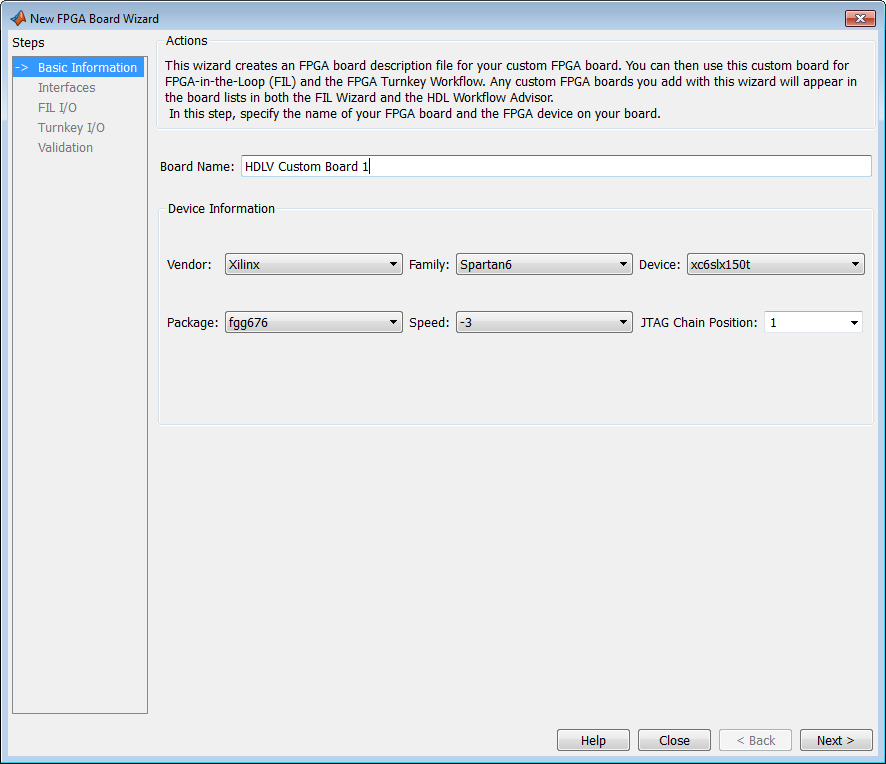

Рабочий процесс для добавления платы FPGA содержит эти шаги:

Board Name: Введите уникальное имя платы.

Device Information:

Vendor: Xilinx или Altera

Family: Семейство зависит от заданного поставщика. Смотрите файл спецификации платы для применимых настроек.

Device: Используйте файл спецификации платы, чтобы выбрать правильное устройство.

Для плат Xilinx® только:

Package: Используйте файл спецификации платы, чтобы выбрать правильный пакет.

Speed: Используйте файл спецификации платы, чтобы выбрать правильную скорость.

JTAG Chain Position: Значение указывает на стартовую позицию для цепи JTAG. Консультируйтесь с файлом спецификации платы для этой информации.

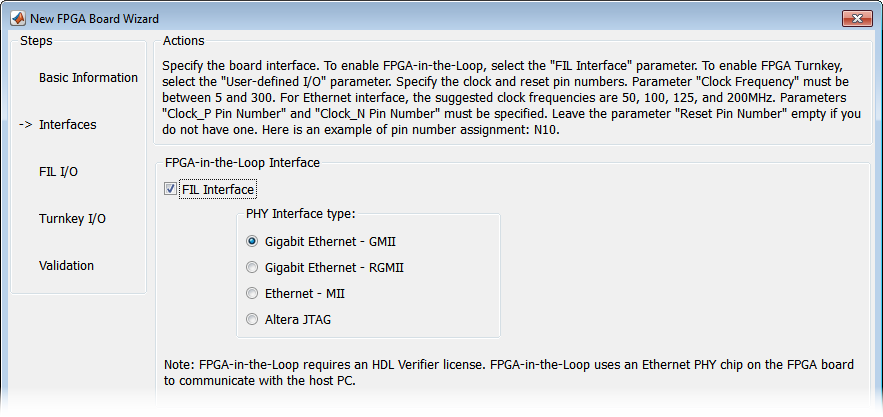

FPGA-in-the-Loop: Чтобы использовать эту плату с FIL, выберите FIL Interface.

Выберите один из следующего PHY Interface type s:

Gigabit Ethernet — GMII

Gigabit Ethernet — RGMII

Gigabit Ethernet — SGMII (опция SGMII появляется, если вы выбираете плату из Stratix® V или семейств устройств IV Stratix),

Ethernet — MII

Altera JTAG (только платы Altera®)

Примечание

Не все интерфейсы доступны для всех плат. Доступность зависит от платы, которую вы выбрали в Основной информации.

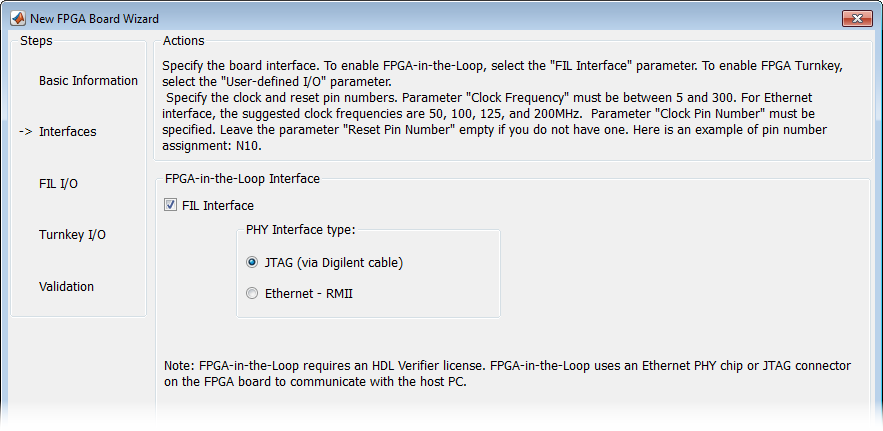

FPGA-in-the-Loop Interface: Чтобы использовать эту плату с FIL, выберите FIL Interface.

Выберите один из следующего PHY Interface type s:

JTAG (via Digilent cable) (только платы Xilinx)

Ethernet — RMII

Примечание

Не все интерфейсы доступны для всех плат. Доступность зависит от платы, которую вы выбрали в Основной информации.

Для получения дополнительной информации о том, как настроить связь JTAG для плат Xilinx, см. JTAG с Setup Кабеля Digilent.

Ограничения. Когда вы симулируете свой проект FPGA через кабель Digilent® JTAG, вы не можете использовать никакую другую функцию отладки, которая требует доступа к JTAG; например, Logic Analyzer Vivado®.

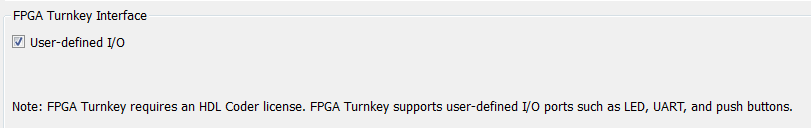

FPGA Turnkey Interface: Если вы хотите использовать с платой с рабочим процессом Тюремщика FPGA HDL Coder™, выберите User-defined I/O.

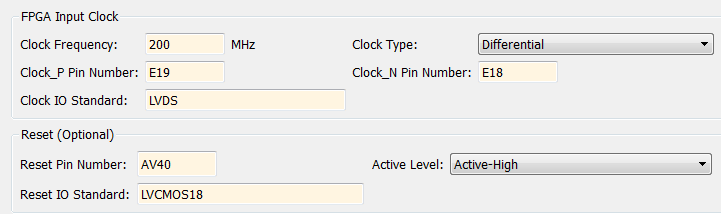

FPGA Input Clock — Детали часов требуются для обоих рабочих процессов. Можно найти всю необходимую информацию в файле спецификации платы.

Clock Frequency — Должен быть от 5 до 300. Для интерфейса Ethernet предложенные тактовые частоты равняются 50, 100, 125, и 200 МГц.

Clock Type — Single_Ended или Differential.

Clock Pin Number (Single_Ended) — Должен быть задан. Пример: N10.

Clock_P Pin Number (Дифференциал) — Должен быть задан. Пример: E19.

Clock_N Pin Number (Дифференциал) — Должен быть задан. Пример: E18.

Clock IO Standard — Программируемый Стандарт ввода-вывода, чтобы использовать, чтобы сконфигурировать вход, выведите, или двунаправленные порты. Например, LVDS.

Reset (Optional) — Если вы хотите указать на сброс, найдите ПИН-код и активный уровень в файле спецификации платы, и введите ту информацию.

Reset Pin Number — Отпуск, пустой, если у вас нет того.

Active Level — Active-Low или Active-High.

Reset IO Standard — Программируемый Стандарт ввода-вывода, чтобы использовать, чтобы сконфигурировать вход, выведите, или двунаправленные порты. Например, LVCMOS33.

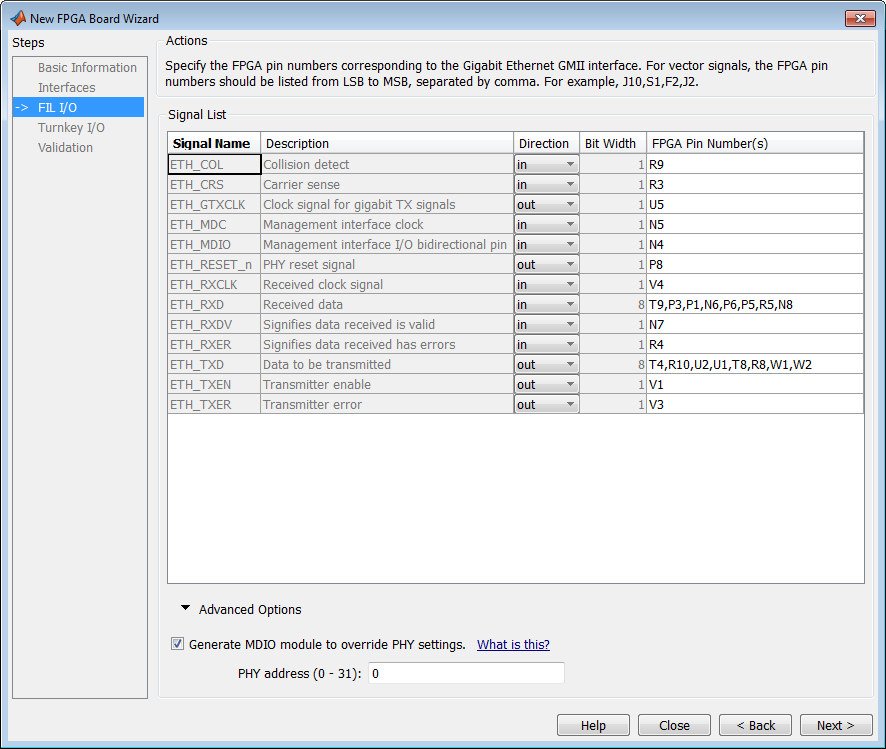

Когда вы выбираете соединение Ethernet со своей платой, необходимо задать контакты для сигналов Ethernet на FPGA.

Signal List: Обеспечьте все ПИН-коды FPGA для заданных сигналов. Можно найти эту информацию в файле спецификации платы. Для векторных сигналов перечислите все ПИН-коды на той же линии, разделенной запятыми.

Примечание

Если ваш чип PHY не имеет дополнительного контакта TX_ER, свяжите ETH_TXER с одним из неиспользованных контактов на FPGA.

Generate MDIO module to override PHY settings: Смотрите следующий раздел по Вводу данных Управления платой FPGA / Выходная шина (MDIO), чтобы определить, когда использовать эту функцию. Если вы действительно выбираете эту опцию, введите адрес PHY.

Примечание

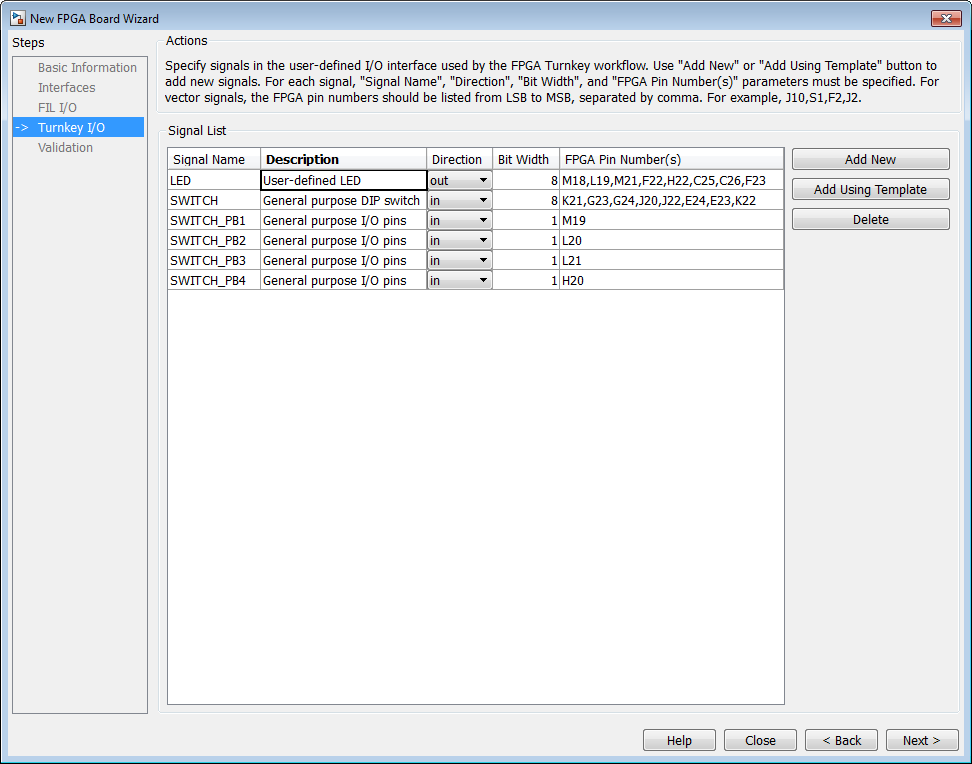

Обеспечьте ввод-вывод FIL для соединения Ethernet только. Задайте по крайней мере один выходной порт для интерфейса Turnkey I/O.

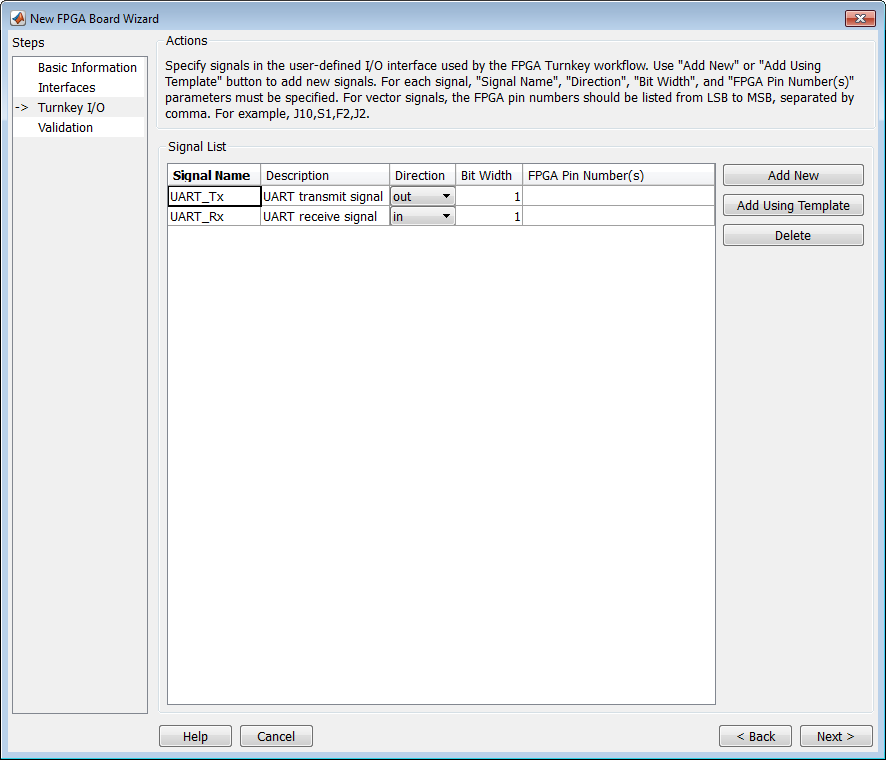

Signal List: Обеспечьте все ПИН-коды FPGA для заданных сигналов. Можно найти эту информацию в файле спецификации платы. Для векторных сигналов перечислите все ПИН-коды на той же линии, разделенной запятыми. Количество ПИН-кодов должно совпадать с битной шириной соответствующего сигнала.

Add New: Вам предлагают ввести все записи в список сигнала вручную.

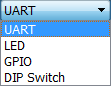

Add Using Template: мастер предварительно заполняет новую запись сигнала для UART, LED, GPIO или сигналов Dip-переключателя со следующим:

Типовое имя сигнала

Описание

Направление

Битная ширина

Можно изменить значения в любом из этих преднаселенных полей.

Удаление: Удалите выбранный сигнал из списка.

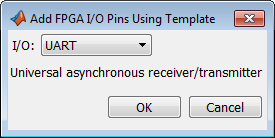

Следующий пример демонстрирует использование функции Add Using Template.

В диалоговом окне Turnkey I/O нажмите Add Using Template.

Можно теперь просмотреть диалоговое окно шаблона.

Выпадающий список вводов-выводов и выбор из следующих опций:

Нажмите OK.

Мастер добавляет заданный сигнал (или сигналы) к списку вводов-выводов.

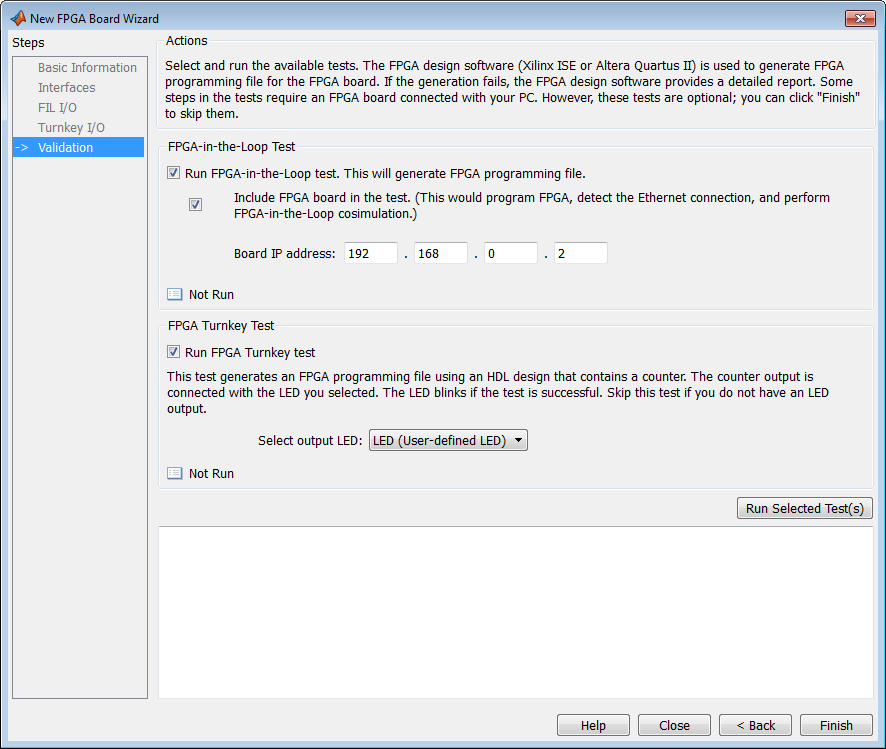

FPGA-in-the-Loop Test

Run FPGA-in-the-Loop test: Выберите, чтобы сгенерировать файл программирования FPGA.

Include FPGA board in the test: (Необязательно) Этот выбор программирует FPGA со сгенерированным файлом программирования, обнаруживает соединение Ethernet (если выбрано) и выполняет FPGA в симуляции цикла.

Board IP address: (только соединение Ethernet) Использование эта опция для установки IP-адреса платы, если это не IP-адрес по умолчанию (192.168.0.2).

При необходимости измените компьютерный IP-адрес в различную подсеть от 192.168.0.x, когда вы настроите сетевой адаптер. Если IP-адрес платы по умолчанию 192.168.0.2 используется другим устройством, измените IP-адрес Совета согласно следующим инструкциям:

Адрес подсети, обычно первые 3 байта IP-адреса платы, должен совпасть с IP-адресом хоста.

Последний байт IP-адреса платы должен отличаться от IP-адреса хоста.

IP-адрес платы не должен конфликтовать с IP-адресами других компьютеров.

Например, если IP-адрес хоста 192.168.8.2, то можно использовать 192.168.8.3 при наличии.

FPGA Turnkey Test

Run FPGA Turnkey test: Выберите, чтобы сгенерировать FPGA, программируя файл с помощью проекта HDL, который содержит счетчик. Необходимо было присоединить плату.

Select output LED: выход счетчика соединяется с LED, который вы выбираете. Пропустите этот тест, если у вас нет LED выходом.

Когда вы завершите валидацию, нажмите Finish. Смотрите Сохранили Файл Определения Совета.