Потоковые данные через канал памяти

SoC Blockset / Память

Потоковые данные о блоке Memory Channel через внешнюю память. Концептуально, это моделирует передачу данных между одним алгоритмом и другим через общую память. Алгоритм может быть аппаратной логикой (HW), модель процессора или устройства ввода-вывода. Алгоритм средства записи запрашивает доступ к памяти от блока Memory Controller. После того, как доступ предоставляется записи алгоритма средства записи к буферу памяти. В модели хранение данных моделируется как буферы в канале. При развертывании на оборудовании данные направляются к внешней общей памяти.

Этот блок может быть сконфигурирован, чтобы поддержать любой из этих протоколов:

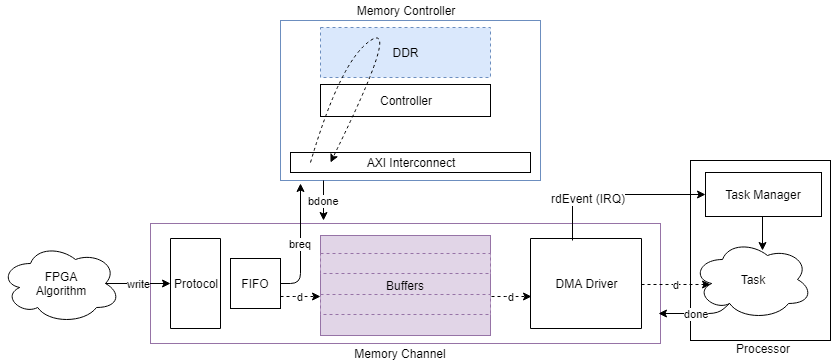

AXI4-Stream to Software via DMA – Смоделируйте связь между аппаратной логикой и программной задачей через внешнюю память. Средство записи помещает данные в канал с помощью упрощенного потокового протокола MathWorks® AXI, и читатель (процессор) получает данные из интерфейса драйвера DMA. Канал моделирует datapath и программный стек той связи включая FIFO, механизм DMA, взаимосвязанную и внешнюю память, прерывания, организацию буферизации данных ядра драйвера DMA и передачи данных к программной задаче. Для получения дополнительной информации об упрощенном потоковом протоколе MathWorks AXI, смотрите AXI4-потоковый Интерфейс.

Это изображение является концептуальным представлением блока Memory Channel, передавая данные потоком от алгоритма FPGA до алгоритма процессора.

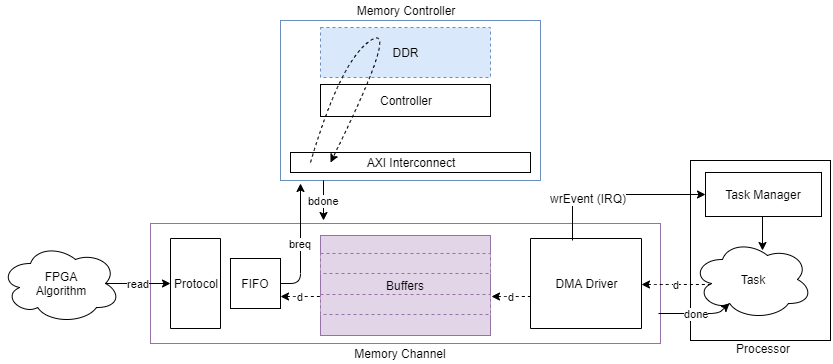

Software to AXI4-Stream via DMA – Смоделируйте связь между аппаратной логикой и программной задачей через внешнюю память. Средство записи (процессор) потоковые данные в канал через драйвер DMA с помощью MathWorks упростило потоковый протокол AXI. Канал моделирует datapath и программный стек той связи включая FIFO, механизм DMA, взаимосвязанную и внешнюю память, прерывания, организацию буферизации данных ядра драйвера DMA и передачи данных от программной задачи. Для получения дополнительной информации об упрощенном потоковом протоколе MathWorks AXI, смотрите AXI4-потоковый Интерфейс.

Это изображение является концептуальным представлением блока Memory Channel, передавая данные потоком от алгоритма процессора до алгоритма FPGA.

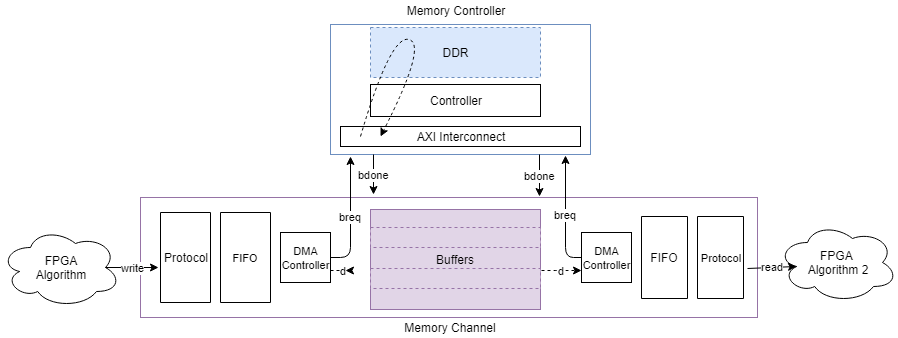

AXI4-Stream FIFO – Смоделируйте связь между двумя алгоритмами FPGA через внешнюю память. Средство записи помещает данные в канал, когда ведущее устройство, использующее MathWorks, упростило потоковый протокол AXI, и читатель получает данные из канала как ведомое устройство с помощью того же протокола. Канал ведет себя как память метода "первым пришел - первым вышел" (FIFO). Канал моделирует datapath связи. Блок Memory Channel включает промежуточный пакетный уровень FIFO, механизм DMA, межсоединение и внешняя память. Сама внешняя память управляема как кольцевой буфер, где буфер должен быть записан, прежде чем он сможет быть считан. Для получения дополнительной информации об упрощенном потоковом протоколе MathWorks AXI, смотрите AXI4-потоковый Интерфейс.

Это изображение является концептуальным представлением блока Memory Channel, передавая данные потоком от одного алгоритма FPGA до другого алгоритма FPGA.

AXI4-Stream Video FIFO – Смоделируйте связь между двумя аппаратными алгоритмами через внешнюю память. Эта структура канала похожа на настройку AXI4 Stream FIFO, но средство записи и читатель используют MathWorks, передающий пиксельный протокол потоком, наряду с сигналом противодавления. Для получения дополнительной информации смотрите AXI4-потоковый Видеоинтерфейс.

AXI4-Stream Video Frame Buffer – Смоделируйте связь между двумя аппаратными алгоритмами через внешнюю память, с помощью полных буферов видеокадра. Протоколом является MathWorks, передающий пиксельный протокол потоком с противодавлением. Кроме того, читатель может гарантировать, что кадровый буфер синхронизируется с нисходящими видео синхронизациями путем утверждения сигнала протокола FSYNC. datapath включает видео DMA (VDMA), механизм и буферы внешней памяти управляемы как кольцевой буфер полных видеокадров. Структура канала идентична структуре типа канала AXI4 Stream FIFO.

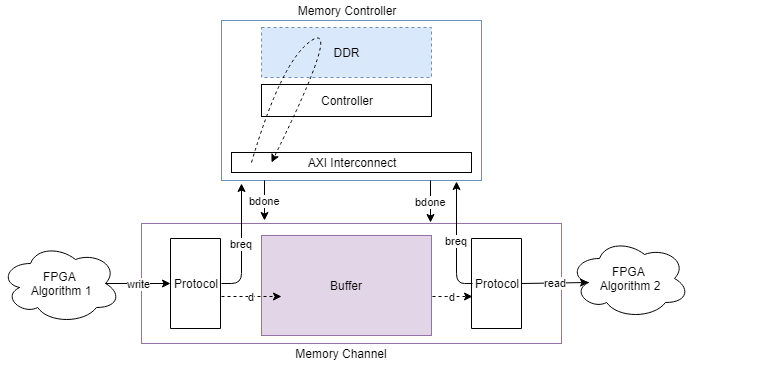

AXI4-Random Access – Смоделируйте связь между двумя аппаратными алгоритмами через внешнюю память, с помощью MathWorks упрощенный AXI4-основной протокол. И средство записи и читатель являются ведущими устройствами, канал является ведомым устройством в обоих случаях. Внешняя память неуправляема (нет никаких логических буферов и никакого кольцевого буфера). Это до читателя и средства записи, чтобы скоординировать синхронизацию на доступах, чтобы гарантировать целостность данных. Для получения дополнительной информации смотрите Упрощенный Основной Интерфейс AXI4.

Это изображение является концептуальным представлением блока Memory Channel с произвольным доступом к памяти для записи и произвольным доступом к памяти для чтения.

Для получения дополнительной информации о доступных протоколах см. Протоколы Канала Внешней памяти.

Interrupt Channel | Memory Controller | Memory Traffic Generator