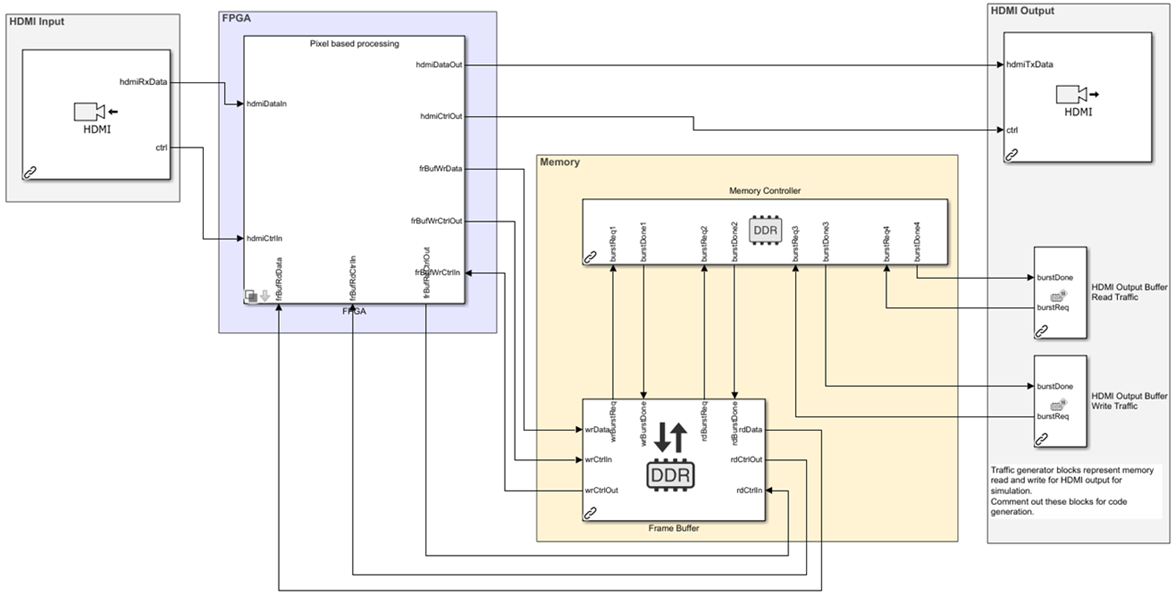

Шаблон Frame Buffer with High-Definition Multimedia Interface (HDMI) создает проект Simulink® с моделями, чтобы симулировать и сгенерировать видео приложение с кадровым буфером внешней памяти. Этот шаблон формирует основу для Эквализации Гистограммы Используя Буферный пример Видеокадра. Используйте этот шаблон, чтобы симулировать полный исходный проект приложения обработки видеоданных на FPGA с вводом-выводом HDMI и связью с кадровым буфером внешней памяти для усовершенствованных проектов обработки изображений.

Vision HDL Toolbox™

Computer Vision Toolbox™

Пакет поддержки SoC Blockset™ для устройств Xilinx®

Видеоданные видеопотоков HDMI от блока HDMI Rx в FPGA. FPGA реализует преобразование цветового пространства и ваш алгоритм обработки изображений. Обработанные изображения затем подвергаются обратному преобразованию цветового пространства и потоку с блоком HDMI Tx. Алгоритм FPGA соединяется с блоком Memory Channel кадрового буфера внешней памяти, сконфигурированным в AXI4-Stream Video Frame Buffer режим.

Из-за аппаратной реализации, HDMI выход требует дополнительного кадрового буфера для синхронизации данных о видеопотоке между областями часов и вводит дополнительного потребителя памяти в полной системе. Можно смоделировать эту систему при помощи блоков Memory Traffic Generator, чтобы симулировать дополнительное потребление памяти. К чтению модели и транзакциям записи, используйте два блока Memory Traffic Generator: один для транзакций чтения и один для транзакций записи. Транзакции записи моделей блока HDMI Output Buffer Write Traffic и модели блока HDMI Output Buffer Read Traffic читают транзакции.

Пиксельная модель FPGA использует блоки Video Stream Connector, чтобы соединить различные подсистемы и соединиться с блоками ввода-вывода HDMI. Это требуется, чтобы смочь сгенерировать каждую подсистему как отдельный IP в реализованном исходном проекте из модели. Поскольку модель системы координат FPGA в целях симуляции только и не используется для реализации, блоки Video Stream Connector не моделируются.

В MATLAB®, на вкладке Project Shortcuts , нажимают Open FPGA pixel model. Дважды кликните, чтобы открыть FPGA Algorithm Wrapper.

![]()

FPGA Algorithm, подсвеченный в зеленом, содержит проходные порты и сигналы.

![]()

Измените содержимое FPGA Algorithm подсистема, чтобы включить ваш желаемый алгоритм обработки видения, с полной симуляцией и генерацией кода окружающей системы видеопамяти. Порты pixelToFrameBuf и pixelFromFrameBuf обеспечивают доступ к каналу внешней памяти, Frame Buffer. Для чистого проекта алгоритма и расследования, во вкладке Project Shortcuts, нажимают Open FPGA frame model и повторяют этот шаг.

Создайте новый проект Используя шаблоны | Используйте шаблон, чтобы создать модель SoC