Демодулируйте модулируемые QPSK данные

PM, в подбиблиотеке Digital Baseband Модуляции

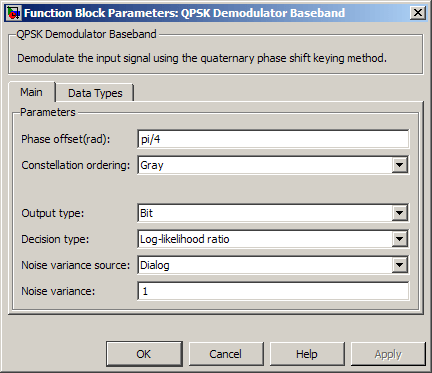

Блок QPSK Demodulator Baseband демодулирует сигнал, который модулировался с помощью квадратурного метода манипулирования сдвига фазы. Вход представляет собой репрезентацию модулированного сигнала.

Вход должен быть комплексным сигналом. Этот блок принимает на вход сигнал в виде вектора - столбца или скалярной величины. Для получения информации о типах данных, которые поддерживает каждый порт блока смотрите Поддерживаемые Типы данных.

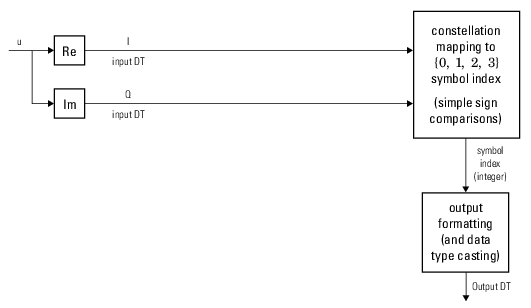

Схема связи Демодулятора QPSK трудного решения для Тривиального Смещения Фазы (нечетное кратное π/4)

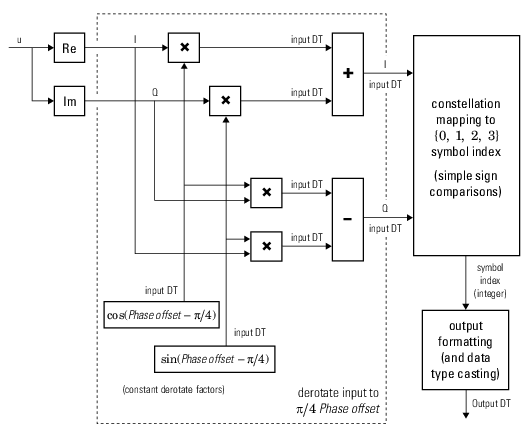

Демодулятор QPSK трудного решения схема связи с плавающей точкой для нетривиального смещения фазы

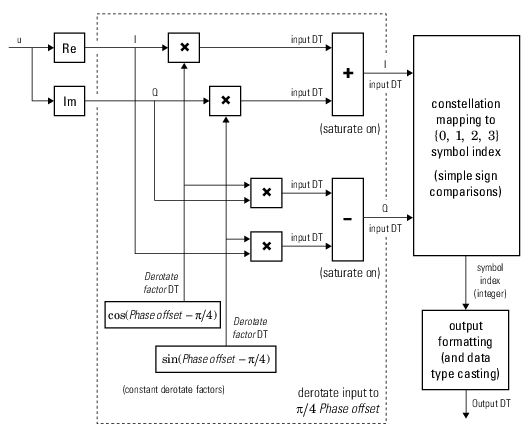

Схема связи фиксированной точки демодулятора QPSK трудного решения для нетривиального смещения фазы

Точный LLR и аппроксимированные случаи LLR (мягкое решение) описаны в Точном Алгоритме LLR и Аппроксимируют Алгоритм LLR.

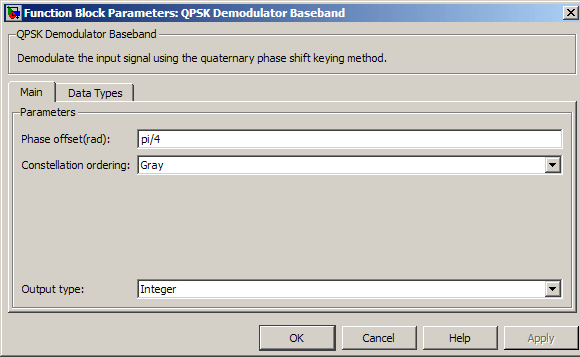

Фаза нулевой точки сигнального созвездия.

Определяет как блок-диаграммы каждое целое число к паре выходных битов.

Определяет, состоит ли выход из целых чисел или битов.

Если параметр Output type устанавливается на Integer и Constellation ordering установлен в Binary, затем блок-диаграммы точка

exp (jθ + jπm/2)

к m, где θ является параметром Phase offset и m, 0, 1, 2, или 3.

Страница с описанием для блока QPSK Modulator Baseband показывает сигнальные созвездия для случаев, когда Constellation ordering установлен в любой Binary или Gray.

Если Output type установлен в Bit, затем выход содержит пары двоичных значений, если Decision type установлен в Hard decision. Старший значащий бит (i.e. крайний левый бит в векторе), первый бит блок выходные параметры.

Если Decision type установлен в Log-likelihood ratio или Approximate log-likelihood ratio, затем выход содержит поразрядный LLR или аппроксимированные значения LLR, соответственно.

Задает использование трудного решения, LLR или аппроксимированного LLR во время демодуляции. Этот параметр появляется, когда вы выбираете Bit от Output type выпадающий список. Выходные значения для отношения Логарифмической правдоподобности и Аппроксимированных типов решения отношения логарифмической правдоподобности имеют совпадающий тип данных как входные значения. Для целочисленного выхода блок всегда выполняет демодуляцию Трудного решения.

См. Точный Алгоритм LLR и Аппроксимируйте Алгоритм LLR для деталей алгоритма.

Это поле появляется когда Approximate log-likelihood ratio или Log-likelihood ratio выбран для Decision type.

Когда установлено в Dialog, шумовое отклонение может быть задано в поле Noise variance. Когда установлено в Port, порт появляется на блоке, через который может быть введено шумовое отклонение.

Этот параметр появляется, когда Noise variance source установлен в Dialog и задает шумовое отклонение во входном сигнале. Этот параметр является настраиваемым в режиме normal mode, Режиме Accelerator и Быстром Режиме Accelerator.

Если вы используете Simulink® Coder™ быстрая симуляция (RSIM) цель, чтобы создать исполняемый файл RSIM, то можно настроить параметр, не перекомпилировав модель. Это полезно для симуляций Монте-Карло, в которых вы запускаете симуляцию многократно (возможно, на нескольких компьютерах) с различными количествами шума.

Алгоритм LLR включает вычислительные экспоненциалы очень больших или очень небольших чисел с помощью конечной арифметики точности и уступил бы:

Inf к -Inf если Noise variance очень высок

NaN если Noise variance и степень сигнала являются оба очень маленькими

В таких случаях используйте аппроксимированный LLR, когда его алгоритм не включает вычислительные экспоненциалы.

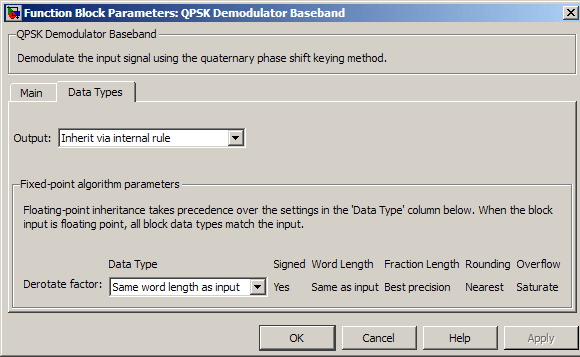

Панель типов данных для трудного решения

Для битных выходных параметров, когда Decision type установлен в Hard decision, тип выходных данных может быть установлен в 'Inherit via internal rule', 'Smallest unsigned integer''double'единственныйint8uint8int16uint16int32uint32, или boolean.

Для целочисленных выходных параметров тип выходных данных может быть установлен в 'Inherit via internal rule', 'Smallest unsigned integer''double'единственныйint8uint8int16uint16int32, или uint32.

Когда этот параметр устанавливается на 'Inherit via internal rule' (настройка по умолчанию), блок наследует тип выходных данных от входного порта. Тип выходных данных совпадет с типом входных данных, если вход будет типом с плавающей точкой (single или double). Если тип входных данных будет фиксированной точкой, тип выходных данных будет работать, как будто этот параметр устанавливается на 'Smallest unsigned integer'.

Когда этот параметр устанавливается на 'Smallest unsigned integer', тип выходных данных выбран на основе настроек, используемых в панели Hardware Implementation диалогового окна Configuration Parameters модели.

Если ASIC/FPGA выбран в панели Hardware Implementation, и Output type является Bit, тип выходных данных является идеальным минимальным однобитным размером, т.е. ufix(1). Для всех других выборов это - беззнаковое целое с самым маленьким доступным размером слова, достаточно большим, чтобы соответствовать одному биту, обычно соответствуя размеру char (например, uint8).

Если ASIC/FPGA выбран в панели Hardware Implementation, и Output type является Integer, тип выходных данных является идеальным минимальным двухбитовым размером, т.е. ufix(2). Для всех других выборов это - беззнаковое целое с самым маленьким доступным размером слова, достаточно большим, чтобы соответствовать двум битам, обычно соответствуя размеру char (например, uint8).

Этот параметр только применяется, когда вход является фиксированной точкой, и Phase offset не является ровным кратным π/4.

Можно выбрать Same word length as input или Specify word length, в этом случае вы задаете размер слова с помощью поля ввода.

Панель типов данных для Мягкого Решения

Для битных выходных параметров, когда Decision type установлен в Log-likelihood ratio или Approximate log-likelihood ratio, тип выходных данных наследован от входа (например, если вход имеет тип данных double, выход имеет также тип данных double).

| Порт | Поддерживаемые типы данных |

|---|---|

Входной параметр |

|

Var |

|

Вывод |

|