Некоторые модели требуют, чтобы вы знали, сколько времени это берет для данных в одном фрагменте модели, чтобы влиять на сигнал в другом фрагменте модели. Например, при конфигурировании калькулятора коэффициента ошибок, необходимо указать на задержку между передатчиком и приемником. Если вы неверно рассчитываете задержка, процессы калькулятора коэффициента ошибок не соответствовали парам данных и следовательно возвращают бессмысленный результат.

Этот раздел иллюстрирует расчет задержек многоскоростных моделей и моделей, где общая задержка последовательности блоков включает несколько задержек от отдельных блоков. Этот раздел также указывает, как использовать Find Delay и блоки Delay, чтобы помочь иметь дело с задержками модели.

Другие части этого набора документации также обсуждают задержки. Для получения информации о контакте с задержками или о задержках определенных типов блоков, смотрите

Страница с описанием блока Find Delay

Страница с описанием блока Delay

Страница с описанием блока Viterbi Decoder

Страница с описанием блока Derepeat

Для обсуждений задержек более простых примеров, чем те в этом разделе смотрите

В то время как некоторые блоки могут определить свое значение текущей производительности с помощью только текущее входное значение, другим блокам нужны входные значения от нескольких временных шагов, чтобы вычислить значение текущей производительности. В последней ситуации блок подвергается задержке. Пример этого случая - когда блок Derepeat должен составить в среднем пять выборок от скалярного сигнала. Блок должен задержать вычисление среднего значения, пока это не получило все пять выборок.

В общем случае задержки вашей силы модели прибывают из различных источников:

Цифровые демодуляторы

Сверточный interleavers или deinterleavers

Эквалайзеры

Блок Viterbi Decoder

Буферизация, субдискретизация, derepeating, и подобные операции сигнала

Явные блоки задержки, такие как Задержка и Переменная Целочисленная Задержка

Фильтры

Следующие обсуждения включают некоторые из этих источников задержки.

Этот раздел исследует пример ADSL С 256 каналами и показывает, как вычислить правильное значение параметров Receive delay в одном из блоков Вычисления Коэффициента ошибок в модели. Модель включает задержки от сверточного перемежения и явного блока задержки. Чтобы открыть модель ADSL в качестве примера, введите commadsl в командной строке MATLAB.

В примере ADSL данные следуют за одним из двух параллельных путей, один с ненулевой задержкой и другим с задержкой нуля. Один путь включает сверточный interleaver и deinterleaver, в то время как другой не делает. Около конца каждого пути блок Error Rate Calculation, параметр Receive delay которого должен отразить задержку данного пути. Остальная часть обсуждения делает наблюдение о периодах системы координат в модели и затем рассматривает путь для чередованных данных.

Перед поиском отдельных задержек сначала заметьте, что большинство сигнальных линий в модели совместно использует тот же период системы координат. На вкладке Debug расширьте Information Overlays. В разделе Sample Time выберите Colors. Эта опция окрашивает блоки и сигналы согласно их периодам системы координат (или периоды расчета, в случае основанных на выборке сигналов). Все сигнальные линии в верхнем уровне модели являются тем же цветом, что означает, что они совместно используют тот же период системы координат. Как следствие системы координат являются удобным модулем для измерения задержек блоков тот процесс эти сигналы. В расчете совокупной задержки вдоль пути взвешенное среднее (количеств систем координат, взвешенных периодом каждой системы координат), уменьшает до суммы.

Во фрагменте передатчика модели чередованный путь является более низкой ветвью, отображенной желтым ниже. Точно так же чередованный путь во фрагменте приемника модели является более низкой ветвью. Около конца чередованного пути блок Error Rate Calculation, который вычисляет значение, пометил Interleaved BER.

Следующая таблица обобщает задержки пути для нечередующихся данных. Следующие абзацы объясняют задержки более подробно и объясняют, почему общая задержка относительно блока Error Rate Calculation является одной системой координат или 776 выборками.

| Блок | Задержитесь в Выходных выборках от отдельного блока | Задержитесь в системах координат | Задержитесь во входных выборках с блоком вычисления коэффициента ошибок |

|---|---|---|---|

| Сверточный Interleaver и Сверточная пара Deinterleaver | 40 | 1 (объединенный) | 776 (объединенный) |

| Задержка | 800 | ||

| Общее количество | Нет данных | 1 | 776 |

Перемежение. В отличие от нечередующегося пути, чередованный путь содержит блок Convolutional Interleaver в передатчике и блок Convolutional Deinterleaver в приемнике. Задержка interleaver/deinterleaver пары является продуктом параметра Rows of shift registers, параметра Register length step и меньше, чем параметр Rows of shift registers. В этом случае задержка interleaver/deinterleaver пары оказывается 5*2*4 = 40 выборок.

Задержите Блок. Фрагмент приемника чередованного пути также содержит блок Delay. Этот блок явным образом вызывает задержку 800 выборок, имеющих тот же шаг расчета как 40 выборок задержки от interleaver/deinterleaver пары. Поэтому общая задержка от перемежения, устранения чередования и явной задержки является 840 выборками. Эти 840 выборок составляют одну систему координат данных, оставляя блок Delay.

Подведение итогов Задержек. Никакие другие блоки в чередованном пути примера не вызывают задержек. Добавление задержек от interleaver/deinterleaver пары и блока Delay указывает, что общая задержка чередованного пути является одной системой координат.

Общая Задержка Относительно Блока Вычисления Коэффициента ошибок. Блок Error Rate Calculation, который вычисляет значение, пометил Interleaved BER требует значения параметров Receive delay, которое эквивалентно одной системе координат. Параметр Receive delay измеряется в выборках, и каждый входной кадр с блоком Error Rate Calculation содержит 776 выборок. Кроме того, частота кадров в выходных портах всех вызывающих задержку блоков в чередованном пути равняется частоте кадров во входе блока Error Rate Calculation. Поэтому правильным значением для параметра Receive delay является 776 выборки.

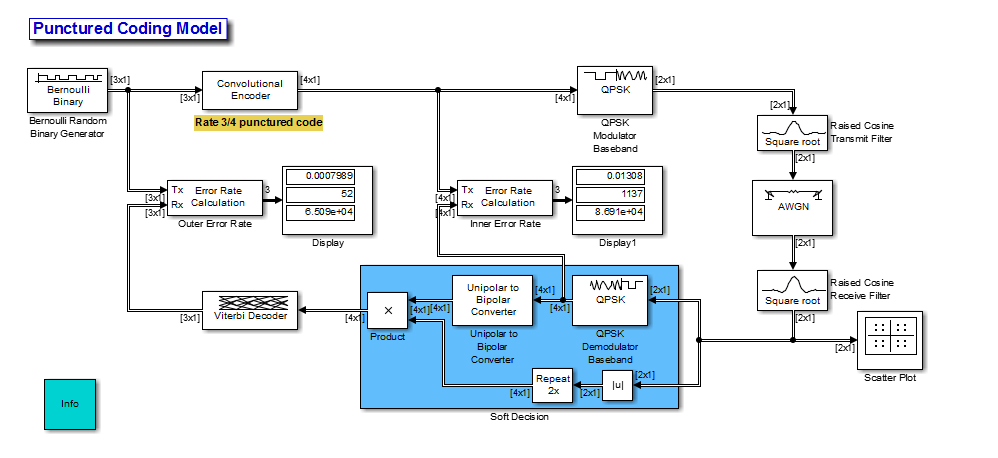

В этом разделе рассматриваются проколотую модель кодирования, которая включает задержки от декодирования, субдискретизации и фильтрации. Два Вычисления Коэффициента ошибок блокируются в работе модели правильно, если и только если их параметры Receive delay точно отражают задержки модели. Чтобы открыть модель, введите doc_punct в командной строке MATLAB.

Перед поиском отдельных задержек, если панель Timing Legend не уже открыта на вкладке Debug, расширяют Information Overlays. В разделе Sample Time выберите Legend. В панели Timing Legend> Highlight> All. Только самый правый фрагмент модели отличается в цвете от остальной части модели. Это означает, что все сигналы и блоки в модели кроме тех в самом правом ребре совместно используют тот же период системы координат. Следовательно, системы координат в этой преобладающей частоте кадров являются удобным модулем для измерения задержек блоков тот процесс эти сигналы. В расчете совокупной задержки вдоль пути взвешенное среднее (количеств систем координат, взвешенных периодом каждой системы координат), уменьшает до суммы.

Желтые блоки представляют многоскоростные системы, в то время как блок AWGN Channel запускается в более высокой частоте кадров, чем все другие блоки в модели.

Блок пометил Inner Error Rate, расположенный около центра модели, копия блока Error Rate Calculation из библиотеки Comm Sinks. Это вычисляет частоту ошибок по битам для фрагмента модели, которая исключает проколотый сверточный код. Во фрагменте модели между двумя входными сигналами этого блока задержки прибывают из Фильтра Tx и Фильтра Rx. Этот раздел объясняет, почему блок Inner Error Rate параметр Receive delay является общим значением задержки 16.

Блок Фильтра Tx. Блок пометил Tx Filter, копия блока Raised Cosine Transmit Filter. Это интерполирует входной сигнал на коэффициент 8 и применяет фильтр приподнятого косинуса квадратного корня. Значение параметра Filter span in symbols блока равняется 6, что означает, что его групповая задержка является 3 символами. Поскольку частота дискретизации этого блока увеличивается от входного порта до выходного порта, это должно вывести начальную систему координат нулей в начале симуляции. Поскольку его размер входного кадра равняется 2, общая задержка блока равняется 2 + 3 = 5 символов. Это соответствует 5 выборкам во входном порту блока.

Блок Фильтра Rx. Блок пометил Rx Filter, копия блока Raised Cosine Receive Filter. Это десятикратно уменьшает свой входной сигнал на коэффициент 8 и применяет другой фильтр приподнятого косинуса квадратного корня. Значение параметра Filter span in symbols этого блока равняется 6, что означает, что его групповая задержка является 3 символами. При выходе блока эти 3 символа соответствуют 3 выборкам.

Блок Демодулятора QPSK. Блок пометил QPSK Demodulator Baseband, получает комплексные сигналы QPSK и выходные параметры 2 бита для каждого комплексного входа. Это преобразование, чтобы вывести биты удваивает совокупную задержку во входе блока.

Подведение итогов Задержек. Никакие другие блоки во фрагменте модели между блоком Inner Error Rate два входных сигнала не вызывают задержек. Общей задержкой является затем (2 + 3 + 3) * 2 = 16 выборки. Это значение может использоваться в качестве параметра Receive Delay в блоке Inner Error Rate.

Блок пометил Outer Error Rate, расположенный слева от модели, копия блока Error Rate Calculation из библиотеки Comm Sinks. Это вычисляет частоту ошибок по битам для целой модели, включая проколотый сверточный код. Задержки прибывают из Фильтра Tx, Фильтра Rx и блоков Декодера Витерби. Этот раздел объясняет, почему блок Outer Error Rate параметр Receive delay является общим значением задержки 108.

Фильтр и Блоки Downsample. Фильтр Tx, Фильтр Rx и блоки Downsample имеют объединенную задержку 16 выборок. Для получения дополнительной информации смотрите Внутренний Блок Коэффициента ошибок.

Блок Декодера Витерби. Поскольку блок Viterbi Decoder декодирует уровень 3/4 проколотый код, это на самом деле уменьшает задержку, замеченную в ее входе. Это сокращение дано как 16 * 3/4 = 12 выборки.

Блок Viterbi Decoder декодирует сверточный код, и использование алгоритма traceback пути вызывает задержку. Блок обрабатывает основанный на системе координат сигнал и установил Operation mode на Continuous. Поэтому задержка, измеренная в выходных выборках, равна значению параметров Traceback depth 96. (Сумма задержки утверждается на странице с описанием для блока Viterbi Decoder.), Поскольку выход блока Viterbi Decoder является точно одними из входных параметров с блоком Outer Error Rate, легче полагать, что задержка 96 выборок, а не преобразует его в эквивалентное количество систем координат.

Общая Задержка Относительно Внешнего Блока Коэффициента ошибок. Блок Outer Error Rate требует значения параметров Receive delay, которое является суммой всех задержек системы. Этой общей задержкой является 12 + 96 = 108 выборки.

Предыдущие обсуждения объяснили, почему определенные блоки Вычисления Коэффициента ошибок в моделях имели определенные значения параметров Receive delay. Вы, возможно, прибыли в те числа независимо при помощи блока Find Delay. Этот раздел объясняет, как найти задержку сигнала с помощью модели ADSL в качестве примера, commadsl, как пример. Применение метода к проколотому сверточному примеру кодирования, обсужденному в Проколотой Модели Кодирования, было бы подобно.

Вспомните из Пути для Чередованных Данных, что задержка пути для чередованных данных является 776 выборками. Чтобы иметь блок Find Delay вычисляют то значение для вас, используют эту процедуру:

Вставьте блок Find Delay и блок Display в модели около блока Error Rate Calculation, который вычисляет значение, пометил Interleaved BER.

Соедините блоки как показано ниже.

Установите блок Find Delay параметр Correlation window length на значение, существенно больше, чем 776, такой как 2 000.

Примечание

Необходимо использовать достаточно большую длину окна корреляции, или иначе значения, произведенные блоком Find Delay, не стабилизировались в правильном значении.

Запустите симуляцию.

Новый блок Display теперь показывает значение 776, как ожидалось.

Задержки и проблемы Выравнивания. Некоторые модели требуют, чтобы вы не только вычислили задержки, но и управляли ими. Например, если модель подвергается задержке между блочным энкодером и его соответствующим декодером, декодер может неправильно истолковать контуры между кодовыми комбинациями, которые это получает и, следовательно, возвратите бессмысленные результаты. В более общем плане такая ситуация может возникнуть, когда путь между парными компонентами блочно-ориентированной операции (такими как перемежение, блочное кодирование или преобразования бита до целого числа) включает вызывающую задержку операцию (такую как перечисленные в Источниках Задержек).

Чтобы избежать этой проблемы, можно вставить дополнительную задержку ассигновать суммы между энкодером и декодером. Если модель также вычисляет коэффициент ошибок, то дополнительная задержка влияет на тот процесс, как описано в Задержках. Этот раздел использует примеры, чтобы проиллюстрировать цель, методы и последствия управления задержками множества обстоятельств.

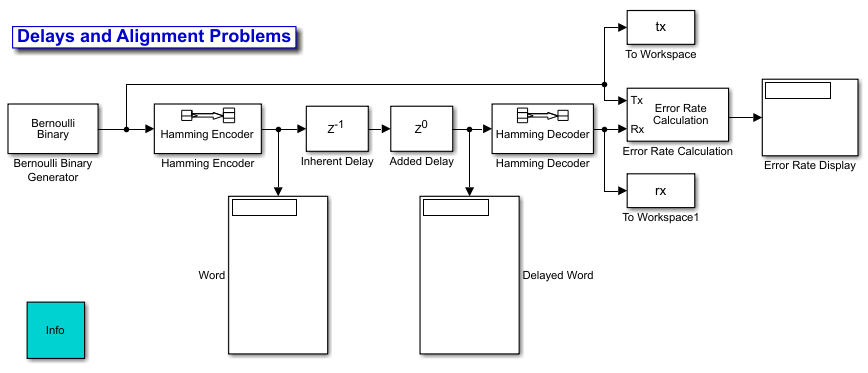

Этот раздел иллюстрирует чувствительность блочно-ориентированных операций к задержкам, с помощью маленькой модели, которая стремится получать сущность проблемы в простой форме. Откройте модель путем ввода doc_alignment в командной строке MATLAB®. Затем запустите симуляцию так, чтобы блоки Отображения показали соответствующие значения.

В этой модели два кодера создают и декодируют блочный код. Две копии блока Delay создают задержку между энкодером и декодером. Два блока Задержки имеют различные цели в этой иллюстративной модели:

Блок Inherent Delay представляет любые вызывающие задержку блоки, которые могут произойти в модели между энкодером и декодером. Смотрите Источники Задержек списка возможностей, которые могут произойти в более реалистической модели.

Блок Added Delay является явной задержкой, которую вы вставляете, чтобы произвести ассигновать сумму в размере общей задержки между энкодером и декодером. Например, commadsl модель содержит блок Delay, который служит этой цели.

Наблюдение проблемы. По умолчанию параметры Delay в Свойственной Задержке и Добавленных блоках Задержки устанавливаются на 1 и 0, соответственно. Это представляет ситуацию, которой некоторая операция вызывает однобитную задержку между энкодером и декодером, но вы еще не попытались компенсировать его. Общая задержка между энкодером и декодером составляет один бит. Вы видите от блоков, пометил Word и Delayed Word, что кодовая комбинация, которая оставляет энкодер, смещена вниз на один бит к тому времени, когда это вводит декодер. Декодер получает сигнал, в котором контур кодовой комбинации на уровне второго бита в системе координат, вместо того, чтобы совпасть с началом системы координат. Таким образом, кодовые комбинации и системы координат, которые содержат их, не выравниваются друг с другом.

Это неприсоединение проблематично, потому что блок Hamming Decoder принимает, что каждая система координат начинает новую кодовую комбинацию. В результате это пытается декодировать слово, которое состоит из последнего бита одной выходной системы координат от энкодера, сопровождаемого на первые шесть битов следующей выходной системы координат от энкодера. Вы видите от блока Error Rate Display, что коэффициент ошибок от этой операции декодирования близко к 1/2. Таким образом, декодер редко восстанавливает исходное сообщение правильно.

Чтобы использовать аналогию, предположите, что кто-то повреждает абзац прозы путем перемещения каждого символа периода от конца предложения в конец первого слова следующего предложения. При попытке считать такой абзац при предположении, что новое предложение начинается после периода вы неправильно понимаете начало и конец каждого предложения. В результате вы можете не изучить значение абзаца.

Чтобы видеть, как задержки различных сумм влияют на эффективность декодера, варьируются значения параметра Delay в блоке Added Delay и параметра Receive delay в блоке Error Rate Calculation и затем запускают симуляцию снова. Много комбинаций значений параметров производят коэффициенты ошибок, которые являются близко к 1/2. Кроме того, если вы исследуете переданные и полученные данные путем ввода

[tx rx]

в командной строке MATLAB вы не можете обнаружить корреляцию между переданными и полученными данными.

Исправление задержек

Некоторые комбинации значений параметров производят коэффициенты ошибок нуля, потому что задержки подходят для системы. Например:

В блоке Added Delay, набор Delay к 6.

В блоке Error Rate Calculation, набор Receive delay к 4.

Запустите симуляцию.

Введите [tx rx] в командной строке MATLAB.

Главный номер в блоке Error Rate Display показывает, что коэффициент ошибок является нулем. Декодер восстановил каждое переданное сообщение правильно. Однако Word и Отображенные блоки Word не показывают совпадающие значения. Это не сразу понятно, как выход энкодера и вход декодера связаны друг с другом. Чтобы разъяснить вопрос, исследуйте выход в окне команды MATLAB. Последовательность вдоль первого столбца (tx) появляется во втором столбце (rx) четыре строки позже. Чтобы подтвердить это, войти

isequal(tx(1:end-4),rx(5:end))

в командной строке MATLAB и замечают, что результатом является 1 TRUE. Эта последняя команда тестирует, совпадает ли первый столбец с переключенной версией второго столбца. Сдвиг вектора MATLAB rx четырьмя строками соответствует поведению блока Error Rate Calculation, когда его параметр Receive delay устанавливается на 4.

Подводя итоги, эти специальные значения Delay и параметров Receive delay работают по этим причинам:

Объединенный, Свойственная Задержка и Добавленные блоки Задержки задерживают кодируемое сообщение полной кодовой комбинацией, а не частичной кодовой комбинацией. Таким образом декодер правилен в своем предположении, что контур кодовой комбинации падает в начале входного кадра и декодирует слова правильно. Однако задержка кодируемого сообщения заставляет каждое восстановленное сообщение появиться одно слово позже, то есть, четыре бита позже.

Блок Error Rate Calculation компенсирует задержку с одним словом системы путем сравнения каждого слова переданного сигнала с данными четыре бита позже в полученном сигнале. Таким образом это правильно приходит к заключению, что коэффициент ошибок декодера является нулем.

Примечание

Это не единственные значения параметров, которые производят коэффициенты ошибок нуля. Поскольку код в этой модели (7, 4), блочный код и свойственное значение задержки равняются 1, можно установить Delay и параметры Receive delay к 7k-1 и 4k, соответственно, для любого положительного целого числа k. Важно, чтобы сумма свойственной задержки (1) и добавленной задержки (7k-1) была кратной длине кодовой комбинации (7).

Выравнивание Слов Блочного кода. Пример ADSL, обсужденный в Модели ADSL В качестве примера, иллюстрирует потребность управлять задержкой модели так, чтобы каждая система координат данных, которые вводят блочный декодер, имела контур кодовой комбинации в начале системы координат. Потребность возникает, потому что путь между блочным энкодером и блочным декодером включает вызывающую задержку сверточную операцию чередования. Этот раздел объясняет, почему модель использует блок Delay, чтобы управлять задержкой между сверточным deinterleaver и блочным декодером, и почему блок Delay сконфигурирован как есть. Чтобы открыть модель ADSL в качестве примера, введите commadsl в командной строке MATLAB.

Неточное совмещение кодовых комбинаций

В примере ADSL Сверточный Interleaver и Сверточные блоки Deinterleaver появляются после подсистем Scrambler & FEC, но перед подсистемами Descrambler & FEC. Эти две подсистемы содержат блоки, которые выполняют кодирование Тростника-Solomon, и кодеры ожидают, что каждая система координат входных данных запустится на новом слове, а не посреди слова.

Как обсуждено в Пути для Чередованных Данных, задержка interleaver/deinterleaver пары является 40 выборками. Однако вход к подсистеме Descrambler & FEC является системой координат размера 840, и 40 не кратное 840. Следовательно, сигнал, который выходит из блока Convolutional Deinterleaver, является системой координат, первая запись которой не представляет начало новой кодовой комбинации. Как описано в Наблюдении проблемы это неточное совмещение, между кодовыми комбинациями и системами координат, которые содержат их, препятствует тому, чтобы декодер декодировал правильно.

Вставка задержки, чтобы откорректировать выравнивание

Пример ADSL решает задачу путем перемещения контура слова от 41-й выборки системы координат с 840 выборками к первой выборке последовательной системы координат. Перемещение контура слова эквивалентно задержанию сигнала. С этой целью пример содержит блок Delay между блоком Convolutional Deinterleaver и подсистемой Descrambler & FEC.

Параметром Delay в блоке Delay является 800 потому что это - минимальное количество выборок, требуемых переключать 41-ю выборку одной системы координат с 840 выборками к первой выборке следующей системы координат с 840 выборками. Другими словами, сумма свойственной задержки с 40 выборками (от процесса перемежения/устранения чередования) и искусственной задержки с 800 выборками является полной системой координат данных, не частичной системой координат.

Эта задержка с 800 выборками имеет последствия для других частей модели, а именно, параметра Receive delay в одном из блоков Вычисления Коэффициента ошибок. Для получения дополнительной информации о том, как задержка влияет на значение того параметра, смотрите Путь для Чередованных Данных.

Используя блок задержки находки

Предыдущее обсуждение объяснило, почему задержка с 800 выборками необходима, чтобы откорректировать неточное совмещение между кодовыми комбинациями и системами координат, которые содержат их. Зная, что подсистема Descrambler & FEC требует, чтобы контуры системы координат произошли на контурах слова, вы, возможно, прибыли в номер 800 независимо при помощи блока Find Delay. Используйте эту процедуру:

Вставьте блок Find Delay и блок Display в модели.

Создайте ответвление, которое соединяет вход блока Convolutional Interleaver к sRef вход блока Find Delay.

Создайте другое ответвление, которое соединяет выход блока Convolutional Deinterleaver к sDel вход блока Find Delay.

Соедините delay выход блока Find Delay с новым блоком Display. Модифицированная часть модели теперь похожа на следующее изображение (который также показывает падающие тени на ключевых блоках, чтобы подчеркнуть модификации).

Покажите размерности каждого сигнала в модели. На вкладке Debug расширьте Information Overlays. В разделе Signals выберите Signal Dimensions.

Запустите симуляцию.

Новый блок Display теперь показывает значение 40. Кроме того, отображение размерностей сигнала показывает, что выход от блока Convolutional Deinterleaver является системой координат длины 840. Эти результаты показывают, что последовательность блоков между Сверточным Interleaver и Сверточным Deinterleaver, включительно, задерживает систему координат с 840 выборками 40 выборками. Дополнительная задержка 800 выборок приносит общую задержку с 840. Поскольку общая задержка является теперь кратным длине системы координат, задержанные устраненные чередование данные могут декодироваться.

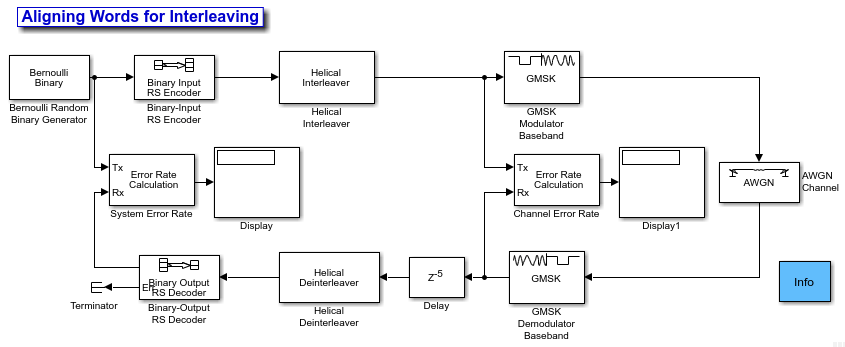

Выравнивание Слов для Перемежения. В этом разделе описываются пример, который управляет задержкой перед deinterleaver, потому что путь между interleaver и deinterleaver включает задержку от демодуляции. Чтобы открыть модель, введите doc_gmskint в командной строке MATLAB.

Модель включает блочное кодирование, спиральное перемежение и модуляцию GMSK. Приведенная ниже таблица обобщает отдельные задержки блока модели.

| Блок | Задержитесь в Выходных выборках от отдельного блока | Ссылка |

|---|---|---|

| Основная полоса демодулятора GMSK | 16 | Задержки цифровой модуляции |

| Спиральный Deinterleaver | 42 | Задержки сверточного Interleavers |

| Задержка | 5 | Страница с описанием Delay |

Неточное совмещение чередованных слов

Процесс демодуляции в этой модели вызывает задержку между interleaver и deinterleaver. Поскольку deinterleaver ожидает, что каждая система координат входных данных запустится на новом слове, важно гарантировать, что общая задержка между interleaver и deinterleaver включает одну или несколько полных систем координат, но никакие частичные системы координат.

Задержка демодулятора является 16 выходными выборками. Однако вход с блоком Helical Deinterleaver является системой координат размера 21, и 16 не кратное 21. Следовательно, сигнал, который выходит из блока GMSK Demodulator Baseband, является системой координат, первая запись которой не представляет начало нового слова. Как описано в Наблюдении проблемы это неточное совмещение между словами и системами координат, которые содержат их, препятствует deinterleaver.

Вставка задержки, чтобы откорректировать выравнивание

Модель перемещает контур слова от 17-й выборки системы координат с 21 выборкой к первой выборке следующей системы координат. Перемещение контура слова эквивалентно задержанию сигнала пятью выборками. Блок Delay между блоком GMSK Demodulator Baseband и блоком Helical Deinterleaver выполняет такую задержку. Блок Delay имеет свой набор параметров Delay к 5.

Комбинирование эффектов демодулятора и блока Delay, общей задержки между interleaver и deinterleaver является полной системой координат с 21 выборкой данных, не частичной системой координат.

Проверка выравнивания кодовых комбинаций блока

interleaver и deinterleaver вызывают объединенную задержку 42 выборок, измеренных при выходе от блока Helical Deinterleaver. Поскольку задержанный выход от deinterleaver идет рядом с декодером кода Рида-Соломона, и потому что декодер ожидает, что каждая система координат входных данных запустится на новом слове, важно гарантировать, что общая задержка между энкодером и декодером включает одну или несколько полных систем координат, но никакие частичные системы координат.

В этом случае задержка с 42 выборками является точно двумя системами координат. Поэтому не необходимо вставить блок Delay между блоком Helical Deinterleaver и блоком Binary-Output RS Decoder.

Вычисление задержек, чтобы сконфигурировать блоки вычисления коэффициента ошибок

Модель содержит два блока Вычисления Коэффициента ошибок, пометил Channel Error Rate и System Error Rate. Каждый из этих блоков имеет параметр Receive delay, который должен отразить задержку пути между Tx блока и Rx сигналы. Следующая таблица объясняет значения Receive delay в двух блоках.

| Блок | Получите значение задержки | Причина |

|---|---|---|

| Коэффициент ошибок канала | 16 | Задержка блока GMSK Demodulator Baseband, в выборках |

| Уровень системной ошибки | 15*3 | Три системы координат с пятнадцатью выборками: одна система координат от блоков Основной полосы и Задержки Демодулятора GMSK и две системы координат от interleaver/deinterleaver пары |

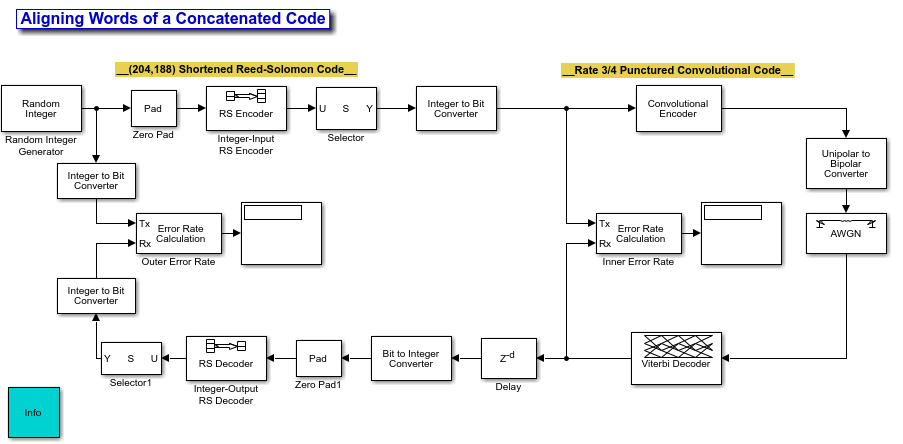

Выравнивание Слов Каскадного кода. В этом разделе описываются пример, который управляет задержкой между двумя фрагментами декодера каскадного кода, потому что первый фрагмент включает задержку от декодирования Viterbi, в то время как второй фрагмент ожидает, что контуры системы координат совпадут с контурами слова. Чтобы открыть модель, введите doc_concat в командной строке MATLAB. Это использует блочные и сверточные коды от commdvbt пример, но упрощает общий замысел много.

Модель включает сокращенный блочный код и проколотый сверточный код. Все сигналы и блоки в модели совместно используют тот же период системы координат. Следующая таблица обобщает отдельные задержки блока модели.

| Блок | Задержитесь в Выходных выборках от отдельного блока |

|---|---|

| Viterbi Decoder | 136 |

| Delay | 1496 (то есть, 1632 - 136) |

Неточное совмещение кодовых комбинаций блока

Viterbi декодирование процесса в этой модели вызывает задержку между блоком Integer to Bit Converter и блоком Bit to Integer Converter. Поскольку последний блок ожидает, что каждая система координат входных данных запустится на новом 8-битном слове, важно гарантировать, что общая задержка между двумя блоками конвертера включает одну или несколько полных систем координат, но никакие частичные системы координат.

Задержка блока Viterbi Decoder является 136 выходными выборками. Однако вход с блоком Bit to Integer Converter является системой координат размера 1632. Следовательно, сигнал, который выходит из блока Viterbi Decoder, является системой координат, первая запись которой не представляет начало нового слова. Как описано в Наблюдении проблемы это неточное совмещение между словами и системами координат, которые содержат их, препятствует блоку конвертера.

Примечание

Внешний декодер в этой модели (Выведенный целым числом Декодер RS) также ожидает, что каждая система координат входных данных запустится на новой кодовой комбинации. Поэтому проблема неточного совмещения в этой модели влияет на многие проекты каскадного кода, не только тех, которые преобразуют между сигналами с целочисленным знаком и с бинарным знаком.

Вставка задержки, чтобы откорректировать выравнивание

Модель перемещает контур слова от 137-й выборки системы координат с 1632 выборками к первой выборке следующей системы координат. Перемещение контура слова эквивалентно задержанию сигнала 1632-136 выборками. Блок Delay между блоком Viterbi Decoder и блоком Bit to Integer Converter выполняет такую задержку. Блок Delay имеет свой набор параметров Delay к 1496.

Комбинирование эффектов блока Viterbi Decoder и блока Delay, общей задержки между interleaver и deinterleaver является полной системой координат с 1632 выборками данных, не частичной системой координат.

Вычисление задержек, чтобы сконфигурировать блоки вычисления коэффициента ошибок

Модель содержит два блока Вычисления Коэффициента ошибок, пометил Inner Error Rate и Outer Error Rate. Каждый из этих блоков имеет параметр Receive delay, который должен отразить задержку пути между Tx блока и Rx сигналы. Приведенная ниже таблица объясняет значения Receive delay в двух блоках.

| Блок | Получите значение задержки | Причина |

|---|---|---|

| Внутренний коэффициент ошибок | 136 | Задержка блока Viterbi Decoder, в выборках |

| Внешний коэффициент ошибок | 1504 (188*8 bits) | Одна система координат с 188 выборками, от комбинации свойственной задержки блока Viterbi Decoder и добавленной задержки блока Delay |

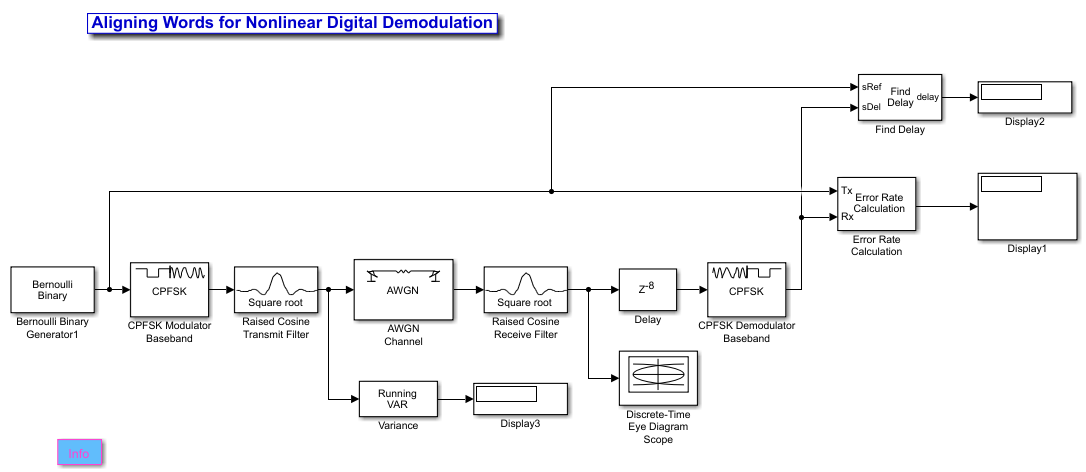

Выравнивание Слов для Нелинейной Цифровой Демодуляции. Этот пример управляет задержкой порядка, получают правильную синхронизацию символа сигнала так, чтобы контуры символа правильно выровнялись, прежде чем демодуляция происходит.

Чтобы открыть эту модель, введите doc_nonlinear_digital_demod в командной строке MATLAB.

Эта модель включает схему модуляции CPFSK и импульсный формирующий фильтр. Для демодуляции, чтобы работать правильно, входной сигнал с блоком демодулятора CPFSK должен иметь правильное выравнивание. Различные блоки в этой модели вводят задержки обработки. Из-за этих задержек входной сигнал с блоком демодулятора CPFSK не находится в правильном выравнивании.

Оба Повышенная Передача Косинуса и Получает блоки Фильтра, вводят задержку. Задержка задана как:

где Ts представляет входной шаг расчета блока Raised Cosine Transmit Filter.

Входной шаг расчета блока Raised Cosine Transmit Filter равняется выходному шагу расчета блока Raised Cosine Receive Filter. Поэтому общая задержка при выходе Повышенного Косинуса Получает Фильтр:

или

как GroupDelay = 4

Блок демодулятора CPFSK получает этот задержанный сигнал, и затем это обрабатывает каждый набор 8 выборок на символ, чтобы вычислить 1 выходной символ. Необходимо гарантировать, что демодулятор CPFSK получает входные выборки в правильном наборе выборок. Для бинарного CPFSK с Modulation index 1/2 вход демодулятора должен выровняться вдоль четных чисел символов. Обратите внимание на то, что это требование применяется только к бинарному CPFSK с индексом модуляции 1/2. Другие схемы CPM с различными M-арными значениями и индексами модуляции имеют различные требования.

Чтобы гарантировать, что демодулятор CPFSK в этой модели получает правильный набор входных выборок с правильным выравниванием, введите задержку 8 выборок (в этом примере, ). Общая задержка во входе демодулятора CPFSK , который приравнивается к двум задержкам символа (2. T, где T является периодом символа).

В основанном на выборке режиме демодулятор CPFSK вводит задержку Traceback length + 1 выборка при его выходе. В этом примере Traceback length равняется 16. Поэтому общий Receiver delay в блоке вычисления Коэффициента ошибок равняется 17+2 или 19. Для получения дополнительной информации смотрите Задержки Цифровой Модуляции.