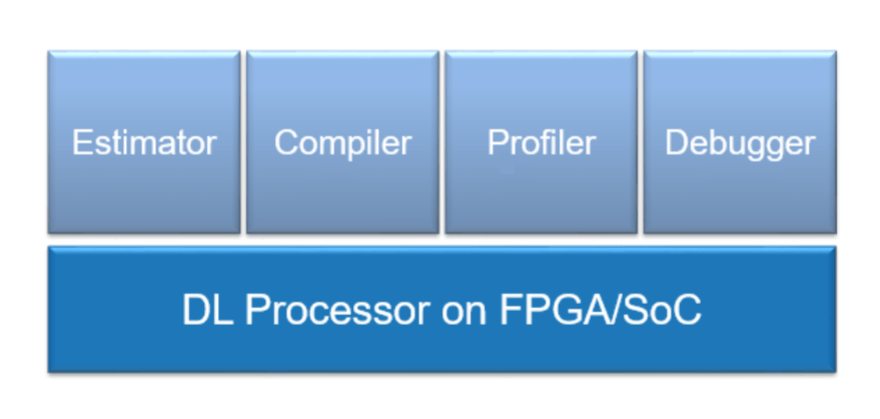

Фигура иллюстрирует решение MATLAB® для реализации глубокого обучения на FPGA.

Решение для глубокого обучения FPGA обеспечивает вплотную решение, которое позволяет вам оценивать, компилировать, профилировать и отлаживать свою пользовательскую предварительно обученную серийную сеть. Можно также сгенерировать пользовательский процессор IP глубокого обучения. Средство оценки используется для оценки эффективности среды глубокого обучения в терминах скорости. Компилятор преобразует предварительно обученную нейронную сеть для глубокого обучения для текущего приложения для развертывания его на намеченных целевых платах FPGA.

Чтобы узнать больше о процессоре IP глубокого обучения, смотрите Ядро IP Процессора Глубокого обучения.

FPGAs обеспечивают преимущества, такие как:

Высокая производительность

Гибкое взаимодействие через интерфейс

Параллелизм данных

Параллелизм модели

Конвейерно обработайте параллелизм

Чтобы запустить определенное Глубокое обучение на задачах FPGA, смотрите информацию, перечисленную в этой таблице.

| Задача | Рабочий процесс |

| Запустите предварительно обученную серийную сеть на своей целевой плате FPGA. | Моделируйте нейронные сети для глубокого обучения на рабочем процессе SoCs и FPGA |

| Получите эффективность своей предварительно обученной серийной сети для предварительно сконфигурированного процессора глубокого обучения. | Оцените эффективность нейронной сети для глубокого обучения |

| Настройте процессор глубокого обучения, чтобы соответствовать вашим ограничениям области. | Оцените использование ресурса для пользовательской настройки процессора |

| Сгенерируйте пользовательский процессор глубокого обучения для своего FPGA. | Сгенерируйте пользовательский поток битов |

| Узнайте о преимуществах квантования ваших предварительно обученных серийных сетей. | Квантование глубоких нейронных сетей |

| Сравните точность ваших квантованных предварительно обученных серийных сетей против вашего одного типа данных предварительно обучила серийную сеть. | Валидация |

| Запустите квантованную предварительно обученную серийную сеть на своей целевой плате FPGA. | Генерация кода и развертывание |