Вычислите величину и угол фазы комплексного сигнала – оптимизированный для генерации HDL-кода с помощью алгоритма CORDIC

Поддержка HDL DSP System Toolbox / Математические функции

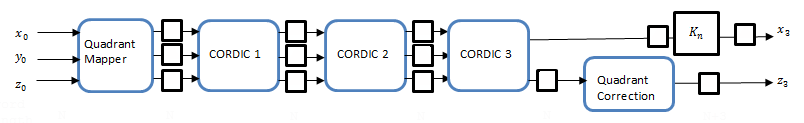

Блок Complex to Magnitude-Angle HDL Optimized вычисляет величину и угол фазы комплексного сигнала и обеспечивает благоприятные для оборудования управляющие сигналы. Чтобы достигнуть эффективной реализации HDL, блок использует конвейерный Координатный Компьютер Вращения (CORDIC) алгоритм.

Можно использовать этот блок, чтобы реализовать операции такой как atan2 в оборудовании.

dataIn — Комплексный входной сигналКомплексный входной сигнал в виде скаляра, вектор-столбец, представляющий выборки вовремя или вектор-строку, представляющий каналы. Используя векторный вход увеличивает пропускную способность при использовании большего количества аппаратных ресурсов. Блок реализует логику преобразования параллельно для каждого элемента вектора. Входной вектор может содержать до 64 элементов.

double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

validIn — Валидность входных данныхBoolean скалярКогда validIn является true, блок собирает данные от входного порта dataIn. Сигнал validIn применяется ко всем выборкам в векторном входном сигнале.

Типы данных: Boolean

Magnitude — Величина входного сигналаВеличина входного сигнала, возвращенного как скаляр, вектор-столбец, представляющий выборки вовремя или вектор-строку, представляющий каналы. Размерности этого порта совпадают с размерностями порта dataIn.

Чтобы включить этот порт, установите параметр Output format на Magnitude and Angle или Magnitude.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

Angle — Угол входного сигналаУгол входного сигнала, возвращенного как скаляр, вектор-столбец, представляющий выборки вовремя или вектор-строку, представляющий каналы. Размерности этого порта совпадают с размерностями порта dataIn.

Чтобы включить этот порт, установите параметр Output format на Magnitude and Angle или Angle.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

validOut — Валидность выходных данныхBoolean скалярБлок устанавливает validOut на true с каждыми допустимыми данными, возвращенными на Magnitude или выходных портах Angle. Сигнал validOut применяется ко всем выборкам в векторном выходном сигнале.

Типы данных: Boolean

Number of iterations source — Источник количества итерацийAuto (значение по умолчанию) | Property Чтобы определить номер итераций к входу WL − 1, выберите Auto. Если вход имеет тип данных double или single, номер итераций определяется к 16 по умолчанию.

Чтобы задать количество итераций при помощи параметра Number of iterations, выберите Property.

Number of iterations — Количество итераций CORDICКоличество итераций должно быть меньше чем или равно входу WL − 1. Задержка блока зависит от количества выполняемых итераций. Для получения информации о задержке смотрите Задержку.

Чтобы включить этот параметр, установите Number of iterations source на Property.

Output format — Формат выходного сигналаMagnitude and Angle (значение по умолчанию) | Magnitude | AngleИспользуйте этот параметр, чтобы задать, какие выходные порты включены.

Чтобы включить Magnitude и выходные порты Angle, выберите Magnitude and Angle (значение по умолчанию).

Чтобы включить выходной порт Magnitude и отключить выходной порт Angle, выберите Magnitude.

Чтобы включить выходной порт Angle и отключить выходной порт Magnitude, выберите Angle.

Angle format — Выведите угловой форматNormalized (значение по умолчанию) | RadiansВозвратить Angle выход как значение фиксированной точки, которое нормирует углы в области значений [–1,1], select Normalized. Для получения дополнительной информации смотрите Нормированный Угловой Формат.

Чтобы возвратить Angle выход как значение фиксированной точки в области значений [-π, π], выбирают Radians. При использовании этого блока, чтобы реализовать atan2 функция, установленная этот параметр на Radians.

Scale output — Scales выходon (значение по умолчанию) | offВыберите этот параметр, чтобы умножить Angle выход на инверсию фактора усиления CORDIC. Блок реализует этот фактор усиления использование архитектуры shift-and-add для множителя. Эта реализация может увеличить длину критического пути в вашем проекте.

Примечание

Если вы очищаете этот параметр и применяете усиление CORDIC в другом месте в вашем проекте, необходимо исключить термин π/4. Поскольку квадрант, сопоставляющий алгоритм, заменяет первую итерацию CORDIC путем отображения входных параметров на угловую область значений [0, π/4], начальное вращение не вносит термин усиления. Фактором усиления является продукт cos(atan(2-n)), для n от 1 до Number of iterations – 1.

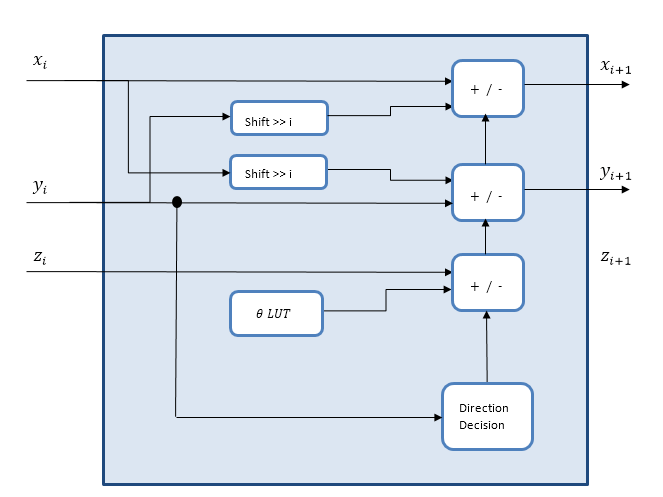

Алгоритм CORDIC является благоприятным для оборудования методом для выполнения тригонометрических функций. Это - итеративный алгоритм, который аппроксимирует решение путем схождения к идеальной точке. Блок использует CORDIC векторизация режима, чтобы итеративно вращать вход на вещественную ось.

Метод Givens для вращения комплексного числа x+iy углом θ следующие. Направление вращения, d, +1 для против часовой стрелки и −1 для по часовой стрелке.

Для аппаратной реализации факторизуйте becauseθ, чтобы оставить термин tanθ.

Чтобы вращать вектор на вещественную ось, выберите ряд вращений θn так, чтобы . Удалите термин becauseθ, таким образом, каждое итеративное вращение использует только сдвиг, и добавьте операции.

Объедините отсутствие условия becauseθ от каждой итерации в константу, и примените его с одним множителем к результату итогового вращения. Выходная величина является масштабированным окончательным значением x. Выходной угол, z, является суммой углов поворота.

Область сходимости для стандартного вращения CORDIC составляет ≈ ±99.7 °. Работать вокруг этого ограничения, прежде, чем сделать любое вращение, блок-диаграммы вход в [0, π/4] область значений с помощью этого алгоритма.

if abs(x) > abs(y) input_mapped = [abs(x), abs(y)]; else input_mapped = [abs(y), abs(x)]; end

Квадрантное отображение сохраняет аппаратные ресурсы и уменьшает задержку путем сокращения количества настроек канала связи CORDIC одной. Фактор усиления CORDIC, Kn, поэтому не включает n=0, или потому что (π/4), называют.

После того, как итерации CORDIC завершены, блок настраивает угол назад к его исходному местоположению. Сначала это настраивает угол правильной стороне π/4.

if abs(x) > abs(y) angle_unmapped = CORDIC_out; else angle_unmapped = (pi/2) - CORDIC_out; end

if (x < 0)

if (y < 0)

output_angle = - pi + angle_unmapped;

else

output_angle = pi - angle_unmapped;

else

if (y<0)

output_angle = -angle_unmapped;

Блок генерирует конвейерную архитектуру HDL, чтобы максимизировать пропускную способность. Каждая итерация CORDIC сделана в одной настройке канала связи. Множитель усиления, если включено, реализован с логикой канонической цифры со знаком (CSD).

Если вы используете векторный вход, этот блок реплицирует эту архитектуру параллельно для каждого элемента вектора.

Следующая таблица показывает Magnitude и Angle размер слова (WL) выхода для конкретного входного размера слова (WL). FL обозначает дробную длину, используемую в представлении фиксированной точки.

| Введите размер слова | Выведите размер слова величины |

|---|---|

| fixdt (0, WL, FL) | fixdt (0, WL + 2, FL) |

| fixdt (1, WL, FL) | fixdt (1, WL + 1, FL) |

| Введите размер слова | Выведите угловой размер слова | |

|---|---|---|

| fixdt ([], WL, FL) | Радианы | fixdt (1, WL + 3, WL) |

| 'normalized' | fixdt (1, WL + 3, WL+2) | |

Логика CORDIC при каждой настройке канала связи реализует одну итерацию. Для каждой настройки канала связи сдвиг и угловое вращение являются константами.

Когда вы устанавливаете Output format на Magnitude, блок не генерирует HDL-код для углового накопления и квадрантной логики коррекции.

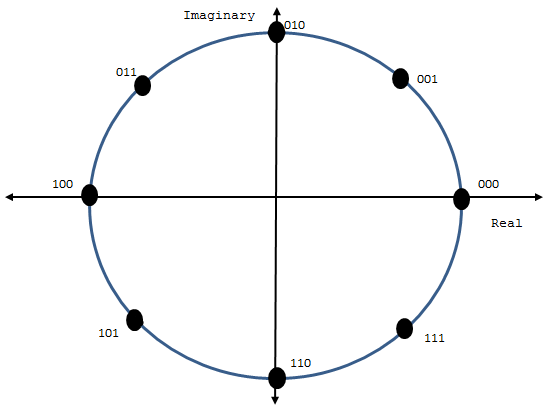

Этот формат нормирует угловые значения радиана фиксированной точки вокруг модульного круга. Это использование битов может быть более эффективным, чем использование области значений [0, 2π] радианы. Также этот нормированный угловой формат включает перенос угла в 0, или 2π без дополнительного обнаруживают и корректируют логику.

Например, представляя угол результатами на 3 бита в этих нормированных значениях.

Блок нормирует углы через [0, π/4] и сопоставляет их с правильным октантом в конце вычисления.

Когда допустимый вход применяется, допустимый выход происходит после Number of iterations + 4 цикла.

Когда вы устанавливаете параметр Number of iterations source на Property, блок сразу показывает задержку. Когда вы устанавливаете Number of iterations source на Auto, блок вычисляет задержку на основе типа данных входного порта и отображает задержку, когда вы обновляете модель.

Когда вы устанавливаете параметр Number of iterations source на Auto, количество итераций является входным WL − 1, и задержка является входом WL + 3. Если вход имеет тип данных double или single, количество итераций равняется 16, и задержка равняется 20.

Уровень был измерен для настройки по умолчанию с выходным отключенным масштабированием и fixdt(1,16,12) входной параметр. Когда сгенерированный HDL-код синтезируется в Xilinx® Virtex®-6 (XC6VLX240T-1FFG1156) FPGA, проект достигает тактовой частоты на 260 МГц. Это использует следующие ресурсы.

| Ресурс | Используемый номер |

|---|---|

| LUT | 882 |

| FFS | 792 |

Xilinx LogiCORE® DSP48 | 0 |

| Блокируйте RAM (16K) | 0 |

Эффективность синтезируемого HDL-кода варьируется в зависимости от вашей цели и опций синтеза. Когда вы используете векторный вход, использование ресурсов является во времена VectorSize скалярным использованием ресурсов.

Этот блок поддерживает генерацию кода C/C++ для акселератора Simulink® и быстрых режимов Accelerator и для генерации компонента DPI.

HDL Coder™ обеспечивает дополнительный параметр конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

Этот блок поддерживает генерацию кода для комплексных сигналов.

atan2 | dsp.HDLComplexToMagnitudeAngle | Complex to Magnitude-Angle (Simulink)

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.