Когда вы запускаете рабочий процесс элемента кода аппаратного программного обеспечения для платформ SoC, вы генерируете ядро IP HDL для алгоритма DUT и затем интегрируете ядро IP в исходный проект. Смотрите Рабочий процесс Элемента кода аппаратного программного обеспечения для Платформ SoC.

К быстрому прототипированию и тесту ядро IP HDL на целевом компьютере, можно сгенерировать скрипт программного интерфейса. Скрипт содержит порты DUT и информацию об отображении интерфейса, который использование HDL Coder™ создать драйверы AXI и получить доступ к ядру IP HDL.

Целевая платформа, такая как ZedBoard, где вы хотите развернуть свою модель программного интерфейса.

Последняя версия стороннего инструмента синтеза, такого как Xilinx® Vivado®. Смотрите Поддержку Языка HDL и Поддерживаемые Сторонние программы и Оборудование. На вашем сеансе MATLAB®, установленном путь к тому установленному инструменту синтеза при помощи hdlsetuptoolpath функция.

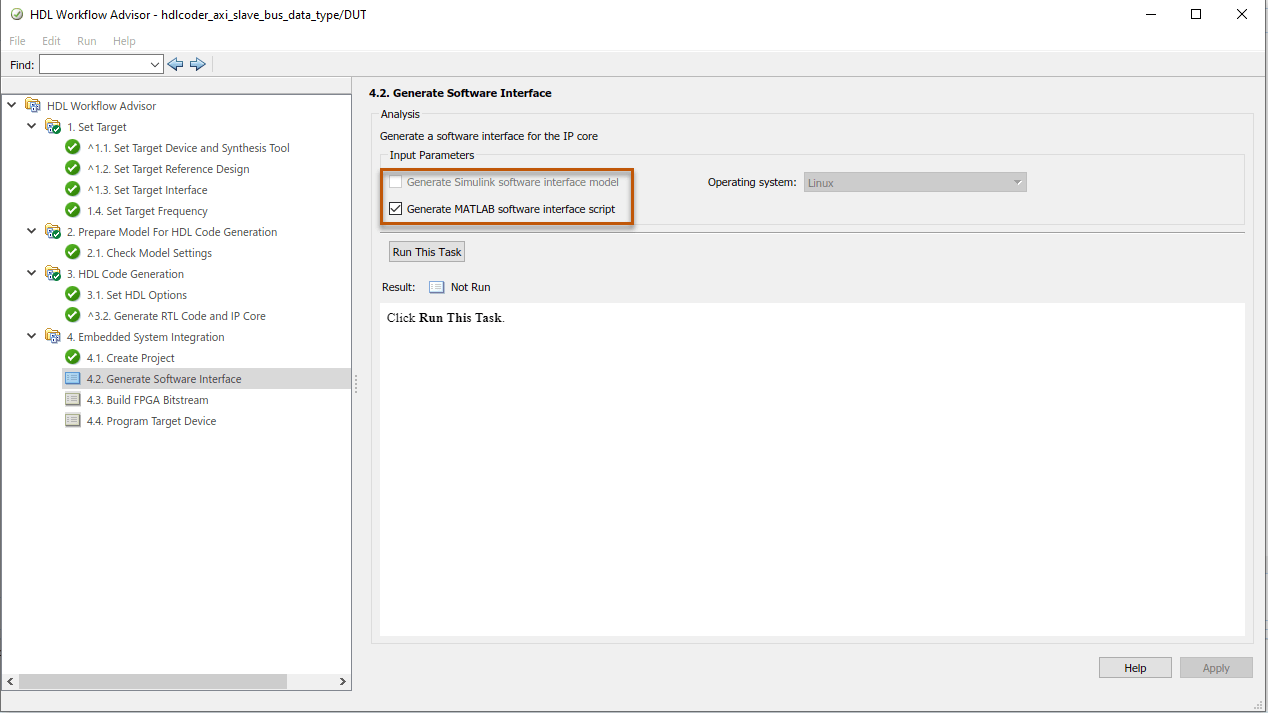

При выполнении рабочего процесса Генерации Ядра IP можно сгенерировать скрипт программного интерфейса и модель от HDL Workflow Advisor пользовательский интерфейс или в командной строке.

От пользовательского интерфейса, в Embedded System Integration> задача Generate Software Interface, устанавливают флажок Generate Software interface script.

Когда вы запускаете рабочий процесс Генерации Ядра IP к задаче Generate Software Interface и устанавливаете флажок Generate MATLAB software interface script, два файла MATLAB сгенерированы:

gs_modelName_setup.m, который является скриптом настройки, который добавляет ведомое устройство AXI4 и AXI4-потоковые интерфейсы. Скрипт также содержит объекты порта DUT, которые имеют имя порта, направление, тип данных и информацию об отображении интерфейса. Скрипт затем сопоставляет порты DUT с соответствующими интерфейсами.

gs_modelName_interface.m, то, которое создает целевой объект, инстанцирует скрипта настройки gs_modelName_setup.m, и затем подключения к целевому компьютеру. Скрипт затем отправляет чтение и команды записи к сгенерированному ядру IP HDL.

Если вы предназначаетесь для автономных плат FPGA, вы не можете сгенерировать модель программного интерфейса. Вместо этого можно сгенерировать скрипт программного интерфейса и протестировать ядро IP при помощи Ведущего драйвера AXI MATLAB.

В задаче Set Target Reference Design, набор Insert JTAG MATLAB as AXI Master к на. Запустите рабочий процесс к задаче Generate Software Interface.

В задаче Generate Software Interface установите флажок Generate Software interface script и запустите эту задачу.

В командной строке экспортируйте настройки HDL Workflow Advisor в скрипт, и затем используйте эти свойства с объектом Workflow Configuration. Этот скрипт задает выполнение задачи программного интерфейса путем генерации модели и скрипта. Если вы пропускаете задачу путем установки RunTaskGenerateSoftwareInterface на ложь, то модель и скрипт не сгенерированы. Смотрите Конфигурируют и Рабочий процесс Генерации Ядра IP Запуска со Скриптом.

% Export Workflow Configuration Script % ... %% Load the Model load_system('hdlcoder_led_blinking'); %% Model HDL Parameters % Set Model HDL parameters % ... hdlset_param('hdlcoder_led_blinking', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_led_blinking', 'Workflow', 'IP Core Generation'); % ... % Set Workflow tasks to run hWC.RunTaskGenerateSoftwareInterface = true; hWC.GenerateSoftwareInterfaceModel = true; hWC.GenerateSoftwareInterfaceScript = true; % ... %% Run the workflow hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC);

Для быстрого прототипирования и тестирования базовой функциональности IP HDL, используйте скрипт программного интерфейса. Скриптом является файл MATLAB, который сгенерирован на основе исходного проекта и табличных настроек интерфейса целевой платформы. Это содержит команды, которые позволяют вам соединиться с целевым компьютером, и записать в или читать из сгенерированного ядра IP из MATLAB. Для автономных плат FPGA используйте скрипт интерфейса сгенерированного программного обеспечения, чтобы проверить базовую функциональность IP HDL при помощи Ведущего устройства AXI MATLAB.

Скрипт программного интерфейса имеет то же имя как ваша исходная модель с префиксным gs_ и постфиксный _interface. Скрипт инстанцирует функции настройки, которая сгенерирована, когда вы включаете генерацию скрипта программного интерфейса. Например, этот код показывает функцию настройки, сгенерированную для модели hdlcoder_sfir_fixed_stream.slx, с исходным проектом и целевой платформой соединяют интерфейсом с табличными ранее заданными настройками. Функция настройки содержит команды для ведомого устройства AXI4 и AXI4-потоковых интерфейсов, что использование HDL Coder, чтобы управлять портами DUT в сгенерированном ядре IP HDL, которые сопоставлены с соответствующими интерфейсами.

function gs_hdlcoder_sfir_fixed_stream_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 09:13:05 on 10/07/2020. % This function was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Run this function on an "fpga" object to configure it with % the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4-Lite addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000); hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100"); hPort_h_in2 = hdlcoder.DUTPort("h_in2", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x104"); hPort_h_in3 = hdlcoder.DUTPort("h_in3", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x108"); hPort_h_in4 = hdlcoder.DUTPort("h_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x10C"); mapPort(hFPGA, [hPort_h_in1, hPort_h_in2, hPort_h_in3, hPort_h_in4]); %% AXI4-Stream addAXI4StreamInterface(hFPGA, ... "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "WriteFrameLength", 1024, ... "ReadEnable", true, ... "ReadFrameLength", 1024); hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]); end

Это - функция настройки в качестве примера для модели с шиной, сопоставленной с ведомым интерфейсом AXI4. Как показано в скрипте, элементы шины представлены как подпорты hdlcoder.DUTPort объекты.

function gs_AXI4SlaveMultipleBus_setup(hFPGA) %-------------------------------------------------------------------------- % Software Interface Script Setup % % Generated with MATLAB 9.10 (R2021a) at 16:20:32 on 16/11/2020. % This function was created for the IP Core generated from design 'AXI4SlaveMultipleBus'. % % Run this function on an "fpga" object to configure it with the same interfaces as the generated IP core. %-------------------------------------------------------------------------- %% AXI4 addAXI4SlaveInterface(hFPGA, ... "InterfaceID", "AXI4", ... "BaseAddress", 0x400D0000, ... "AddressRange", 0x10000); hPort_bus1_in_scalar_in1 = hdlcoder.DUTPort("scalar_in1", ... "Direction", "IN", ... "DataType", numerictype('single'), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x100"); hPort_bus1_in_scalar_in2 = hdlcoder.DUTPort("scalar_in2", ... "Direction", "IN", ... "DataType", numerictype(1,8,0), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x104"); hPort_bus1_in_scalar_in3 = hdlcoder.DUTPort("scalar_in3", ... "Direction", "IN", ... "DataType", numerictype(1,32,0), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x108"); hPort_bus1_in_scalar_in4 = hdlcoder.DUTPort("scalar_in4", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x10C"); hPort_bus1_in_vector_in = hdlcoder.DUTPort("vector_in", ... "Direction", "IN", ... "DataType", numerictype(0,32,0), ... "Dimension", [1 2], ... "IOInterface", "AXI4", ... "IOInterfaceMapping", "0x110"); hPort_bus1_in = hdlcoder.DUTPort("bus1_in", ... "Direction", "IN", ... "DataType", "Bus", ... "Dimension", [1 1], ... "IOInterface", "AXI4", ... "SubPorts", [hPort_bus1_in_scalar_in1, hPort_bus1_in_scalar_in2, hPort_bus1_in_scalar_in3, hPort_bus1_in_scalar_in4, hPort_bus1_in_vector_in]);

Скрипт программного интерфейса инстанцирует этой функции настройки, чтобы соединиться с целью и отправить команды записи или чтение. Можно не прокомментировать и отправить значимые данные при помощи входных параметров к DUT в исходной модели. После взаимодействия через интерфейс с оборудованием скрипт отключается от аппаратного ресурса, сопоставленного с fpga объект.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2020b) at 09:13:10 on 10/07/2020. % This script was created for the IP Core generated from design 'hdlcoder_sfir_fixed_stream'. % % Use this script to access DUT ports in the design mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % % To write to input ports, use the "writePort" command and specify port name and input data. % The input data will be cast to the DUT port's data type before writing. % % To read from output ports, use the "readPort" command and specify the port name. % The output data will be returned with the same data type as the DUT port. % % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures "fpga" object with same interfaces as the generated IP core gs_hdlcoder_sfir_fixed_stream_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4-Lite writePort(hFPGA, "h_in1", zeros([1 1])); writePort(hFPGA, "h_in2", zeros([1 1])); writePort(hFPGA, "h_in3", zeros([1 1])); writePort(hFPGA, "h_in4", zeros([1 1])); %% AXI4-Stream writePort(hFPGA, "x_in_data", zeros([1 1024])); data_y_out_data = readPort(hFPGA, "y_out_data"); %% Release hardware resources release(hFPGA)

См. прототипный проект FPGA на оборудовании с живыми данными при помощи Команд MATLAB

Это - скрипт программного интерфейса в качестве примера, чтобы читать и записать данные для моделей, которые имеют типы данных шины, сопоставленные с ведомыми интерфейсами AXI4.

Чтобы записать во вход шины, вы можете также:

Запишите в отдельные подпорты путем определения полного имени подпорта, такие как bus1_in.scalar_in1.

Запишите в целую шину путем определения имени верхнего порта, такого как bus1_in. Передайте данные, которые будут записаны как struct, зарегистрированные имена которого совпадают с именами подпорта. Не все имена подпорта должны быть частью struct. Подпорты без соответствующих полей struct пропущены при записи в порт.

Чтобы читать из входа шины, вы можете также:

Считайте отдельный подпорт путем определения полного имени подпорта, такого как bus1_out.scalar.in1.

Считайте целый вход шины путем определения имени верхнего порта, такого как bus1_out.

%-------------------------------------------------------------------------- % Software Interface Script % % Generated with MATLAB 9.10 (R2021a) at 16:20:33 on 16/11/2020. % This script was created for the IP Core generated from design 'AXI4SlaveMultipleBus'. % % Use this script to access DUT ports in the design that were mapped to compatible IP core interfaces. % You can write to input ports in the design and read from output ports directly from MATLAB. % To write to input ports, use the "writePort" command and specify the port name and input data. The input data will be cast to the DUT port's data type before writing. % To read from output ports, use the "readPort" command and specify the port name. The output data will be returned with the same data type as the DUT port. % Use the "release" command to release MATLAB's control of the hardware resources. %-------------------------------------------------------------------------- %% Create fpga object hFPGA = fpga("Xilinx"); %% Setup fpga object % This function configures the "fpga" object with the same interfaces as the generated IP core gs_AXI4SlaveMultipleBus_setup(hFPGA); %% Write/read DUT ports % Uncomment the following lines to write/read DUT ports in the generated IP Core. % Update the example data in the write commands with meaningful data to write to the DUT. %% AXI4 % There are two ways to write a DUT bus ports % (1). Prepare a struct value and write it to the whole bus port. writePort(hFPGA, "bus1_in", struct()); % (2). Prepare a value for each member of the bus and write it individually. writePort(hFPGA, "bus1_in.scalar_in1", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in2", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in3", zeros([1 1])); writePort(hFPGA, "bus1_in.scalar_in4", zeros([1 1])); writePort(hFPGA, "bus1_in.vector_in", zeros([1 2]));