Быстрое прототипирование ядро IP HDL путем взаимодействия через интерфейс с требуемой платой по Ethernet или JTAG. Используйте соединение Ethernet для плат, которые имеют процессор ARM. Используйте связь JTAG для плат, которые не имеют процессора ARM.

Целевая платформа, такая как ZedBoard™, где вы развертываете свою модель программного интерфейса

Последняя версия стороннего инструмента синтеза, такого как Xilinx® Vivado®. Смотрите Поддержку Языка HDL и Поддерживаемые Сторонние программы и Оборудование. На вашем сеансе MATLAB®, установленном путь к тому установленному инструменту синтеза при помощи hdlsetuptoolpath функция.

Чтобы использовать основанную на Ethernet связь с вашими платами целевого компьютера, которые имеют встроенный процессор ARM, можно или сгенерировать скрипт программного интерфейса или создать скрипт заказного программного обеспечения. Перед подготовкой основанного на Ethernet интерфейса, настроенного SD-карта платы с изображением встроенного программного обеспечения MathWorks®. Настраивать микропрограммное изображение для вашей требуемой платы:

Для связанных с Intel® плат смотрите Ведомого Setup SD-карты (Пакет Поддержки HDL Coder для Устройств Intel SoC)

Для связанных с Xilinx плат смотрите Ведомого Setup SD-карты (Пакет Поддержки HDL Coder для Платформы Xilinx Zynq).

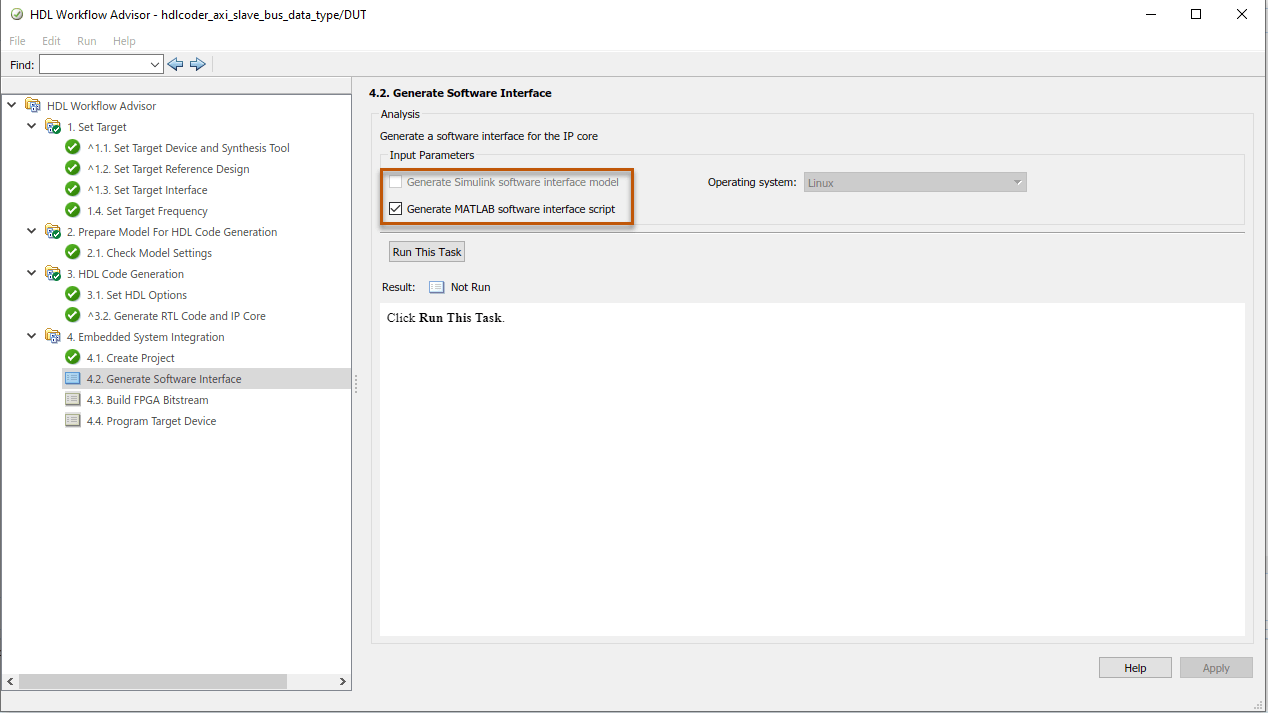

Когда вы запускаете задачу Generate Software Interface и устанавливаете флажок Generate MATLAB software interface script.

Сгенерированные файлы MATLAB:

gs_modelName_setup.m, который является скриптом настройки, который добавляет ведомое устройство AXI4 и AXI4-потоковые интерфейсы. Скрипт также содержит объекты порта DUT, которые имеют имя порта, направление, тип данных и информацию об отображении интерфейса. Скрипт затем сопоставляет порты DUT с соответствующими интерфейсами.

gs_modelName_interface.m, то, которое создает целевой объект, инстанцирует скрипта настройки gs_modelName_setup.m, и затем подключения к целевому компьютеру. Скрипт затем отправляет чтение и команды записи к сгенерированному ядру IP HDL.

Смотрите генерируют скрипт программного интерфейса, чтобы зондировать и ядро IP HDL быстрого прототипирования.

Для быстрого прототипирования настройте скрипт программного интерфейса или создайте свой собственный скрипт на основе того, как вы изменяете свой первоначальный проект. Настройте скрипт, чтобы задать:

Целевой объект для различного поставщика FPGA.

Дополнительные интерфейсы или конфигурируют существующие интерфейсы на основе модификаций к вашему первоначальному проекту. HDL Coder™ использует эту информацию, чтобы создать драйверы IIO, чтобы получить доступ к ядру IP HDL.

Дополнительные объекты порта DUT или удаляют существующие объекты на основе того, как вы изменяете свой проект, и затем изменяете информацию об отображении соответственно.

Входные данные, чтобы записать в порты DUT и выходные данные, чтобы читать из портов.

Можно настроить скрипт сгенерированного программного обеспечения или создать собственный скрипт программного интерфейса. Создать скрипт заказного программного обеспечения:

Создайте fpga объект для целевого устройства и хранилища в hFPGA.

hFPGA = fpga("Xilinx")

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [0×0 fpgaio.interface.InterfaceBase]

Использовать цель Intel:

hFPGA = fpga("Intel")

hFPGA =

fpga with properties:

Vendor: "Intel"

Interfaces: [0×0 fpgaio.interface.InterfaceBase]

Сконфигурируйте интерфейсы AXI, чтобы сопоставить порты DUT в сгенерированном ядре IP HDL. Можно добавить ведомое устройство AXI4 и AXI4-потоковые интерфейсы. Чтобы добавить ведомые интерфейсы AXI4, используйте addAXI4SlaveInterface функция.

addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDeviceName", "mwipcore0:mmwr0", ... "ReadDeviceName", "mwipcore0:mmrd0");

Чтобы добавить AXI4-потоковые интерфейсы, используйте addAXI4StreamInterface функция.

addAXI4StreamInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "ReadEnable", true, ... "WriteFrameLength", 1024, ... "ReadFrameLength", 1024, ... ... % Driver properties "WriteDeviceName", "mwipcore0:mm2s0", ... "ReadDeviceName", "mwipcore0:s2mm0");

Информация отображения интерфейса, которую вы указали, сохранена как свойство на fpga объект, hFPGA.

hFPGA

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [1×2 fpgaio.interface.InterfaceBase]Для автономных плат FPGA, которые не имеют встроенного процессора ARM, можно создать объект, и затем использовать aximaster объект. Затем используйте этот объект в качестве драйвера для addAXI4SlaveInterface функция. aximaster объект требует пакета поддержки HDL Verifier™ для платы FPGA Intel или Xilinx.

% Create an "aximaster" object hAXIMDriver = aximaster("Xilinx"); % Pass it into the addInterface command addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xB0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDriver", hAXIMDriver, ... "ReadDriver", hAXIMDriver, ... "DriverAddressMode", "Full");

Укажите информацию о портах DUT в сгенерированном ядре IP HDL как массив объекта порта при помощи hdlcoder.DUTPort объект. Объект представляет порты вашего DUT на целевом компьютере.

hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100")

hPort_h_in1 =

DUTPort with properties:

Name: "h_in1"

Direction: IN

DataType: [1×1 embedded.numerictype]

Dimension: [1 1]

IOInterface: "AXI4-Lite"

IOInterfaceMapping: "0x100"Чтобы записать в или читать из портов DUT в сгенерированном ядре IP HDL, сопоставьте порты с интерфейсом AXI при помощи mapPort функция. После того, как вы сопоставите порты с интерфейсами, эта информация сохранена на fpga возразите как Interfaces свойство.

mapPort(hFPGA, hPort_h_in1); hFPGA.Interfaces

ans =

AXI4Slave with properties:

InterfaceID: "AXI4-Lite"

BaseAddress: "0xA0000000"

AddressRange: "0x10000"

WriteDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIORead]

InputPorts: "h_in1"

OutputPorts: [0×0 string]

Можно также указать эту информацию для портов, сопоставленных с AXI4-потоковыми интерфейсами.

hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream");

Чтобы записать в или читать из портов DUT в сгенерированном ядре IP HDL, сопоставьте порты с интерфейсом AXI при помощи mapPort функция.

mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]);

fpga возразите как Interfaces свойство.hFPGA

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [1×2 fpgaio.interface.InterfaceBase]hFPGA.Interfaces

ans =

AXI4Slave with properties:

InterfaceID: "AXI4-Lite"

BaseAddress: "0xA0000000"

AddressRange: "0x10000"

WriteDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIORead]

InputPorts: "h_in1"

OutputPorts: [0×0 string]

AXI4Stream with properties:

InterfaceID: "AXI4-Stream"

WriteEnable: 1

ReadEnable: 1

WriteFrameLength: 1024

ReadFrameLength: 1024

WriteDriver: [1×1 fpgaio.driver.AXIStreamIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIStreamIIORead]

InputPorts: "x_in_data"

OutputPorts: "y_out_data"

Чтобы протестировать базовую функциональность IP HDL, используйте readPort и writePort функции, чтобы записать данные к или считать данные из этих портов.

writePort(hFPGA, "h_in1", 5); writePort(hFPGA, "x_in", sin(linspace(0, 2*pi, 1024))); data = readPort(hFPGA, "y_out");

После того, как вы протестировали ядро IP HDL, можно выпустить аппаратный ресурс, сопоставленный с fpga объект при помощи release функция.

release(hFPGA)

Для примера при создании пользовательского интерфейсного скрипта и прототипировании вашего проекта на целевой плате FPGA по соединению Ethernet, см. Прототипный Проект FPGA на Оборудовании с Живыми Данными при помощи Команд MATLAB.

Для автономных плат FPGA, которые не имеют встроенного процессора ARM, можно ввести MATLAB JTAG как Ведущий IP AXI в исходный проект. Создайте скрипт, который использует aximaster возразите что подключения к IP по физическому кабелю JTAG. Этот скрипт позволяет чтению и командам записи назнатить ячейки памяти ведомым устройством из командной строки MATLAB.

Использовать MATLAB в качестве Ведущего устройства AXI:

Установите пакеты аппаратной поддержки HDL Verifier.

Не предназначайтесь для автономных плат, которые не имеют hRD.AXI4SlaveInterface функциональность или платы, которые основаны на Xilinx ISE.

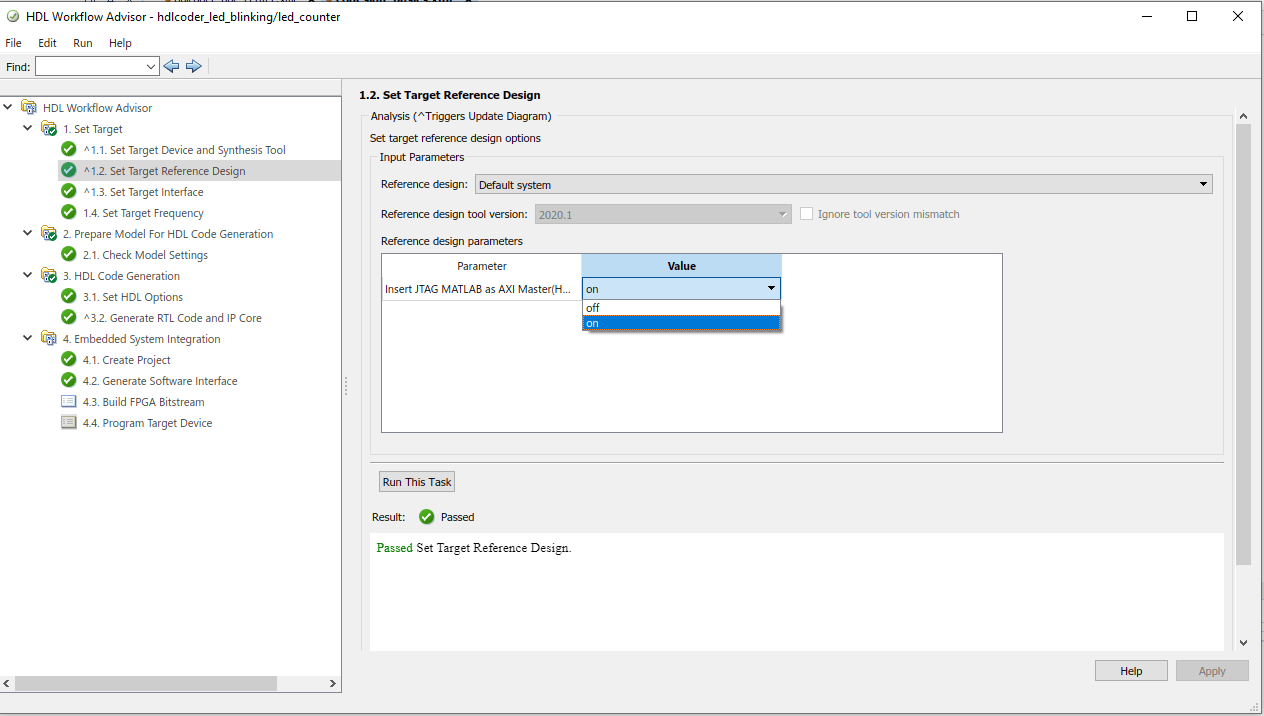

Когда вы запускаете рабочий процесс Генерации Ядра IP, в Set Target> задача Set Target Reference Design, выбираете Default system for Reference Design и устанавливаете Insert JTAG MATLAB as AXI Master на на.

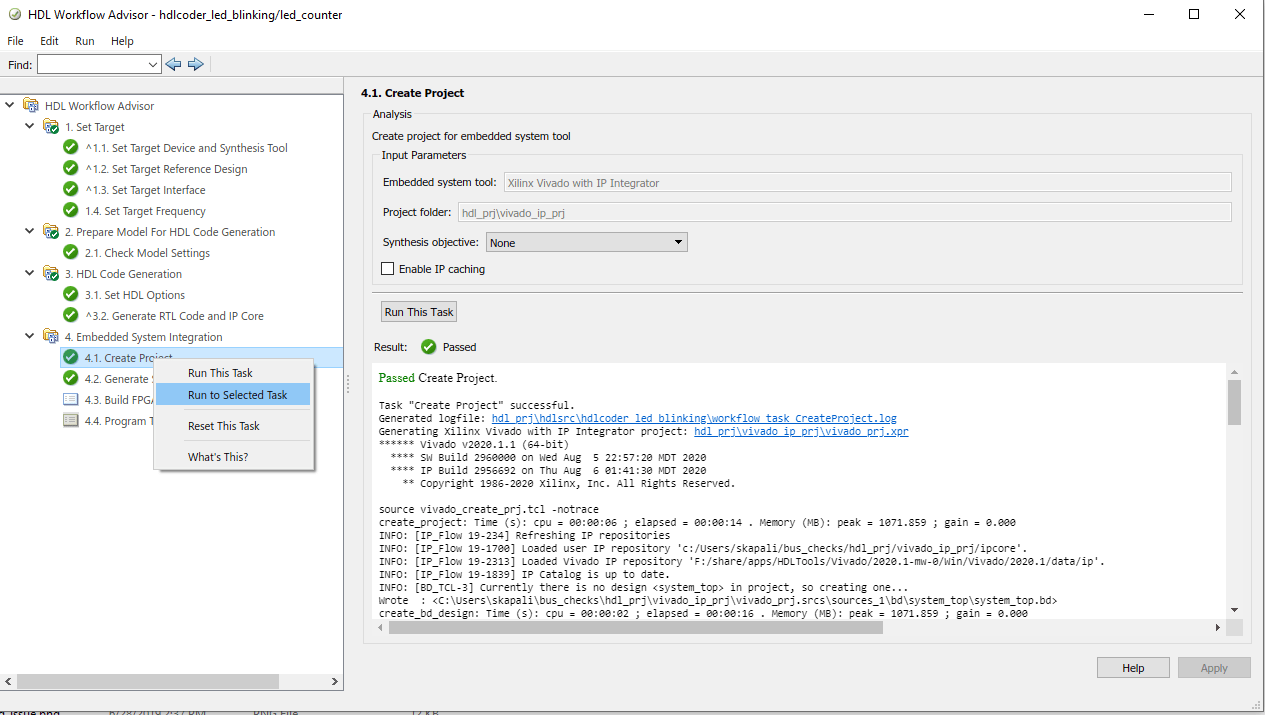

Чтобы сгенерировать Ядро IP и создать проект с Основным IP AXI, щелкните правой кнопкой по задаче Create Project и выберите Run to Selected Task.

Можно теперь взаимодействовать с целевой платой FPGA при помощи MATLAB JTAG как Ведущая функция AXI. Создайте объект при помощи aximaster объект. Используйте созданный объект в качестве драйвера для addAXI4SlaveInterface функция.

% Create an "aximaster" object hAXIMDriver = aximaster("Xilinx"); % Pass it into the addInterface command addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xB0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDriver", hAXIMDriver, ... "ReadDriver", hAXIMDriver, ... "DriverAddressMode", "Full");

Для примера о том, как взаимодействовать через интерфейс с требуемой платой по JTAG, смотрите Используя MATLAB JTAG, когда Ведущее устройство AXI, чтобы управлять HDL Coder сгенерировало Ядро IP.