Синхронизируйте делитель, который делит частоту входного сигнала дробным номером

Mixed-Signal Blockset / PLL / Базовые блоки

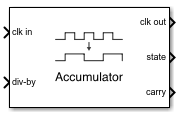

Блок Fractional Clock Divider with Accumulator делит частоту входного сигнала настраиваемым дробным значением (N.FF). Когда по сравнению с блоком Single Modulus Prescaler, блок Fractional Clock Divider with Accumulator помогает достигнуть узкого канала, располагающего с интервалами, который может быть меньше ссылочной частоты замкнутого цикла фазы (PLL) система.

[1] Лучше всего, Роланд Э. Замкнутый цикл фазы. Нью-Йорк, Нью-Йорк: Tata McGraw-Hill Companies Inc., 2003.

Dual Modulus Prescaler | Fractional Clock Divider with DSM | PFD | Single Modulus Prescaler | VCO