Модулятор Сигмы Delta основывал дробный делитель часов

Mixed-Signal Blockset / PLL / Базовые блоки

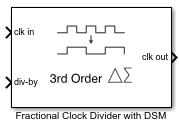

Используя сигму дельты (Δ-Σ) метод модуляции, Fractional Clock Divider with DSM уменьшает первичные дробные шпоры путем распространения области значений, в которой варьируется значение div-by. Этот блок позволяет модуляцию сигмы дельты до 4-го порядка.

clk in — Введите тактовую частотуВведите тактовую частоту, которая должна быть разделена в виде скаляра. В замкнутом цикле фазы (PLL) система порт clk in соединяется с выходом блока VCO.

Типы данных: double

div-by — Отношение выхода, чтобы ввести тактовую частотуОтношение выхода, чтобы ввести тактовую частоту в виде дробного скаляра. Значение в порте div-by, N.FF, разделено в две части: целая часть (N) и дробная часть (.FF).

Для модулятора сигмы дельты th-порядка n значение в порте div-by достигается различным N между 2n различные целочисленные значения.

Примечание

Для n th модулятор сигмы дельты порядка, используйте значение ≥ 2n в порте div-by.

Типы данных: double

clk out — Выведите тактовую частотуВыведите тактовую частоту в виде скаляра. В системе PLL порт clk out соединяется с входным портом обратной связи блока PFD. Выход в порте clk out является квадратной последовательностью импульсов 1-вольтовой амплитуды.

Типы данных: double

Delta Sigma Modulator order — Порядок модулятора сигмы Delta3rd order (значение по умолчанию) | 1st order | 2nd order | 4th orderПорядок модулятора сигмы дельты.

Для th-порядка n модулятора сигмы дельты значение в порте div-by достигается путем варьирования значения счетчика N между 2n различные значения. Порядок модулятора задает область значений значений, которыми сигнал в порте clk in будет разделен, обеспечивая эффект деления, похожий на значение N.FF в порте div-by.

Использование get_param(gcb,'dsm') просмотреть текущий Delta Sigma Modulator order.

Использование set_param(gcb,'dsm',value) установить Delta Sigma Modulator order на определенное значение.

Enable increased buffer size — Включите увеличенный buffer sizeВыберите, чтобы включить увеличенный buffer size в процессе моделирования. Это увеличивает buffer size Logic Decision в блоке Fractional Clock Divider with DSM. По умолчанию эта опция является невыбранной.

Buffer size — Количество выборок буферизации ввода, доступной в процессе моделированияКоличество выборок буферизации ввода, доступной в процессе моделирования в виде положительного целочисленного скаляра. Это устанавливает buffer size Logic Decision в блоке Fractional Clock Divider with DSM.

Выбор различного решателя симуляции или выборка стратегий могут измениться, количество входных выборок должно было произвести точную выходную выборку. Установите Buffer size на достаточно большое значение так, чтобы входной буфер содержал все входные требуемые выборки.

Этот параметр только доступен, когда опция Enable increased buffer size выбрана в диалоговом окне Block Parameters.

Использование get_param(gcb,'NBuffer') просмотреть текущее значение Buffer size.

Использование set_param(gcb,'NBuffer',value) установить Buffer size на определенное значение.

Блок подсистемы Fractional Clock Divider with DSM состоит из четырех модуляторов сигмы дельты порядков один - четыре инкапсулировавших в Селекторной различной подсистеме DSM. Выход селектора DSM управляет блоком Single Modulus Prescaler. Учитывая Delta Sigma Modulator order, активируется соответствующий модулятор сигмы дельты.

Порядок модулятора задает область значений, в которой варьируется значение счетчика N. Для модулятора сигмы дельты th-порядка n N варьируется по 2n различные значения. Это изменение достигается путем интеграции изменений в дробной части (.FF) от предыдущего цикла и квантования дифференциальных изменений.

Общая форма передаточной функции для модулятора сигмы дельты n-го порядка:

где

Y(z) = Выход модулятора

X(z) = Вход модулятор

E(z) = ошибка Квантования

E(z) вычисляется путем вычитания значения входа X(z) в существующем цикле от его значения в предыдущем цикле. Другими словами, E(z) является формой цифровой фильтрации highpass.

Модуляторы высшего порядка уменьшают первичные дробные шпоры путем чередования N в большей области значений целочисленных значений. В результате дробные шпоры продвинуты к более высоким частотам в спектре частоты и могут быть отфильтрованы эффективнее контурным фильтром в системе PLL.

Например, если модулятор сигмы дельты третьего порядка активируется, N варьируется более чем 8 различных значений, которые могут расположиться от (N-3) к (N +4).

Последовательность модулятора сигмы Delta

| Порядок модулятора | Область значений | Последовательность DSM |

| 1-й | 0, 1 | N, N +1 |

| 2-й | -1, 0, 1, 2 | N-1, N, N +1, N +2 |

| 3-й | -3, -2, -1, 0, 1, 2, 3, 4 | N-3, N-2, …, N +4 |

| 4-й | -7, -6, …, 7, 8 | N-7, N-6, …, N +8 |

[1] Миллер, B. и Конли, R.J., Модулятор Кратного Дробный Делитель. Транзакции IEEE на Инструментировании и Измерении, издании 40, № 3, 1991, стр 578-583.

Dual Modulus Prescaler | Fractional Clock Divider with Accumulator | PFD | Single Modulus Prescaler | VCO

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.